d触发器是干什么的_d触发器有什么用

模拟技术

描述

d触发器是干什么的

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种。

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态取决于CP的脉冲上升沿到来之前D端的状态,即次态=D。因此,它具有置0、置1两种功能。由于在

CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

D触发器原理学习指导:

通过本知识点的学习,了解基本D触发器的工作原理,掌握用真值表、状态转换真值表、特性方程和状态转换图描述D触发器的逻辑功能及D触发器的应用。

D触发器逻辑功能

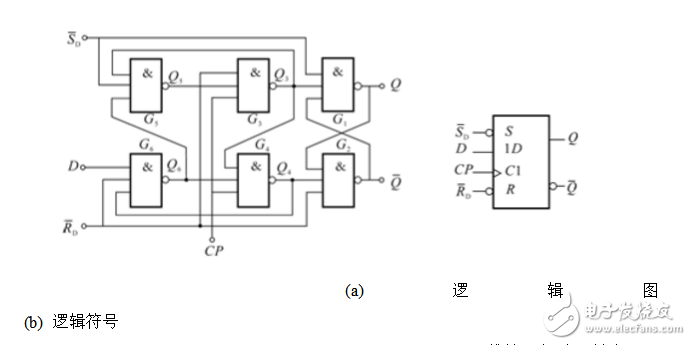

维持-阻塞D触发器是在时钟脉冲CP上升沿触发的一种,图4-7(a)是其逻辑电路,图4-7(b)是逻辑符号,逻辑符号中D的小矩形代表“与”门,为了扩展触发器的功能,往往制作多个D输入端,D=D1D2…。

d触发器有什么用

主从JK触发器是在CP脉冲高电平期间接收信号,如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器产生与逻辑功能表不符合的错误状态。边沿触发器的电路结构可使触发器在CP脉冲有效触发沿到来前一瞬间接收信号,在有效触发沿到来后产生状态转换,这种电路结构的触发器大大提高了抗干扰能力和电路工作的可靠性。下面以维持阻塞D触发器为例介绍边沿触发器的工作原理。

维持阻塞式边沿D触发器的逻辑图和逻辑符号如图9-7所示。该触发器由六个与非门组成,其中G1、G2构成基本RS触发器,G3、G4组成时钟控制电路,G5、G6组成数据输入电路。和

分别是直接置0和直接置1端,有效电平为低电平。分析工作原理时,设和均为高电平,不影响电路的工作。电路工作过程如下。

③ 触发器翻转后,在CP=1时输入信号被封锁。G3和G4打开后,它们的输出和的

状态是互补的,即必定有一个是0,若

为0,则经G4输出至G6输入的反馈线将G6封锁,

即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。G3为0时,将G4和G5封锁,D端通往基本RS触发器的路径也被封锁;G3输出端至G5反馈线起到使触发器维持在1状态的作用,称作置1维持线;G3输出端至G4输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。因此,该触发器称为维持阻塞触发器。

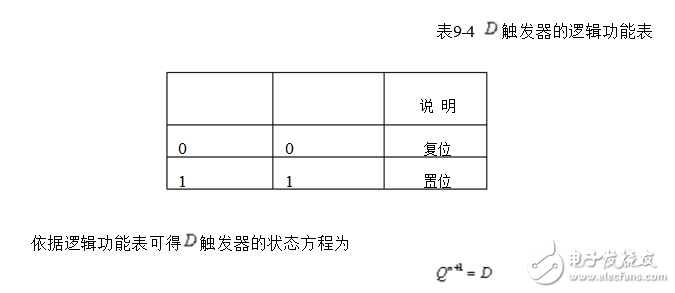

由上述分析可知,维持阻塞D触发器在CP脉冲的上升沿产生状态变化,触发器的次态取决于CP脉冲上升沿前D端的信号,而在上升沿后,输入D端的信号变化对触发器的输出状态没有影响。如在CP脉冲的上升沿到来前=0,则在CP脉冲的上升沿到来后,触发器置0;如在CP脉冲的上升沿到来前=1,则在CP脉冲的上升沿到来后触发器置1。维持阻塞触发器的逻辑功能表如表9-4所示。

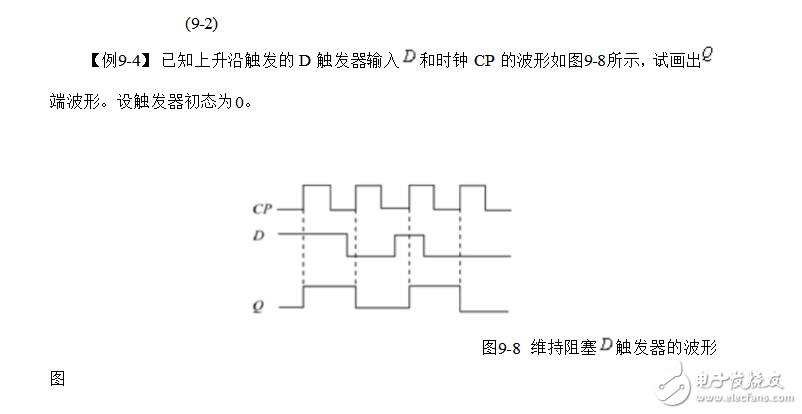

解:该D触发器是上升沿触发,即在CP的上升沿过后,触发器的状态等于CP脉冲上升沿前D的状态。所以第一个CP过后,=1,第二个CP过后,= 0,…,波形如图9-8所示。 触发器在CP上升沿前接受输入信号,上升沿触发翻转,即触发器的输出状态变化比输入端的状态变化延迟,这就是触发器的由来

-

57.2 主从D触发器 (3)#触发器电路设计快学 2022-08-01

-

触发器实验2009-03-20 0

-

如何用JK触发器构成D触发器 电路图2011-11-14 0

-

D触发器Verilog描述2012-02-22 0

-

触发器的分类2012-06-18 0

-

J-K触发器用D触发器代替 求教2014-01-09 0

-

labview新手 请教D触发器设计2014-12-24 0

-

关于D触发器的问题2019-01-16 0

-

请问电平触发的D触发器型号有哪些?2019-02-28 0

-

什么是触发器 触发器的工作原理及作用2019-12-25 0

-

图文并茂:D型触发器电路设计教程2021-02-03 0

-

jk触发器设计d触发器2021-07-22 0

-

常见的触发器包括哪些2022-01-20 0

-

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?2022-01-25 0

-

JK触发器和D触发器所使用的时钟脉冲能否用逻辑电平开关提供?2023-05-10 0

全部0条评论

快来发表一下你的评论吧 !