时序分析基本概念——STA概述简析

描述

在芯片设计中,我们常用PPA(Power, Performance, Area)来衡量一块芯片的指标。Performace直接取决于Timing参数。由此可见,时序设计在后端设计中占有举足轻重的地位。那今天我们就来介绍下,时序分析中的最重要概念——STA。

我们现在生活中其实存在着不少时序问题,比如以下两个例子:

•我打电话给张三,李四却接了电话

这就代表着数据传输过程中出现问题,导致芯片不工作

•我想要一辆法拉利,你却给我的是装着QQ引擎的法拉利

这就代表着芯片没有工作在正常的频率之下

同样在芯片设计过程中,存在着很多时序的违例。这就需要我们在设计中去验证时序的正确与否。

通常,我们有以下两种验证方法:

(1) 动态时序分析(Dynamic timing simulation)

(2) 静态时序分析(Static Timing Analysis, 简称STA)

动态时序分析,主要是通过输入向量作为激励,来验证整个设计的时序功能。动态时序分析的精确与否取决于输入激励的覆盖率,它最大的缺点就是速度非常慢,通常百万门的设计想全部覆盖测试的话,时间就是按月来计算了。

而静态时序分析呢?

Static timing Analysis is a method for determining if a circuit meets timing constraints without having to simulate clock cycles.

翻成中文的话: 套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

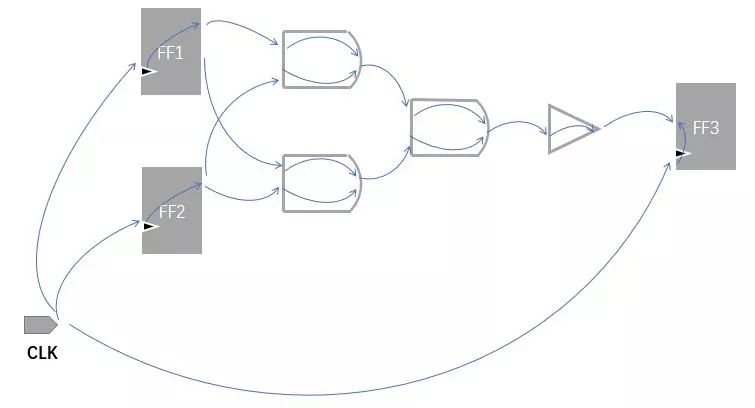

和动态时序分析相比,它不需要输入激励,因此速度会很快,并且它是Path Based分析,采用穷举型逻辑,如下图所示,理论上能分析到所有同步逻辑是否违反约束。

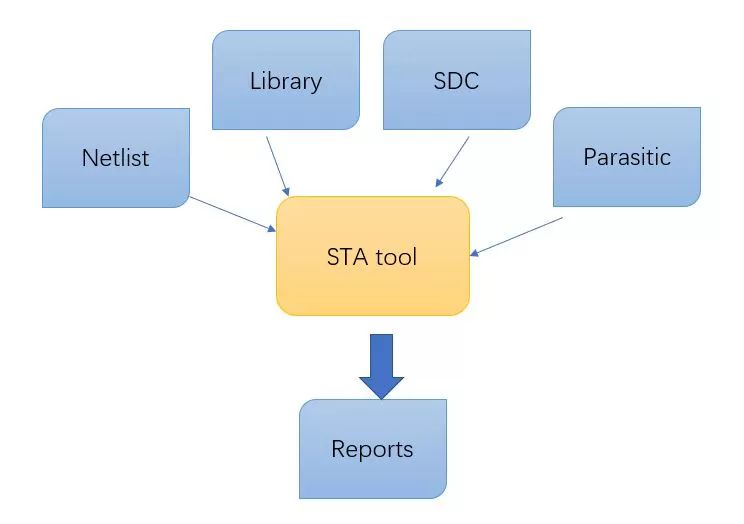

那么如何去做STA,需要准备些什么文件呢?简单的可以用下图表示:

我们需要准备设计的libarary data (包括cell的lib和operating condition等等),Timing constraints(包括clock的描述,design boundry的约束等其他sdc),Gate-level-netlist,sdf/spef等rc信息文件; 然后需要指定时序分析模式,最后会产生设计中的详细时序分析报告。

-

GPIO的基本概念简析2021-12-15 0

-

ESP8266 WIFI模块基本概念与工作模式简析2022-01-18 0

-

时序分析中的一些基本概念2017-02-11 3984

-

时序分析基本概念介绍——时序库Lib,除了这些你还想知道什么?2017-12-15 10591

-

详细介绍时序基本概念Timing arc2018-01-02 23609

-

时序分析和时序约束的基本概念详细说明2021-01-08 1191

-

时序设计基本概念之collection2021-11-26 3340

-

FPGA设计中时序分析的基本概念2022-03-18 2146

-

STA-0.静态时序分析概述2023-06-27 575

-

静态时序分析的基本概念和方法2023-06-28 806

-

介绍时序分析的基本概念lookup table2023-07-03 762

-

介绍时序分析基本概念MMMC2023-07-04 1604

-

时序分析Slew/Transition基本概念介绍2023-07-05 1708

-

时序分析基本概念介绍—Timing Arc2023-07-06 1587

全部0条评论

快来发表一下你的评论吧 !