关于单片机加上上拉电阻的详细解释

电子说

描述

51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态,对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。

在一个系统中或在一个整体中,我们往往定义了一些参考点,就像我们常常说的海平面,在单片中也是如此,我们无论说是高电平还是低电平都是相对来说的。明确了这一点对这一问题可能容易理解。

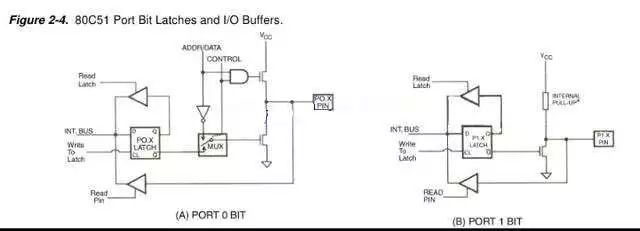

在51单片机,没有连接上拉电阻的P0口相比有上拉电阻的P1口在I/O口引脚和电源之间相连是通过一对推挽状态的FET来实现的,51具体结构如下图。

51结构图

组成推挽结构,从理论上讲是可以通过调配管子的参数轻松实现输出大电流,提高带载能力,两个管子根据通断状态有四种不同的组合,上下管导通相当于把电源短路了,这种情况下在实际电路中绝对不能出现,从逻辑电路上来讲,上管开-下管关开时IO与VCC直接相连,IO输出低电平0,这种结构下如果没有外接上拉电阻,输出0就是开漏状态(低阻态),因为I/O引脚是通过一个管子接地的,并不是使用导线直接连接,而一般的MOS在导通状态也会有mΩ极的导通电阻。

排阻(图片来源于网络)

到这里就很清楚了,无论是低阻态还是高阻态都是相对来说的,把下管子置于截止状态就可以把GND和I/O口隔离达到开路的状态,这时候推挽一对管子是截止状态,忽略读取逻辑的话I/O口引脚相当于与单片机内部电路开路,考虑到实际MOS截止时会有少许漏电流,就称作“高阻态”

由于管子PN节带来的结电容的影响,有的资料也会称作“浮空”,通过I/O口给电容充电需要一定的时间,那么IO引脚处的对地的真实电压和水面浮标随波飘动类似了,电压的大小不仅与外界输入有关还和时间有关,在高频情况下这种现象是不能忽略的。

总之一句话高阻态是一个相对概念。在使用的时候我们只要按照要求去做,让我们加上拉我们就加上,都是有一定道理的。

-

最详细的上拉电阻解释,帮您理解上拉电阻2011-06-02 0

-

51单片机I/O口接上拉电阻的作用???大侠给解释一下。2012-07-23 0

-

关于上拉电阻2013-06-13 0

-

51单片机的IO口驱动能力、灌电流、拉电流、上拉电阻的选择2013-11-18 0

-

DIP封装的51单片机P0口驱动数码管时需要加上拉电阻,PQFP封...2014-10-25 0

-

关于51单片机IO引脚的驱动能力与上拉电阻2016-06-26 0

-

几个问答让你轻而易举看懂上拉电阻与下拉电阻2019-03-25 0

-

上拉电阻与下拉电阻有什么作用2019-05-20 0

-

GPIO电路图与上拉电阻的作用(附详细分析)2020-06-12 0

-

单片机一定要加上拉电阻,你知道其中含义吗?2020-08-06 0

-

单片机必学:GPIO电路与上拉电阻2020-10-12 0

-

上拉电阻的目的是什么2021-07-27 0

-

为什么要在51单片机外部接上拉电阻呢2022-01-14 0

-

解释一下上下拉电阻2022-01-14 0

全部0条评论

快来发表一下你的评论吧 !