关于高速信号几个基本问题的解答分析

电子说

描述

1、为什么要用信号的上升(下降)时延长短来判断是否为高速信号?

A:信号越“陡”,需要保持信号完整的频率分量也就越多(福利叶变换可知;一般数字信号保持5倍频最多,因为取5倍频已经考虑到了信号90%的能量)。又不同频率的信号有不同的传输特性,传输使用的频带越宽传输特性越复杂。如,同样是150M信号,如果取7倍频,信号会好看很多,但是它的传输频率会达到1GHz;分立元件在150M-1G这个频段内的特性变化很大,说不定哪个频率就会出现驻波现象。况且,信号不是“纯”的150M,情况便复杂的多。

2、高速信号和普通的低频信号分析上有哪些不同?

A:从考虑的物理量,传输系统和电路模型三个方面考虑。

低频电路系统

物理量为:电流、电压、电阻、电容、电感。传输系统为可见的回路式电路。电路模型为分立元件电路、集总模型。

微波电路系统

物理量为:功率、损耗、特征阻抗、传输模式。传输系统为可见不可见介质回路形式,大气、波导、传输线等。电路模型为麦克斯韦方程、等效分布模型。

3、怎样看待高速信号的传输过程,如果不是像低频系统中的“电子流”那样?

A:电磁波的传输是电磁波在传输介质中交替建立电场和磁场传输的。这个交替的过程会一直沿着某个方向延续下去,虽然电场的强度会不断减弱。我们分析常用的是TEM模型,也就是限制电磁波传播方向在Z轴方向。换句话说,不是沿Z轴向前,就是向后。那么,如果遇到“障碍物”,电磁波有一部分继续传输,而另一部分则是被反射回来,反向传输。我们定义电磁波传输的反射电压和前向电压之比为反射系数。

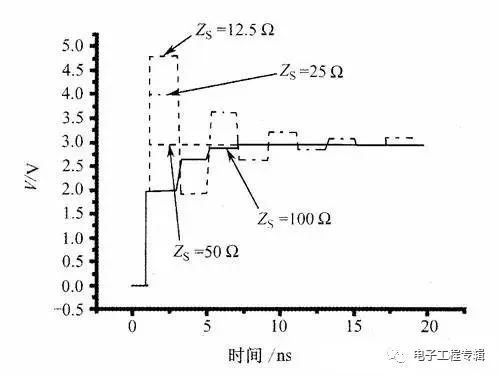

4、匹配到底是该匹配源端还是终端?

A:虽然源端和终端都存在匹配问题,但是终端的匹配更重要一些,因为这是消除反射的最佳位置。事实上,很多工程师提到匹配,都会默认为终端匹配。当然,在很多情况下,终端不允许做匹配或者终端匹配机制做的不好,那就要在源端来进行匹配了。比如,时钟芯片的输出管脚,一定要接一个22Ω或者33Ω的电阻,这就是典型的源端匹配。源端匹配和终端匹配并不矛盾,只是匹配的位置和消除反射的对象不同而已。

5、到底该如何理解“阻抗”impedence?

A:对于所有的理想元件,其阻抗定义为该导体两端的电压(矢量)和流经该导体的电流(矢量)的比值。这个定义不管是在时域还是频域都是有效的。从这个定义出发,那么有,对于理想电阻,其电压和电流总是同频矢量,即,理想电阻不会影响信号的频率。而对于理想电感和电容,我们推导得出其阻抗分别问ZL=jwL,ZC=-jwC。即电感和电容的阻抗都是频率相关量。注意,这里说的是理想元件!对非理想元件,需要建立等效模型来研究。需注意的是,电磁波每经过一段导线Δx,它都要建立相应的电磁场,则对应一个瞬时阻抗。如果传输线上每个单元Δx等效电路相同,且其物理特性完全一致,即每个瞬时阻抗都是一致的。那么,该瞬时阻抗就可以定位为该传输线的特征阻抗。而该传输线系统便是“连续且均匀的”。

6、传输线结构应该怎样理解?

A:一个独立的点可以构成电场吗?答案是不能的。如果把导线上某点看成两个电势点中的高电势点的话,那还得要一个低电势点。也就是为信号提供回流路径。注意!不是只有通常意义上的地平面,任何能够和信号线之间建立电场和磁场联系的导体,都能和信号线提供回流路径。对于一段微带线,和它构成传输线结构的路径包括了:微带线本身,回流路径,以及微带线和回流路径之间的介质。所以,这条传输线的特性阻抗,其实是这整个传输线结构中各个因素等效后的综合结果。

7、为什么是50Ω?

A;原因一是和以前的产品及系统相兼容,就像“铁轨宽度是由马屁股决定的”那样;原因二是,CMOS的输出阻抗一般在几十欧姆,且IBM的调查显示,板级设计的也是40Ω~80Ω为最优。

-

PCB Layout and SI 信号完整性 问答专家解答(经典资料18篇)2008-12-25 0

-

高速信号分析的几个基本问题2017-12-16 0

-

高速信号分析的基本问题解答2019-06-25 0

-

信号反射的几个基本问题分析2019-10-16 0

-

转一篇很好的AD转换设计中的基本问题整理 精选资料分享2021-07-28 0

-

高速电路信号完整性分析之应用篇2006-05-28 937

-

关于HPLC的常见问题及解答2009-12-25 1215

-

AD转换设计中的基本问题整理2017-12-25 13648

-

高速信号分析几个基本问题2022-12-09 842

-

关于差动放大电路实验的几个问题2021-04-09 577

-

关于半导体制冷片的几个常见问题2021-04-26 4817

-

高速电路信号完整性分析与设计—调试技巧2022-02-10 597

-

高速电路信号完整性分析与设计—串扰2022-02-10 532

-

高速电路信号完整性分析与设计—信号完整性仿真2022-02-10 1387

-

嵌入式程序员应知道的几个基本问题2023-11-20 90

全部0条评论

快来发表一下你的评论吧 !