基于74LS90数字电子钟逻辑电路的设计

应用电子电路

描述

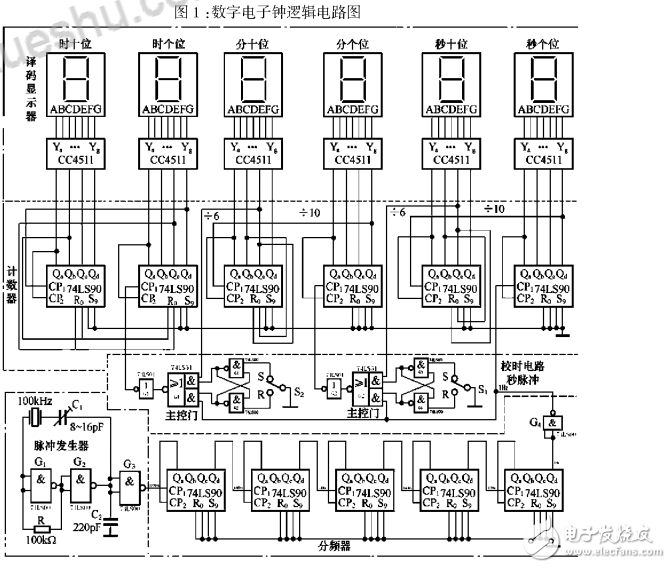

数字电子钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长使用寿命的优点,因此得到了更广泛的使用,数字电子钟从原理上讲是一的数字电路,其中包括了组合逻辑电路和时序电路。

脉冲信号发生器

石英晶体振荡器的振荡频率最稳定,其产生 的信号频率为100KHz, 通过整形缓冲级G3 输出矩形波信号。

分频器

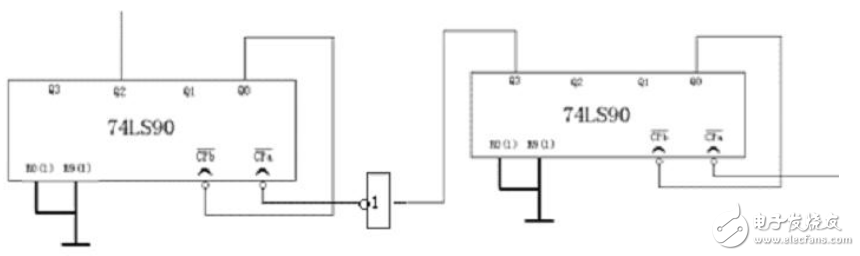

石英晶体振荡器产生的信号频率为100KHz, 要得到1Hz的秒脉冲信号, 则需要分频, 图中采用5个中规模计数器74LS90, 将其串接起来组成105分频器。每块74LS90的输出脉 冲信号为输人信号的十分频, 则100KHz的输人脉冲信号通过五级分频正好获得秒脉冲信号, 秒信号送到计数器的时钟脉冲GP端进行计数。首先, 将74LS90连成十进制计数器 共需5块, 再把第一级的GP1接脉冲发生器的输出端。 第一级的QD端接第二级GP1的,第二级的QD端接第三级的GP1 … …第五级的输出QD就是秒脉冲信号

计数器

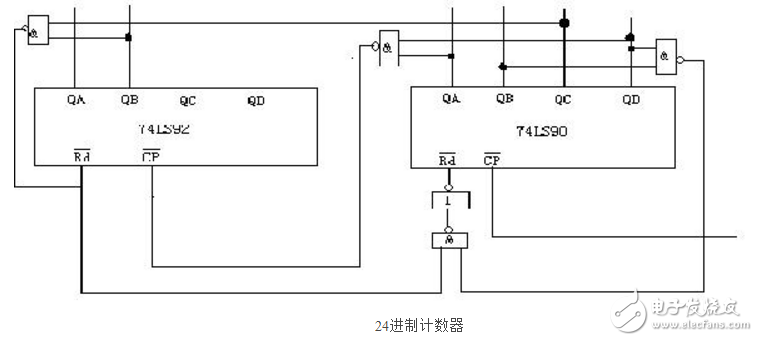

秒计数器采用两块74LS90接 成六十进制计数器, 分计数器也是采用两块74LS90接成六十进制计数器。 时计数器则采用两块74LS90接成二十四进制计数器,秒脉冲信号经秒计数器累计, 达到“60” 时秒计数器复位归零并 向分计数器送出一个分脉冲信号, 分脉冲信号再经分计数器累计, 达到“60” 时分计数器复位归零并 向时计数器送出一个时脉 冲信号, 时脉冲信号再经时计数器累计, 达到‘24’时复位归零

译码显示电路

时、 分、 秒计数器的个位与十位分别通过每位对应一块七段显示译码器GG4511和半导体数码管, 随时显示出时、分、 秒的数值

校时电路

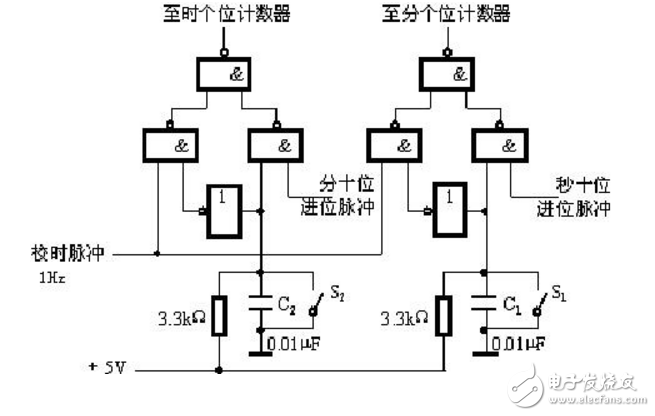

在图中设有两个快速校时电路, 它是由基本RS触发器和与或非 门组成的控制电路, 电子钟正常工作时, 开关S1、S2 合到S端, 将基本RS触发器置“1” , 分、 时脉冲信号可以通过控制门电路。 当开关S1、S2合到S 端时, 将基本RS触发器置“0”,封锁了控制门电路, 使正常的计时信号不能通过控制门电路, 而秒脉冲信号则可 以通过控制门电路, 使分、 时计数器变成 了秒计数器, 实现了快速校准

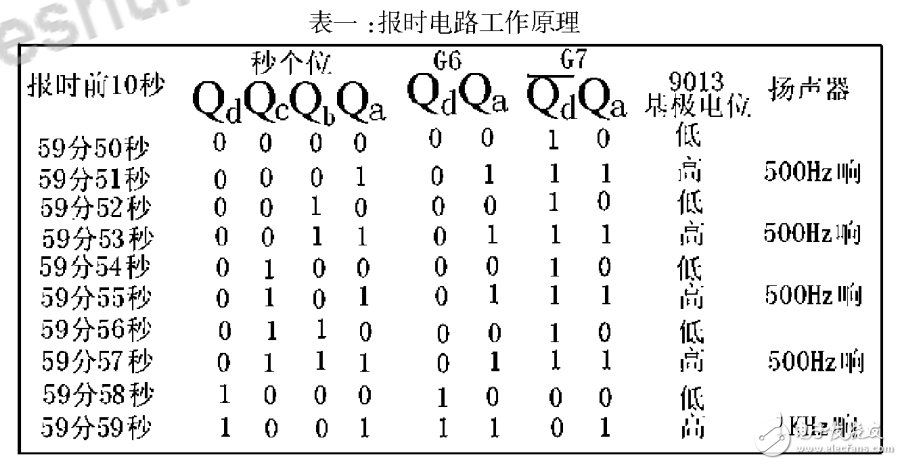

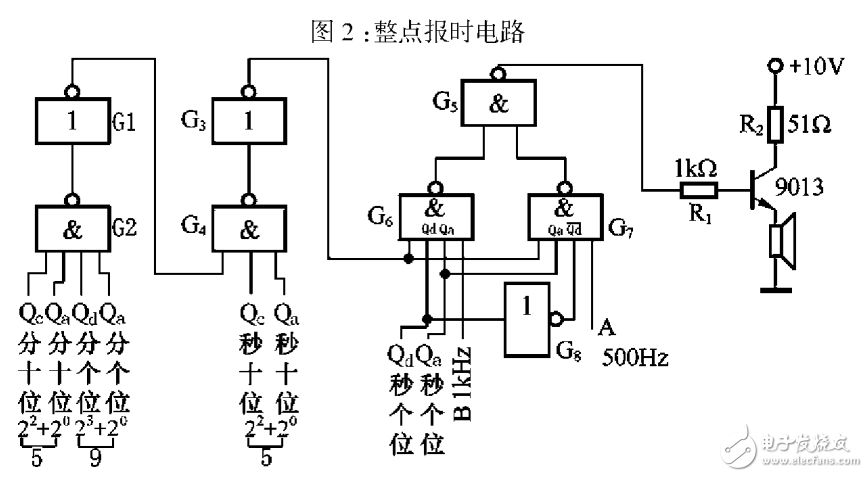

整点报时电路

每当分计数器和秒计数器计到59分秒时, 便自动驱动音响电路, 在10秒内自动发出5次鸣叫声, 每隔1秒 叫一次,每次叫声持续1秒, 并且前4声的音调低, 最后一响的音调高, 此时计数器指示正好为整点(“0”分“0”秒)。音响电路采用射极跟随器推动扬声器发声,报时所需的1KHz及500Hz音频信号可以从图一的多级分频电路中取得。

时分秒计数器的设计

分和秒计数器都是60进制的计数器

其计数规律为00—》01—》...—》58—》59—》00

选74LS90作个位计数器10进制计数器, 将R0(1) ,R9(1) 接地, 74LS90 为10进制计数器; 74LS90作十位6进制记数器。将R0(1) ,R9(1) 接地, 74LS90 为10进制计数器Q2输出的则为6进制。再将它们级联组成60进制的计数器

小时计数器是一个24进制计数器,同样选用74LS90作十位计数器,74LS90作个位计数器。当小时的十位不到2时,小时的个位是十进制计数器;而当小时的十位为2时,小时的个位是4进制计数器。当数字钟运行到23时59分59秒时,秒的个位计数器再输入一个秒脉冲时,数字钟应自动显示为00时00 分00秒,实现日常生活中习惯用的计时规律。

校时电路设计

校时是数字钟应具备的基本功能。一般电子手表都具有时、分校时功能。当数字钟接通电源或者计时出现误差时,需要校正时间。分别对分、时进行连续脉冲校准调整时,在小时校正时不影响分和秒的正常计数,在分校正时不影响秒和小时的正常计数。

校时脉冲采用分频器输出的1Hz脉冲。由于校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,接电容C1、C2可以缓解抖动。

-

8.9.2 74LS90介绍(1)#硬声创作季学习硬声知识 2022-12-03

-

8.9.2 74LS90介绍(2)#硬声创作季学习硬声知识 2022-12-03

-

8.9.3 74LS90构成任意进制计数器(1)#硬声创作季学习硬声知识 2022-12-03

-

8.9.3 74LS90构成任意进制计数器(2)#硬声创作季学习硬声知识 2022-12-03

-

74ls90引脚图及引脚功能2008-04-01 120892

-

74ls90电子秒表说明书2016-05-20 2160

-

数字电子钟逻辑电路设计2016-06-22 2581

-

74LS90 英版数据手册2016-08-29 1439

-

74LS90英文手册2016-11-05 1195

-

74ls90工作原理_逻辑功能表_电性参数及应用电路2017-12-22 254373

-

74ls90和74ls290的区别是什么?2018-01-26 23436

-

74ls90应用电路图大全(脉冲发生器/分频电路/计数器/数字电子钟逻辑电路)2018-05-29 65760

-

74LS90引脚图及引脚功能资料免费下载2019-05-30 4490

-

74LS90测试电路的3D原理图免费下载2021-03-24 1090

-

74ls90管脚图和真值表2021-06-04 19349

全部0条评论

快来发表一下你的评论吧 !