移位寄存器实验报告_移位寄存器原理

存储技术

描述

什么是移位寄存器

在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器特点

移位寄存器可以用来寄存代码,还可以用来实现数据的串行—并行转换、数值的运算以及数据的处理等。

移位寄存器原理

移位寄存器不仅能寄存数据,而且能在时钟信号的作用下使其中的数据依次左移或右移。

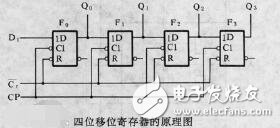

四位移位寄存器的原理图如图所示。F0、F1、F2、F3是四个边沿触发的D触发器,每个触发器的输出端Q接到右边一个触发器的输入端D。因为从时钟信号CP的上升沿加到触发器上开始到输出端新状态稳定地建立起来有一段延迟时间,所以当时钟信号同时加到四个触发器上时,每个触发器接收的都是左边一个触发器中原来的数据(F0接收的输入数据D1)。寄存器中的数据依次右移一位。

移位寄存器实验报告

(一) 实验原理

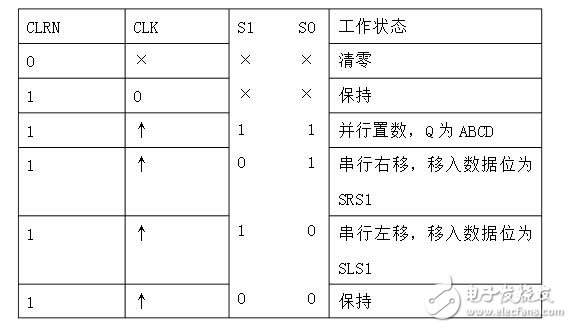

移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路。根据移位寄存器存取信息的方式可分为串入串出、串入并出、并入串出、并入并出4种形式。74194是一种典型的中规模集成移位寄存器,由4个RS触发器和一些门电路构成的4位双向移位寄存器。该移位寄存器有左移,右移、并行输入数据,保持及异步清零等5种功能。有如下功能表

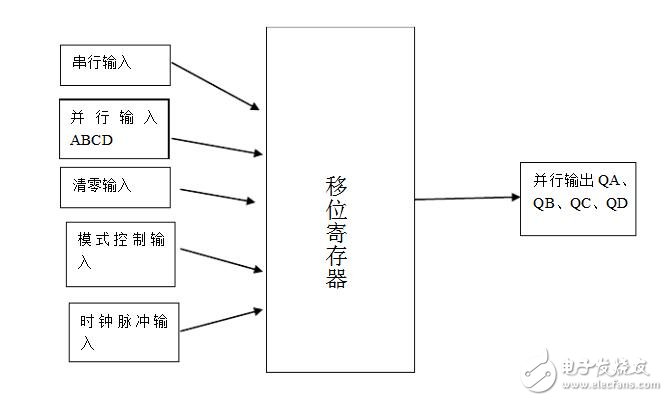

(二) 实验框图

(三) 实验内容

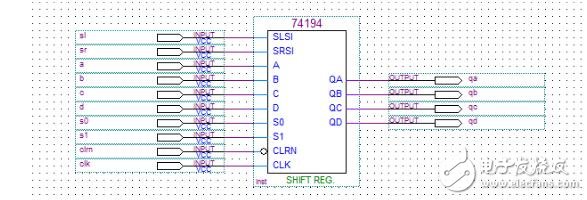

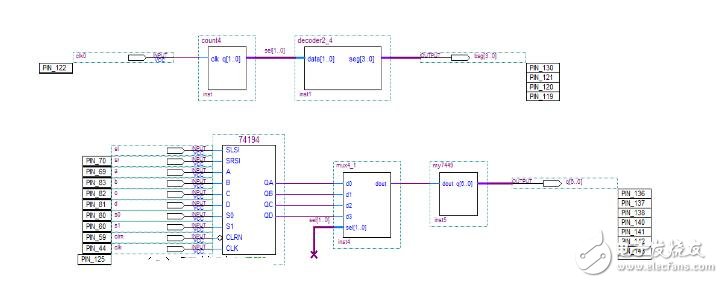

1.按如下电路图连接电路

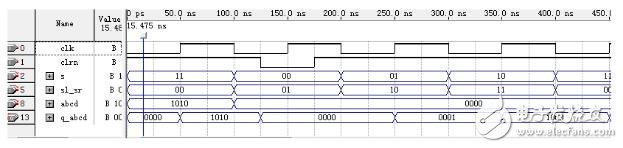

2.波形图

参数设置:

End time:2us Grid size:100ns

波形说明:

clk:时钟信号; clrn:置0 s1s0:模式控制端 sl_r:串行输入端

abcd:并行输入 qabcd:并行输出

结论:

clrn优先级最高,且低有效高无效;s1s0模式控制,01右移,10左移,00保持,11置数重载;sl_r控制左移之后空位补0或补1。

3.数码管显示移位

(1)电路图

管脚分配:

a,b,c,d:86,87,88,89

bsg[3..0]:99,100,101,102

clk:122

clk0:125

clrn:95

q[6..0]:51,49,48,47,46,44,43

s0,s1:73,72

sl_r:82,83

结论:

下载结果与仿真结果一致,下载正确。

- 相关推荐

- 移位寄存器

-

线性移位寄存器2010-01-12 1772

-

移位寄存器原理2019-06-20 0

-

四位双向移位寄存器实验2009-03-16 2070

-

集成移位寄存器2009-03-20 863

-

可越位的移位寄存器2009-04-10 437

-

移位寄存器,移位寄存器是什么意思2010-03-08 17114

-

移位寄存器及其应用实验2012-07-16 6969

-

寄存器与移位寄存器2016-05-20 1072

-

移位寄存器具有什么特点及作用?2017-12-22 82444

-

移位寄存器的特点_移位寄存器工作原理2017-12-22 46428

-

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途2017-12-22 19256

-

一文解析Matlab如何实现移位寄存器2018-04-26 15979

-

移位寄存器的原理2019-07-15 71767

-

labview移位寄存器的用法及作用2020-11-11 50721

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 1556

全部0条评论

快来发表一下你的评论吧 !