FPGA的多重加载实际运用详解

FPGA/ASIC技术

描述

如今,随着FPGA工艺的进步,性能提升和成本缩减均得到极大的改善,这使得FPGA芯片的使用越来越广泛。因此为了达到降低系统维护和升级的成本,通常我们都会通过网络传送最新的下载文件,让用户在现场直接将文件下载到FPGA中进行远程的升级处理。然而,一旦下载文件是错的,那么系统轻则功能出错,重则直接死机不工作。为了防止这种情况发生给用户带来重大影响或者损失,Xilinx提供了FPGA的多重配置操作功能。

1.何为多重配置

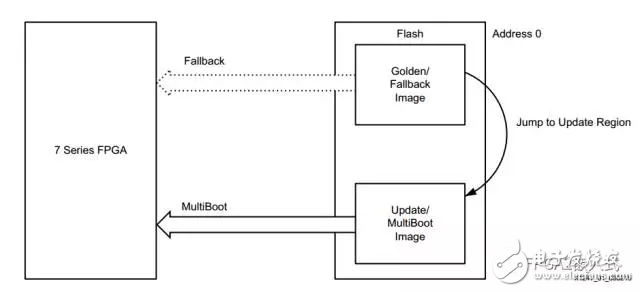

FPGA多重配置允许动态进行多个下载文件之间的切换,当引导配置过程中检测到出错时,FPGA会触发一个回退标志确保一个已知的好的文件可以被加载进来。具体如下图所示:

简而言之,就是你的.mcs文件里包含有两个或更多的下载文件,然后地址0的位置开始存放一个可用的下载文件(多数是升级前那个旧的文件),后面的地址(ADDR_1)存放你将要更新的文件。当下载时,FPGA会先从ADDR_1读取更新的文件,若这个过程发生错误的话就会回到地址0,读取之前的文件,确保设备仍能正常工作。

2.多重配置的使用

Xilinx的多重配置功能除了更新文件外,也可以进行多任务的切换调度处理。基于这个功能,只要Flash够大,是可以存放好多个下载文件的。当遇到FPGA资源较小,且多个功能之间是独立不干扰的话,有时候可以通过外部控制,在需要不同功能时,进行文件切换下载。

比如一个设备需要做到ABCD四个功能,且ABCD各自应用于不同场合,之间没有数据往来,互不干扰。如果这时FPGA的资源只能够实现ABCD中的一种功能或者两种,那么我们就可以做出四个不同的bit文件分别实现ABCD四种功能并合并成一个.mcs文件下载到Flash中。当在需要A功能的场合,我们可以使用按键或者上位机进行配置,让FPGA加载A功能的下载文件,实现A功能。同理,在只需要BCD的场合也是这样,如此可以大大节省FPGA的资源。

3.多重配置的流程

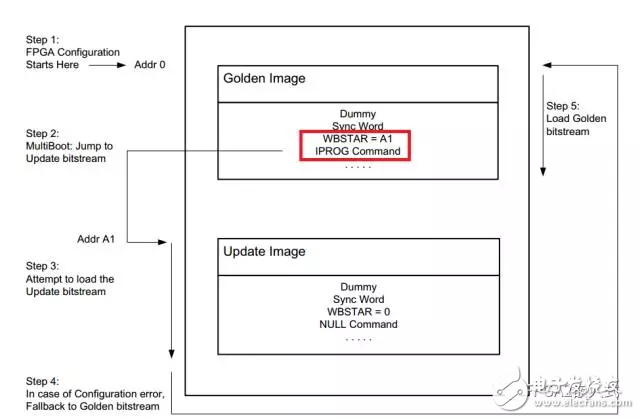

FPGA内部有一个ICAP核,可对程序加载进行预配置,预配置处理可在.v代码中处理并随之生成.bit文件。如果不在代码处理,则为默认配置。Xilinx FPGA的多重配置流程如下图所示,具体可参考官方文档 “ xapp1247 ” 。

其中可用文件存放在起始地址为0处;更新文件存放在起始地址为A1处。

上电后,FPGA会进入Flash的0地址,检测配置寄存器中的WBSTAR和IPROG指令(.v里进行配置)。

如果WBSTAR地址指向A1,且IPROG的指令正确,FPGA会跳到A1处读取并加载文件。

如果A1处的WBSTAR地址为0,且没有IPROG指令,则加载此处的文件。

如果在加载更新文件过程中发生错误,FPGA便会跳到地址0处,重新加载确保可用的那个文件。

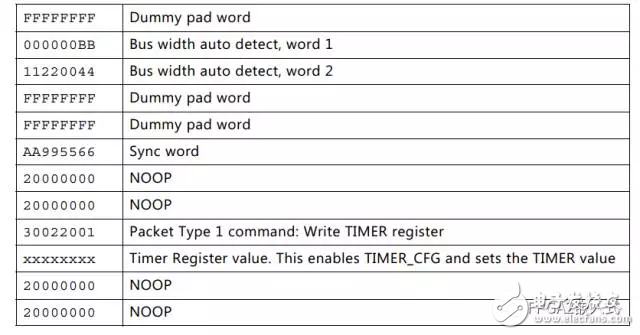

IPROG的指令表如下所示:

对于IPROG的指令配置,必须按照这个顺序进行,一旦数据不对或者顺序不对,FPGA便不会对更新文件进行加载。

4.结语

在实际使用中FPGA的多重加载是非常有帮助的,灵活的使用能够避免很多现场的尴尬,也节省了很多后期技术支持的成本。下一节将介绍如何进行代码的多重配置处理与使用。

-

labview实际运用2013-01-28 0

-

详解FPGA上电加载时序2019-07-18 0

-

如何在a7 fpga中实现回退多重启动2020-06-01 0

-

TMS320C61416控制FPGA数据加载设计2011-08-16 1587

-

揭秘FPGA多重配置硬件电路设计方案2015-02-02 1132

-

FPGA多重加载技术的设计模块及其在硬件平台上的多模式启动测试并分析2017-11-18 5953

-

FPGA的配置/加载方式2018-10-05 17372

-

一种基于CPLD加载FPGA的方案设计详解2019-02-19 1951

-

FPGA上电加载时序介绍2019-07-01 16296

-

基于外部处理器的FPGA加载应用程序的方法研究2020-08-13 1854

-

浅谈光伏并网柜的实际运用2021-09-23 1001

-

解析Zynq的加载方式2022-05-09 2463

-

FPGA上电时序加载过程详解2022-12-26 1837

-

AMD FPGA的SelectMAP加载模式2023-07-07 1239

全部0条评论

快来发表一下你的评论吧 !