如何利用SDSoC工具来创建嵌入式C/C++/OpenCL应用开发

电子说

描述

教你如何使用Xilinx SDSoC

实现在ARTY Z7上进行软硬协同设计

细心的小伙伴们可能早已留意到,在Digilent今年全新出品的Zynq评估板中,无论是第二代经典入门级的Zynq™ Board - ZYBO Z7,还是创客最爱的ARTY Z7,都全面支持Xilinx SDSoC开发环境。意味着如果你是一名系统或软件工程师,现在无需深度的硬件专业知识,就能广泛地利用Zynq® SoC,畅享超过100倍的软件性能加速。

本篇干货教程中,我们就将带你入门了解如何使用Xilinx SDSoC工具来创建嵌入式C/C++/OpenCL应用开发,并实现直接在ARTY Z7嵌入式视觉开发平台的器件上进行软件设计。

01

SDSoC软硬协同设计与其开发流程

由于集成了ARM处理器内核与可编程逻辑,对于众多应用开发而言,Zynq 非常的灵活。这意味着开发人员可以将设计按不同的元素来优化划分,例如将其中那些高层次决策的部分放入ARM内核(PS端),并将诸如图像处理流水线等需要加速的部分用可编程逻辑(PL端)来实现。

当然,传统的Zynq开发流程会将Vivado和SDK分离开来,这种方法很难在可编程逻辑(PL)和处理系统(PS)之间分配功能,因此无法获得最优的系统性能。

通过SDSoC,则可以解决上述问题。SDSoC是一个系统最优编译器,支持软件定义的整个系统开发,包括PS和PL。标准的SDSoC开发流程如下:

-

使用高层次语言开发应用

-

使用提供的性能监视器来分析设计从而确定性能瓶颈

-

使用SDSoC将造成性能瓶颈的功能用可编程逻辑来实现加速

-

重新验证性能,如果有必要也可以加速其它功能模块

正是因为高层次综合(HLS)和互联框架的结合才使得各种功能模块可以在PS和PL之间轻松的转换:

-

使用Vivado HLS加速某个功能模块

-

分析通信功能

-

建立AXI通信

-

生成软件存根

为了能够使可编程逻辑获得最佳的性能,我们需要给加速的功能模块定义一些优化参数,这样才能够确定HLS工具执行哪些优化操作。我们可以使用高层次语言(比如C/C++/OpenCL)来开发基于Zynq的设计。为了支持SDSoC的使用,我们需要一个面向SDSoC的基础平台来定义底层硬件和软件环境。

对于Arty Z7,点击「阅读原文」,在“下载代码”按钮中可以找到Arty Z7对应的SDSoC基础平台,下载之后就可以在Arty Z7上开发相关的应用了。

02

创建一个新的SDSoC工程

在这一教程中,我们将探究如何使用SDSoC平台来加速矩阵乘法的性能。

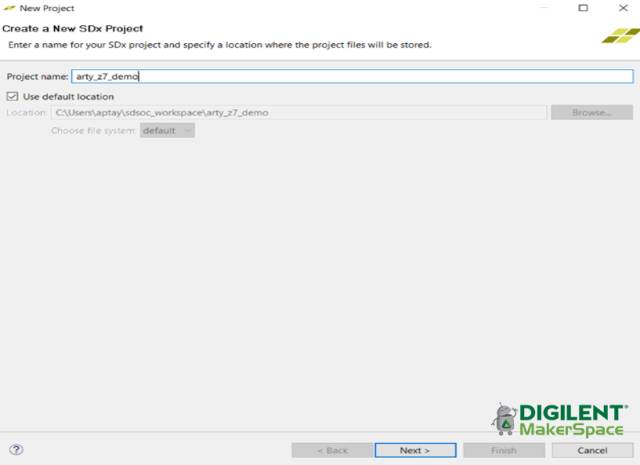

使用SDSoC工具创建一个新的SDSoC工程,具体操作步骤如下:File -> New -> Xilinx SDx Project。这会打开一个新工程的对话框,包括支持的平台规范、操作系统选择和示例应用选择。详细图解如下。

创建一个新工程:

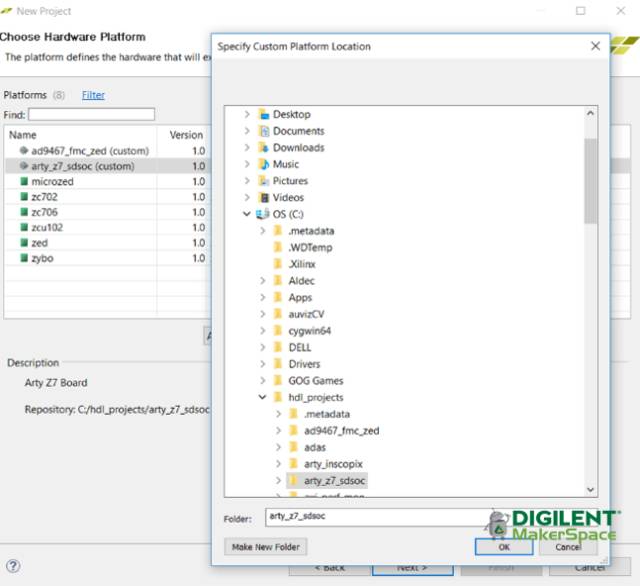

选择Arty7 Z7-20作为硬件平台。这里,在新工程对话框的第二页选择一个新的平台,点击添加自定义平台选项(add custom platform)。然后对应找到已下载好的Arty Z7-20平台,添加好后这个平台就能在构建列表中看到,在此基础上我们可以选择它应用到我们的工程中:

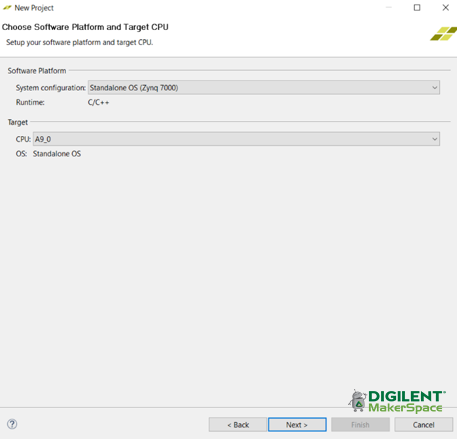

选择操作系统(OS)和目标CPU:

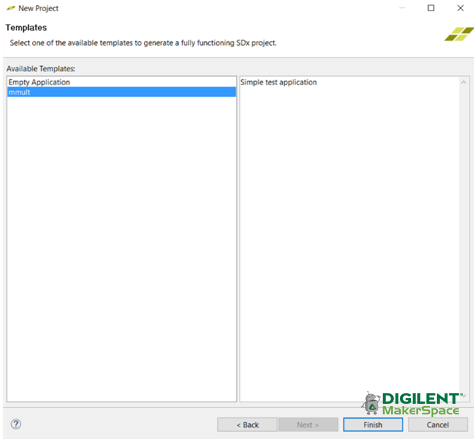

然后选择示例应用:

03

SDx项目设置页面

完成项目新建之后,将在SDSoC开发环境中看到SDx项目设置页面。我们使用这个项目设置选项卡可以在PS和PL之间转移功能。实现方式是:选择“Add HW Function”按钮,然后选择所需要移植到PL中的功能。

如果我们想将原本在PS中运行的功能转移到PL中来实现加速,那么我们应当遵循以下几条规则:

-

这个功能不能包含任何操作系统级的系统调用

-

这个功能必须完整

-

C结构体需要有界并固定大小

-

结构体的实现是明确的

在项目设置控制面板上,我们也可以控制加速模块和PL与PS之间数据移动网络传递数据的操作频率。

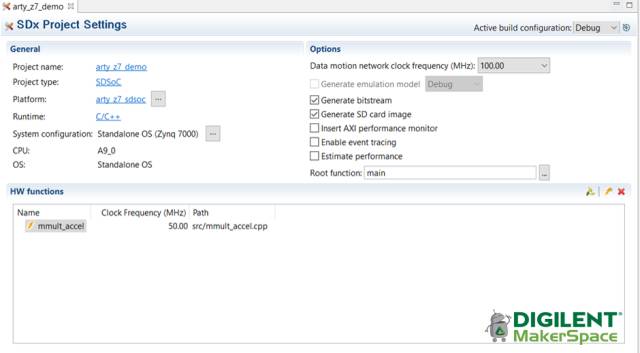

SDSoC Project Settings – 此界面显示的是SDSoC主要的控制功能:

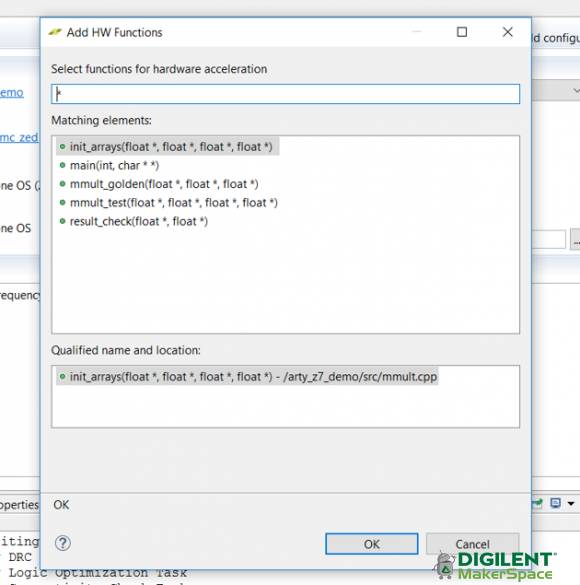

Add HW Function界面 – 显示可以用于加速的函数:

04

预估性能选项与启动调试器

当SDSoC构建时会生成必要的bin文件,我们可以将其放到SD卡中来启动运行或者下载到Zynq中用于调试。构建过程需要一定的时间,因此在很多情况下当我们选择一个函数用于加速时,我们可以先运行一个功能,估计一下需要的总资源和预期的加速效果。通过在项目设置菜单中点击“估计性能(estimate performance)”选项就可以实现上述这一步。

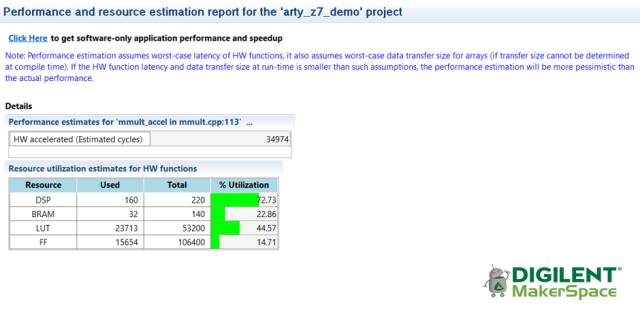

整个构建过程完成后就会生成一个结果报告,估计运行结果界面如下图:

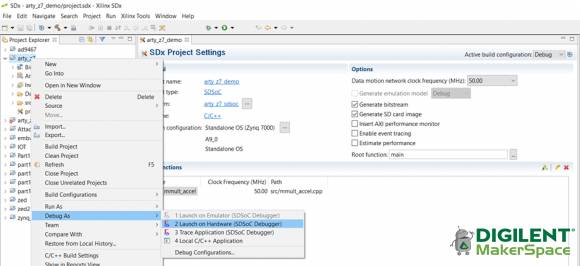

如果我们构建这个设计时没有点击预估性能选项,那么我们可以使用调试器(debugger)像正常应用那样下载和运行示例程序。要想启动调试器,在工程上右击,然后选择Debug As ->Launch on Hardware(SDSoC Debugger)。参考下图启动调试界面,这里我们会将应用下载到Arty Z7,并在编程入口使Zynq挂起。将SDSoC终端与Arty Z7 UART(串口)连接我们就可以看到示例程序的运行结果:

05

利用好SDSoC开发环境中库的优势

当我们开发自己的SDSoC应用时,我们需要了解SDSoC提供的库和加速栈资源。

为了帮助开发者能够更快地开发最终应用,SDSoC提供了一些HLS库,开发者可以将其应用到自己的设计中,具体包括:

-

reVison Stack – 提供了一个三元素开发栈,我们可以使用OpenCV、Caffe和一系列通用的神经网络开源框架到嵌入式视觉应用中。reVision包括多重加速能力的OpenCV。

-

数学库 – 提供了标准数据库可综合的实现。

-

IP库 – 提供了可以实现FFT、FIR和移位寄存器LUT功能的IP库。

-

线性代数库 – 提供了通用线性代数功能的库资源。

-

任意精度数据类型库 – 提供无二次幂和有符号/无符号整数任意数据长度的支持,这个库可以让开发者更加高效的使用FPGA资源。

06

总结

通过这个项目中的例子,我们看到借助SDSoC,我们可以在PS与PL之间轻松地转移软件(SW)函数,并通过将之转移到PL端来实现性能上的提升。

So,如果此刻,你已经对利用SDSoC来实现软硬协同开发与优化产生了兴趣,赶快拿起一块Arty Z7,参照着教程尝试一下快感吧!

-

[推荐][分享]uCOS-II-CN开发资料、C和C++嵌入式系統編程2009-12-10 0

-

[分享]基于ARM的嵌入式开发、C和C++嵌入式系統編程2009-12-10 0

-

如何为嵌入式应用编写优秀的C++程序代码2014-09-22 0

-

C++在嵌入式领域的用处是什么?2019-11-06 0

-

嵌入式开发中为什么选择C++语言2021-10-27 0

-

什么是嵌入式技术?嵌入式开发方向是什么?2021-11-05 0

-

是否应该使用C++替代C语言进行开发工作2021-11-05 0

-

嵌入式开发与C++开发到底有什么区别呢2021-11-05 0

-

嵌入式C++编程的相关资料分享2021-11-09 0

-

C/C++嵌入式远程调试怎么实现?2021-12-24 0

-

学习C++的方法以及C++的就业方向2021-12-24 0

-

嵌入式开发中C++好用吗2022-02-23 0

-

C/C++/OpenCL 应用编译的SDSoC开发2018-05-21 2021

-

SDSoC系统级的特性描述及应用开发体验2019-07-27 1748

全部0条评论

快来发表一下你的评论吧 !