74ls161中文资料_74ls161计数器功能及其应用

应用电子电路

描述

74ls161计数器是目前比较常见的计数器。

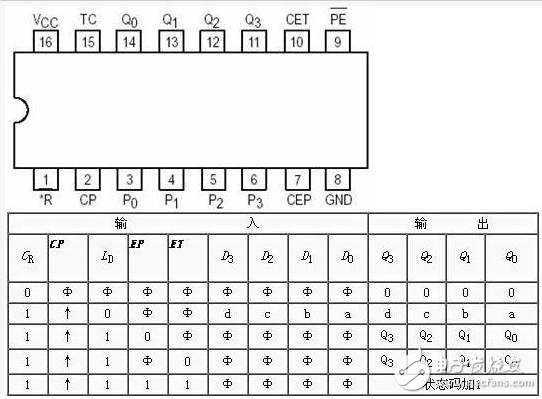

74ls161引脚图及真值表

74ls161功能

74ls161功能表

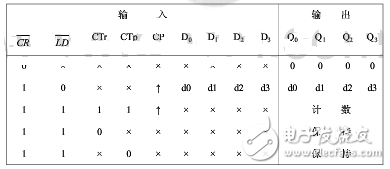

从功能表的第一行可知,当CR=0(输入低电平),则不管其他输入端(包括CP端)状态如何,四个数据输出端Qn、Qn、QC、Qn全部消零。由于这一清零操作不需要时钟脉冲CP配合(即不管CP是什么状态都行),所以为异步清零端,且低电平有效,也可以说该计数器具有“异步清零”功能。

从功能表的第二行可知,当CR=1且西=0时,时钟脉冲CP上升沿到达,四个数据输出端QA、Qn、QC、QP同时分别接收并行数据输入信号a、b、c、d。由于这个置数操作必须有CP上升沿配合,并与CP上升沿同步,所以称那么该芯片具有“同步置数”功能。

从功能表的第三行可知,当LD=CR=1,CTr=CTp=1时,则对计数脉冲CP实现同步十进制加计数。

而从功能表的第四行又知道,当CR=LD=1时,只要CTr和ENP中有-一个为0,则不管CP状态如何(包括上升沿),计数器所有数据输出都保持原状态不变。因此,CTr和CTP应该为计数控制端,当它们同时为1时,计数器执行正常同步计数功能;而当它们有一个为0时,计数器执行保持功能。

另外,进位输出Qcc=CTrQo.Qr.Q2.Q;表明,进位输出端仅当计数控制端CTr=1且计数器状态为15时它才为1,否则为0。

74ls161应用

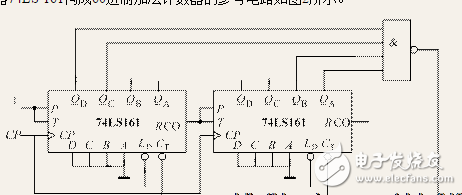

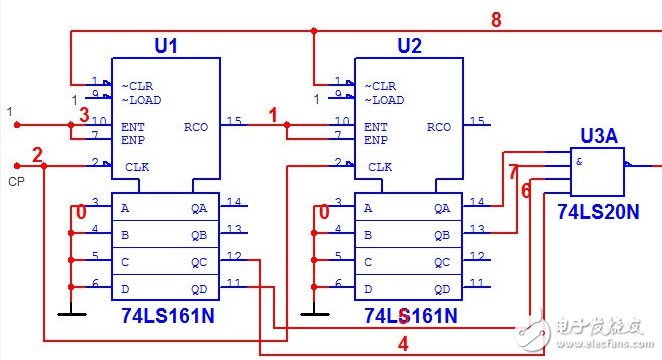

60进制同步加法计数器

用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

加法计数器设计(清零法)

74LS161为十六进制四位二进制加法计数器,异步清零,同步置数。

设计60进制的加法计数器,采用清零法。60用二进制表示为00111100,因为是异步清零,当计数器从零开始计数时,计数到00111100时异步清零即可。要用到两片74LS161,需要两计数器进行级联,采用同步并行级联方式。其中ET和EP都接高电平。低片计数到1100,且高片计数到0011时异步清零,用四输入与非门连接,输出接到端。

多谐振荡器设计

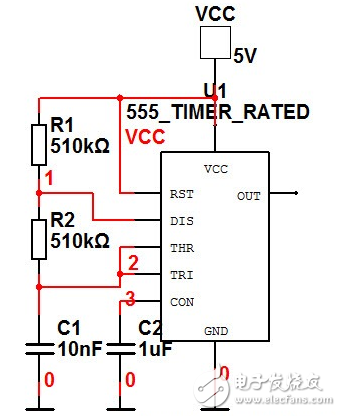

多谐振荡器所给器件中有510K电阻2个,用来做多谐振荡器的外接电阻,电容选用103电容,则多谐振荡器的周期为:

则用555构成的多谐振荡电路为:

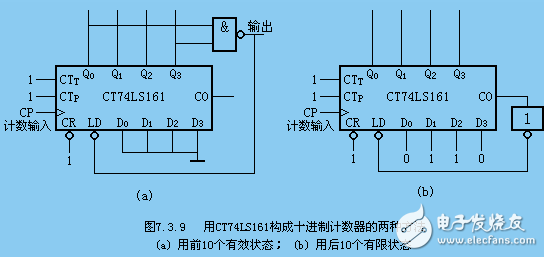

用74LS161构成十进制计数器

-

74ls1612013-05-20 0

-

三片74LS161怎么级联计数2400?2019-04-24 0

-

74LS161中文资料pdf2008-03-20 5297

-

二进制同步计数器74LS161引脚图及功能表(管脚图)2007-11-22 52413

-

74LS161计数器及显示应用电路图2007-12-02 12378

-

74ls161制作24进制计数器设计2018-01-16 115471

-

74ls161管脚图引脚图及功能表2018-01-17 270147

-

基于74LS161的扭环形计数器自启动设计2018-01-17 38422

-

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)2018-01-18 357690

-

74ls160和74ls161区别2018-05-08 117367

-

74ls161与74ls163有什么区别2018-05-08 55912

-

74ls161商品批发价格 74ls161引脚图与管脚功能测试2021-06-08 5229

-

74ls161引脚图及功能介绍2021-07-08 208055

-

74ls161十进制计数器电路图2021-07-09 80662

全部0条评论

快来发表一下你的评论吧 !