fpga基本结构是什么_全面解析

FPGA/ASIC技术

描述

FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

可编程逻辑块

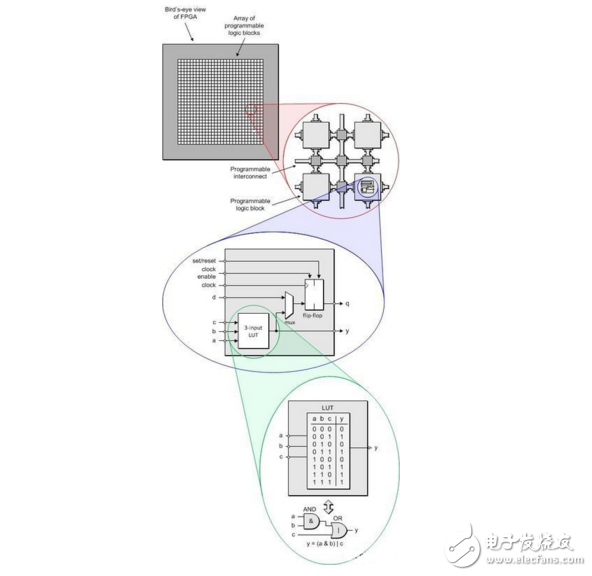

如果我们仔细观察FPGA封装的内部,我们将看到硅片(技术术语裸片)。可编程构造表现为可编程逻辑块阵列,如下图所示。如果我们用放大镜“放大查看”,我们可以看到这种构造由沉浸于可编程互连“海洋”中的许多逻辑“岛”(可编程逻辑块)组成。

如果我们进一步放大,我们可以看到,每个可编程模块都包含有许多数字功能。在这个例子中,我们可以见到一个三输入的查找表(LUT)、一个复用器和一个触发器,但重要的是我们要认识到,这些功能的数量和类型对不同系列的FPGA来说是会变化的。

触发器可以被配置(编程)为寄存器或锁存器;复用器可以被配置为选择一个到逻辑块的输入或LUT的输出;LUT可以被配置为代表任何所要求的逻辑功能。

可编程输入/输出单元IOE

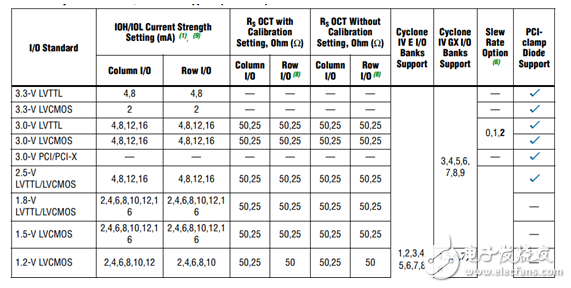

可编程I/O,可配置成OC门、三态门、双向IO、单端/差分等;支持各种不同的I/O标准:LVTTL、LVCOMS、SSTL、LVDS、HSTL、PCI等;

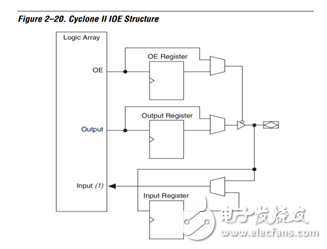

Altera器件IOE结构

Altera器件的输入输出结构:可配置成三态、输入/输出、双向IO

Altera器件中cyclone系列中的IOE结构是基本的输入、输出、使能的触发器结构。

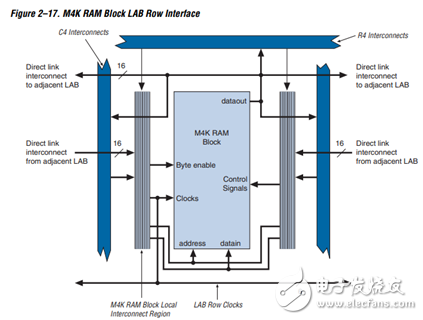

嵌入式块RAM(BRAM)

大多数FPGA都具有内嵌的块RAM,这大大拓展了FPGA的应用范围和灵活性。块RAM可被配置为单端口RAM、双端口RAM、内容地址存储器 (CAM)以及FIFO等常用存储结构。RAM、FIFO是比较普及的概念,在此就不冗述。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入 CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将 FPGA中的LUT灵活地配置成RAM、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。

单片块RAM的容量为18k比特,即位宽为18比特、深度为1024,可以根据需要改变其位宽和深度,但要满足两个原则:首先,修改后的容量(位宽 深度)不能大于18k比特;其次,位宽最大不能超过36比特。当然,可以将多片块RAM级联起来形成更大的RAM,此时只受限于芯片内块RAM的数量,而不再受上面两条原则约束。

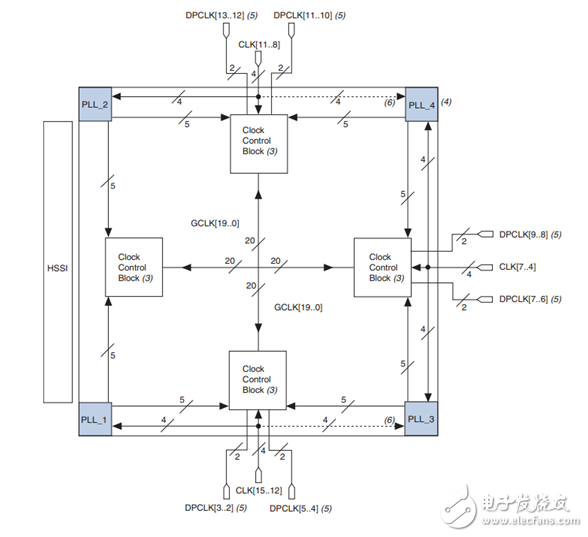

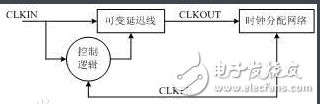

完整的时钟管理

全局时钟树

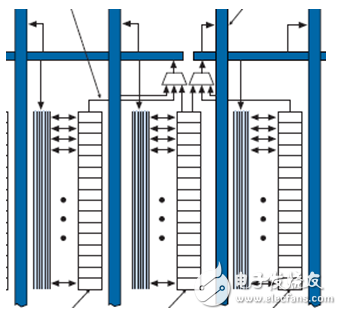

丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片 Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有密切、直接的关系。

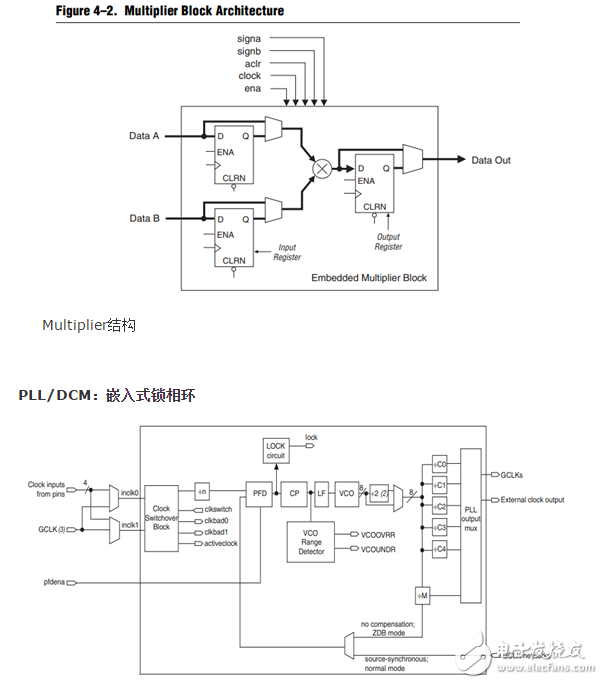

底层嵌入式功能块

主要是指PLL/DPLL、DCM、DSP48、乘法器、嵌入式硬核/软核;

Xilinx:DCM、DSP48/48E、DPLL、Multiplier等

Altera:PLL/EPLL/FPLL、DSPcore等;

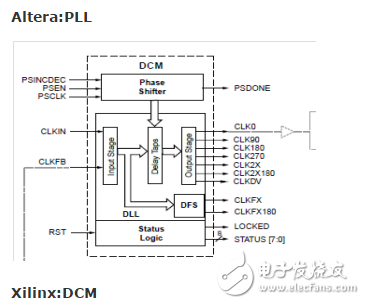

Altera的Cyclone II器件最多有四个PLL,分布在芯片四个角;需要主要的是Altera的PLL是模拟锁相环,在电源/地方面要做考虑。

Xilinx的spatan-3器件最多有四个DCM,也是分布在芯片四个角。

两者的区别:Altera的PLL可支持较低的输入频率,可Xilinx的DCM支持的最低锁相频率为24/32MHz;但Xilinx的高端器件Virtex-5的DPLL可达到很低的输入频率。

内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(Hard Core),等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:为了提高FPGA的乘法速度,主流的FPGA 中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。Xilinx公司的高端产品不仅集成了Power PC系列CPU,还内嵌了DSP Core模块,其相应的系统级设计工具是EDK和Platform Studio,并依此提出了片上系统(System on Chip)的概念。通过PowerPC、Microblaze、Picoblaze等平台,能够开发标准的DSP处理器及其相关应用,达到SOC的开发目的。

- 相关推荐

- 热点推荐

- FPGA

-

深入解析FPGA芯片结构2022-10-25 2913

-

深度解析CPLD和FPGA内部结构和原理2023-08-29 2848

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 4433

-

大家有全面转型使用国产FPGA的么?2024-03-06 4894

-

Labview 复杂结构体解析2013-09-11 7828

-

全面解析无线充电技术2016-07-28 3619

-

HDR显示技术全面解析2016-10-26 685

-

从原理到结构,全面解析中间继电器2016-11-04 5544

-

全面解析:PCB设计接地问题精要2016-12-15 965

-

全面解析多点触控技术2017-01-14 1037

-

数字设计FPGA应用:FPGA的基本逻辑结构2019-12-03 3009

-

解析操作系统的概念、结构和机制2021-03-26 775

-

ARM与FPGA的接口实现的解析2021-07-22 1018

-

电磁脉冲防护系统平台全面解析2025-04-27 781

-

电磁干扰抑制系统平台全面解析2025-08-11 851

全部0条评论

快来发表一下你的评论吧 !