修改时钟滤波器来改善全速测试效率的方法

射频/微波/无线测试

描述

为了追求以更低功耗和成本实现更高性能的目标,超大规模集成电路产业向系统级芯片(SoC)集成方向发展,从而导致了多时钟域设计的出现。最常见的是,当频率关系是2的整数倍时,共享相同时钟源的功能块具有同步交互性。从时序的角度看,这些交互可能经常发生在设计的关键路径。在这种情况下,你必须测试这些交互以查证过渡类型(transition-type)故障,以达到测试覆盖率和DPPM(百万分之一缺陷)目标。

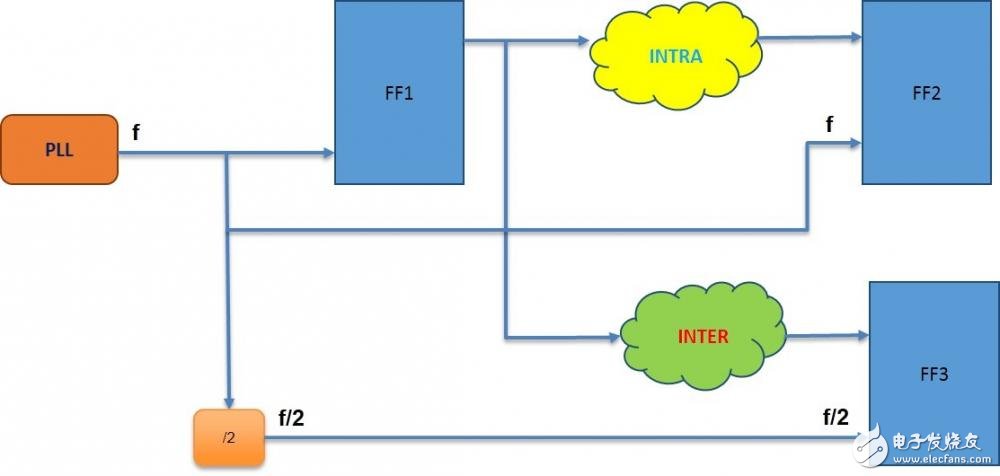

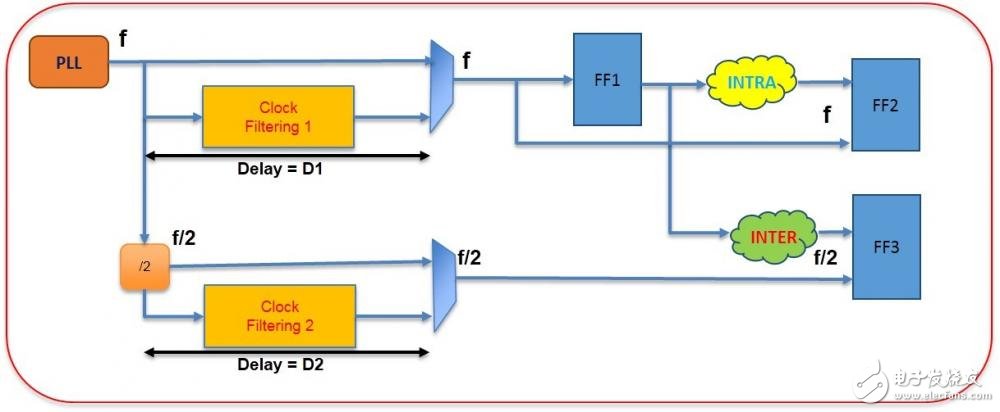

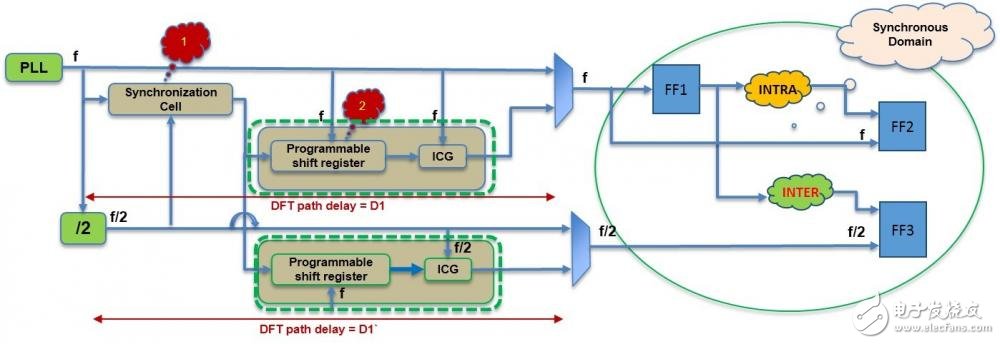

换句话说,在一个时钟域中具有发射触发器,并且在另一个同步时钟域中具有捕获触发器的路径被称为同步跨时钟域(SCCD)路径。如图1所示,FF1到FF2之间的组合云被称为内部时钟(intra-clock)域,而FF1到FF3之间的云被称为跨时钟(inter-clock)域。

图1:内部时钟域和跨时钟域路径可能会以延迟的形式引入故障。

用于过渡故障测试的时钟滤波电路(CFC)从时钟源滤除所需的时钟脉冲。典型的CFC具有局限性,不能用于测试跨同步时钟域的过渡故障。出现过渡错误时会出现什么问题?我们将解释这些限制,并建议对CFC进行改进、以使对SCCD的测试(如图1所示的跨时钟域故障)可行。

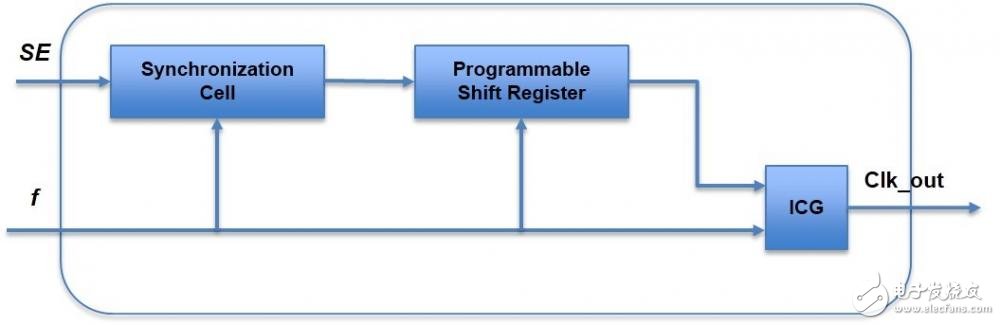

图2表示一个典型的时钟滤波电路,它有三个主要组件。

• 同步单元将扫描使能(SE)信号与工作时钟域同步。

• 由同步SE信号触发的可编程移位寄存器来控制集成时钟门控(ICG)以生成所需数量的时钟脉冲。

• ICG单元。

图2:典型的时钟滤波电路可能不足以测试跨同步时钟域的时钟故障。

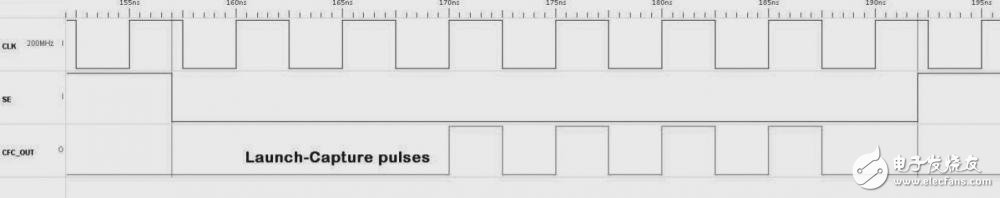

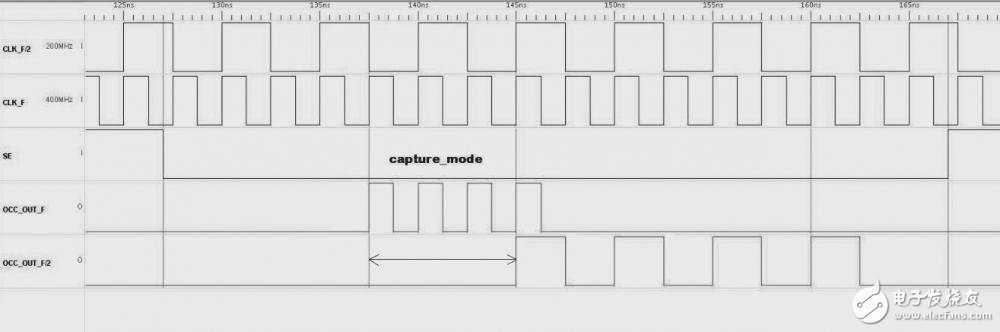

全速故障测试包括两个步骤。第一步是移位模式,第二步是捕捉模式。在移位模式,当SE为高电平时,经由扫描链移位,寄存器被初始化为已知值。在捕捉模式,当SE为低时,功能路径的响应被捕捉到寄存器中。

在捕捉模式,CFC用于产生所需的时钟脉冲,用于全速测试的启动和捕捉周期。

当SE被选通,经过一段延迟才到达CFC。然后在CFC中,与接收时钟域的两级同步单元同步。被SE同步的信号将触发n级可编程寄存器给ICG提供使能信号,以滤除所需的时钟脉冲。这意味着来自CFC的时钟脉冲距离从SE到达CFC那一刻已有一定延迟。延迟主要由同步单元延迟造成。

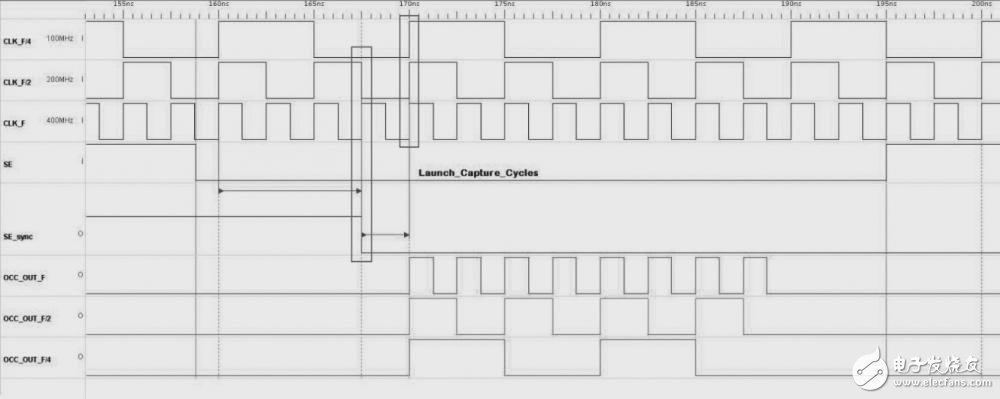

图3:全速测试时钟的典型CFC输出波形。

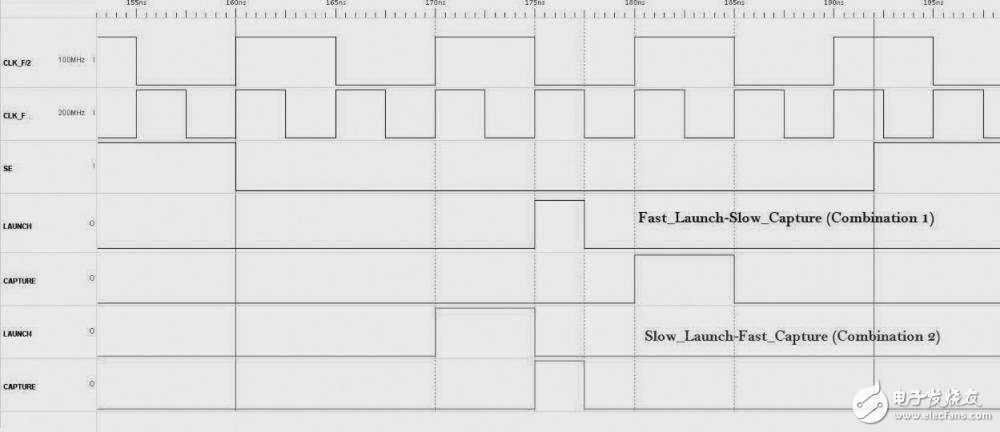

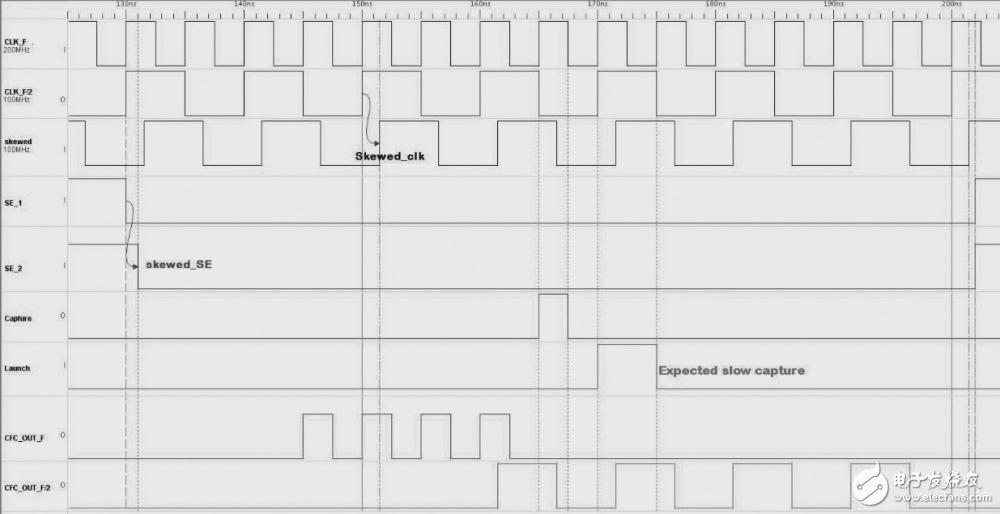

为测试时钟域内的故障(内部时钟域故障),该CFC尽职尽责,如图3所示。但是,要测试SCCD过渡故障,需要产生启动和捕获脉冲,如图4所示。为获得这种波形,我们通常使用两个独立的CFC。每个时钟域都需要自己的CFC,因为每个时钟的脉冲宽度都不相同,因此需要从不同的CFC生成。图4给出了你可以实现的不同启动和捕获条件的示例。

图4:用于测试跨时钟域故障的典型启动和捕获脉冲组合,包括快速启动和慢速捕获以及慢速启动和快速捕获脉冲。

当用于测试同步复时钟域(图1)中的故障时,同一个CFC遇到以下挑战:

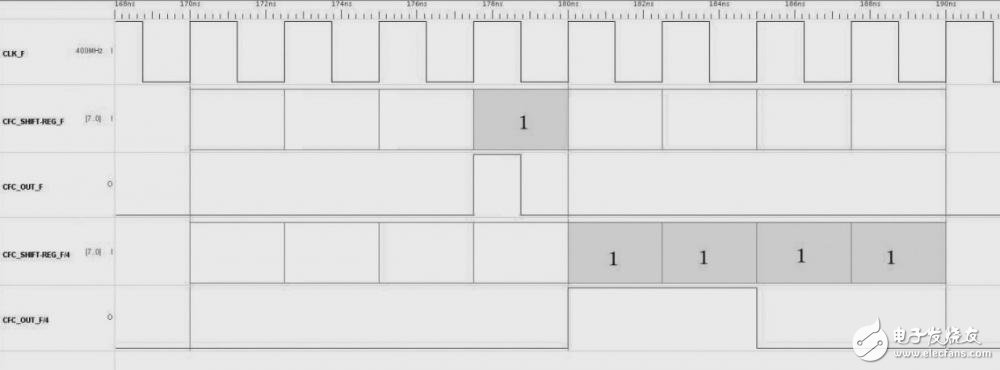

***边缘失齐***:当测试两个SCCD之间的故障时,每个时钟域都有自己的CFC。而由于CFC固有的同步延迟会导致输出错位。产生的时钟边缘将不会是周期对齐的。例如,假定频率为F和F/2的两个同步时钟,每个都具有移位寄存器长度为4的可编程CFC。可编程移位寄存器在不同时间被触发,从而导致CFC输出的不同延迟。假定为两级同步器,则时钟域F/2需要两倍于时钟域F的时间。图5显示了两个CFC的时钟输出波形。需要注意的是,有两种类型的错位失齐。一种是由于同步本身的延迟,如图5所示。

图5:通用CFC输出的时钟波形,显示失齐的边沿。

失齐的另一个原因是时钟偏斜(clock skew)。每个时钟的偏斜都导致两个CFC时钟输出失齐的进一步加剧。如图6所示,CFC_OUT_F的输出相对于CFC_OUT_F/2是偏斜的。正因为如此,捕获发射信号的功能时序窗口被压缩,损害了测试质量和有效性。

图6:时钟偏斜可导致边缘失齐。

***丢失时钟脉冲***:图4显示了在跨时钟域故障的全速测试中所需的启动和捕获脉冲的子集。参考图5,可以推断,对于具有长度为4的可编程移位寄存器的CFC来说,它不能命中发射和捕获脉冲的所有组合。例如,发射和捕获脉冲的第一个组合(在图4中)可以使用这两个CFC来创建,但第二个组合不能。可通过增加移位寄存器的长度来解决该问题。

如图4所示,为成功测试SCCD路径,需要两个启动和捕捉脉冲组合。脉冲应该由时钟时序窗口分开。但由于时钟偏斜和同步单元延迟,这很难实现。

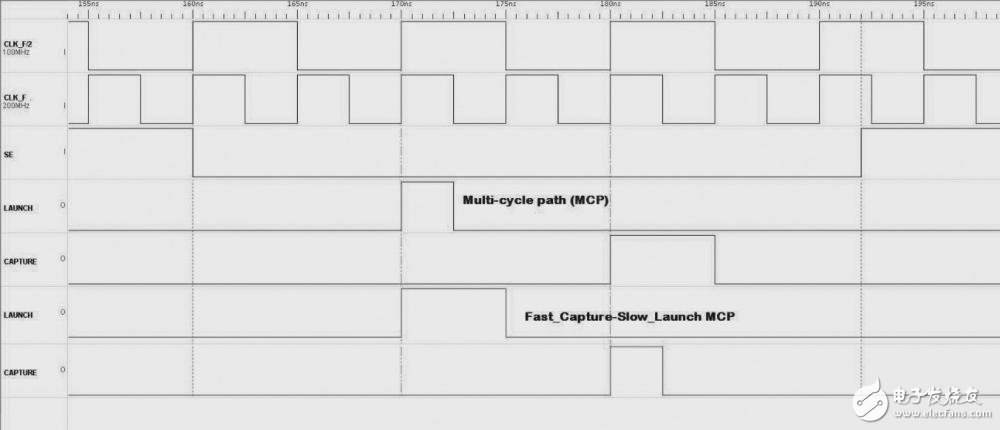

***多周期路径(MCP)测试***:由于与时钟脉冲丢失有关的问题,测试受移位寄存器长度的限制。移位寄存器的长度不足以捕获所有的启动和捕获组合,并且这在MCP中变得更严重,因为你必须等待一个时钟周期来脉启(pulse)另一个。可编程的移位寄存器应该有足够的宽度来创建所需的MCP启动并捕获脉冲和测试路径。图7显示了MCP的两种情况。同样,对CFC来说,只有第一个条件是可能的,而第二个不行,因为它是基于通用CFC脉冲产生的。

图7:多周期路径需要足够长的移位寄存器来产生有效启动。

***物理实现和STA挑战***:如图8所示,D1和D2之间的延迟差异需要尽可能接近。小的差异确保两个时钟之间的时钟偏斜在测试条件下与在功能条件下看到的时钟偏斜相似。设计者应提供额外的物理和时序约束来实现小差异。例如,你可以使用SDC使能D1和D2路径之间的时钟平衡。

图8:最小化D1和D2之间的差异以减少时钟偏斜。

***范式生成***:即使对于可测条件,设计者也需要在可编程移位寄存器中找到正确的位序列来实施约束。基于这些值,CFC将为单周期路径和多周期路径生成正确的启动和捕捉脉冲序列。

用于测试跨时钟域过渡故障的时钟滤波电路应确保以下几点:

• 同步时钟域的CFC应同时触发,以产生对齐的时钟脉冲。

• 电路应提供选择所需精确脉冲对的灵活性,以实现启动和捕获的任意组合。

• 电路应该是时序友好和便于实现的。

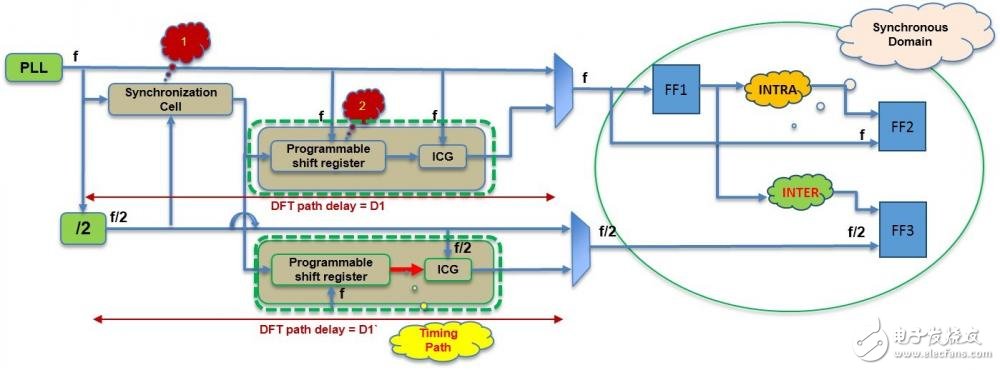

图9显示了我们在OpenSilicon中使用的一个修改后的CFC。

图9:CFC修改包括可编程移位寄存器和一个分离同步单元。

***公用同步单元***:从CFC中取出同步单元,并与所有SCCD CFC公用。这样做可以确保对可编程移位寄存器的触发同时到达。单独的单元消除了由于同步单元延迟差异而导致的边缘失齐。

如图10所示,要实现带对齐上升沿的输出时钟脉冲,你应该在SCCD最快时钟的前一个边沿处生成同步SE。你可以通过同步单元中多个SCCD时钟的组合来实现。为了以最小的逻辑来实现上面的对齐,在同步单元中使用最慢和最快的SCCD时钟。

图10:有效的SE同步沿产生所有SCCD时钟的正确对齐。

***移位寄存器时钟***:SCCD CFC的可编程移位寄存器被修改为以该SCCD的最快时钟频率工作。这在该SCCD的最快时钟(f)和工作时钟(f/2)之间创建了一条时序路径,如图11所凸显。通过在时钟树综合(CTS)阶段严格地限制时钟偏斜,该修改简化了物理实现和静态时序分析(STA)。它还使对物理实现和STA的额外限制不再必要。

图11:SCCD时序路径包含一个同步单元和可编程移位寄存器。

***移位寄存器宽度***:由于移位寄存器的工作频率高于CFC的工作频率,因此需要增加其宽度。例如,要产生四个f/2时钟脉冲,移位寄存器的长度应为8,因为它工作在频率f。移位寄存器的宽度取决于给定SCCD中最快时钟与最慢时钟频率之比。下面的公式表示可改变移位寄存器宽度的参数:

例如,如果同步时钟域的频率为f、f/2和f/4,为最多实现四个时钟脉冲,则移位寄存器宽度应该是:

因此,你需要一个以最快时钟f工作的16位宽移位寄存器。

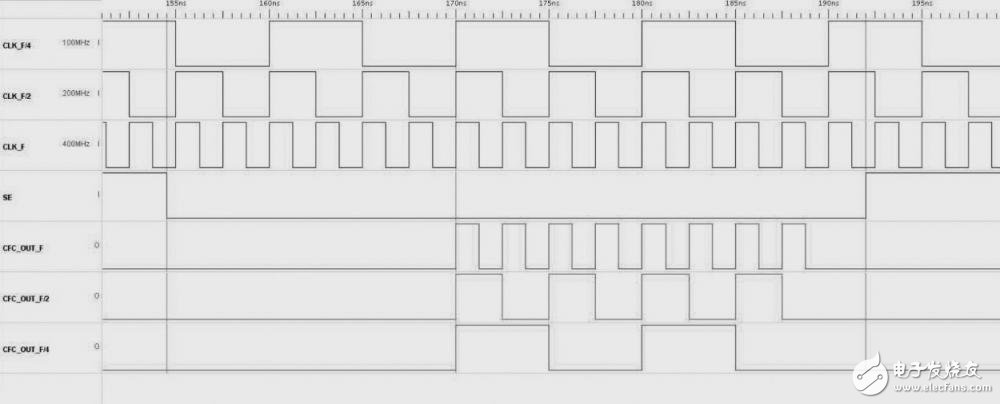

图12描绘了F、F/2和F/4三个不同时钟的SCCD CFC输出时钟脉冲。使用可编程移位寄存器,你可以配置CFC以生成所需的启动和捕捉时钟脉冲。

图12:同步时钟域中的CFC输出显示了所有时钟沿都对齐、没有任何延迟。

在图5,我们表明,使用典型的CFC,不能产生用以测试跨时钟域故障的启动和捕获时钟脉冲的所有组合。使用增强型CFC,你可以生成所有可能的启动和捕获脉冲组合,包括MCP测试所需的组合。

***范式生成***:增强型CFC的范式生成涉及将移位寄存器的位编程为与所需的启动和捕获脉冲相对应的值。使用增强型CFC,可编程移位寄存器工作在最快的时钟来获得一个时钟脉冲。因此,你需要约束移位寄存器内的多个位。

假定频率为f/4的工作时钟和频率为f的可编程移位寄存器时钟。需要对移位寄存器的四个位进行编程,以生成一个f/4工作时钟频率的脉冲(图13)。此外,使用命名捕获程序(NCP)自动测试范式生成(ATPG)方法来运行故障模拟。

图13:两个CFC的可编程移位寄存器位值可生成一个启动和捕捉组合。

设计结果

在Open-Silicon,这种增强型CFC已经在设计中实现,实现了1.07%的全速覆盖提升。虽然该数字本身可能看起来很小,但这些故障覆盖了必须要测试的关键路径。

结论

在包含多个时钟的复杂SoC中测试SCCD故障并不容易,但对于提高良率非常重要。为克服这些挑战,本文提出了一种修改现有CFC以实现更高覆盖率的新方法。采用这种方法,可以在不影响任何设计进度和复杂性的前提下,只对原初的CFC进行微小更改、就实现了一款强健的CFC。测试这种同步跨时钟域的故障可以让设计人员实现更高的全速测试覆盖率和低的DPPM目标。 这也有助于集成电路(IC)部件的筛选,并给速度分拣(speed binning)带来额外好处。

这种测试方法为系统工程师推出成功产品提供了更强信心,特别是在设计包含许多这样的SCCD路径的情况下。

-

实测演示|ATECLOUD-滤波器测试代替手动测试,效率提升50%#电子工程师 #滤波器 #软件测试namisoft 2023-03-10

-

基于AccelDSP的自适应滤波器设计2010-04-24 0

-

共模电感滤波器设计2015-08-03 0

-

LC滤波器设计和制作方法的实用工具书:LC滤波器设计与制作PDF2017-08-03 0

-

鉴相频率的杂散与环路滤波器的布线怎么改善杂散2018-11-07 0

-

基于芯片测试的外围环路滤波器设计2019-07-05 0

-

如何用FPGA来实现滤波器的设计2021-07-30 0

-

LC滤波器设计与制作2021-08-06 0

-

stm32F4修改时钟的方法和stm32F103修改时钟的方法不一样2021-08-12 0

-

电源EMI滤波器的设计方法2022-06-07 0

-

陶瓷滤波器介绍及测试方法2010-01-13 3235

-

有源带通滤波器电路的设计步骤及仿真分析和测试方法2022-03-23 12293

-

如何修改时钟频率2022-02-08 2989

-

stm32F4修改时钟频率,更换为8MHz晶振2021-12-27 1232

-

基于ATECLOUD平台|频谱分析仪自动化测试滤波器工作频率,效率提升50%2023-04-25 737

全部0条评论

快来发表一下你的评论吧 !