一种基于FPGA的十字路口交通灯系统控制的设计

控制/MCU

描述

交通灯通常指由红、黄、绿三种颜色灯组成用来指挥交通的信号灯。绿灯亮时,准许车辆通行,黄灯亮时,已越过停止线的车辆可以继续通行;红灯亮时,禁止车辆通行。

十字路口车辆穿梳,行人熙攘,车行车道,人行人道,有条不紊。那么靠什么来实现这井然秩序呢?靠的是交通信号灯的自动指挥系统。交通信号灯控制方式很多,本文设计一个十字路口交通灯控制电路,要求东西、南北两条干道的红、绿、黄交通灯按要求循环变化,并以倒计时方式指示干道通行或禁止的维持时间。并在FPGA实验板上实现所设计电路的功能。

1、系统概述

1.1、设计思想

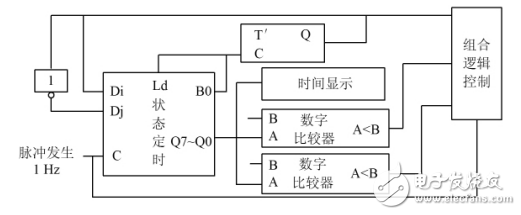

基于FPGA的交通灯系统控制设计包括4大模块,分别为脉冲发生、状态定时、交通灯闪烁的控制、闪烁时间的控制,基本原理如图1所示。

图1 交通灯控制电路参考原理图

1.2、总体工作情况

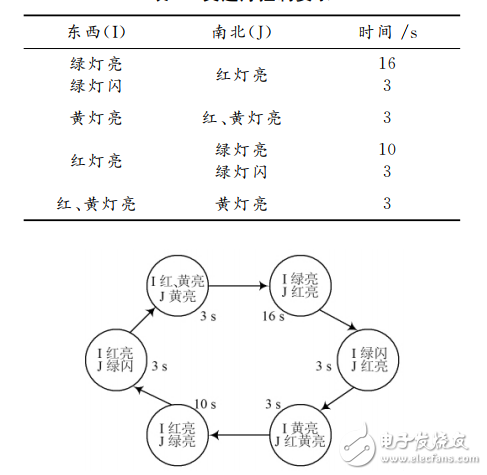

交通灯控制要求如表1所示。

该设计的交通灯控制分为6个状态。由于各状态持续时间不同,所以电路的核心控制部分是状态机和定时器,状态机在定时器触发下周期性循环,状态码控制6个灯以一定的规律变化。变化情况如图2所示。

表1交通灯控制要求

图2电路状态转换图

系统脉冲由FPGA开发板晶振经过分频电路实现。状态定时由74190可逆十进制计数器和T’触发器实现,只要置数合理,翻转信号到位,就可以使电路在东西(I)、南北(J)两个控制状态间翻转。红、黄、绿灯的闪烁由7485数字比较器和组合逻辑控制,其中7485数字比较器用于比较计数器当前持续状态和所需要的状态全部时间,并做出相应的变化。组合逻辑控制由AHDL文件编写真值表实现。时间显示由AHDL文件编写真值表实现,输入正确的逻辑,七段译码电路即能得到正确的时间显示。

1.3、各功能的组成

整个电路可以分为4大部分,包括脉冲发生、状态定时、时间显示和数字比较一组合逻辑控制。

1.3.1、脉冲发生

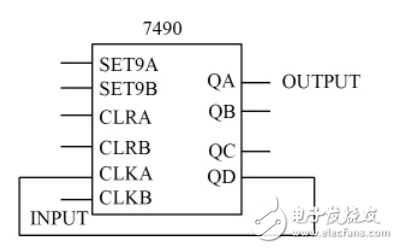

脉冲发生器为整个系统提供驱动,将输入端分配给FPGA实验板的PIN55引脚,则会由实验板上产生频率为10MHz的输入脉冲,用7片7490,每一级都构成10分频电路,使频率从10MHz降低为1Hz。

1.3.2、状态定时

状态定时可由预置BCD码初值的74190级联实现,构成减计数器。级联原则是:低位计数器从全0状态变为最大码值状态时可使高位计数器减1。级联方式分为异步和同步两种,本文采取的是异步级联方式,即低位计数器溢出信号控制高位计数器的记数脉冲输入端。可根据计数器的时钟触发方式,在低位计数器状态码从全“0”变为最大码值的瞬间,为高位计数器提供有效的计数脉冲边沿。具体做法是将低片位的溢出信号RCON端口接到高片位的计数脉冲CLK,实现两位BCD码的置数、翻转和借位,使系统表示的数字能在22~16之间循环。

74190功能说明:

(1)GN为计数器使能控制端,低电平有效。当GN为高电平时,禁止计数。

(2)DNUP为计数方式控制,接高电平为减计数,接低电平为加计数。

(3)LDN为异步预置数控制。当LDN为低电平时,计数器状态QD,QC,QB,QA分别等于D,C,B,A。

(4)计数器位序由高至低顺序为QD,QC,QB,QA。QD为最高位MSB,QA为最低位LSB。

(5)计数脉冲CLK上升沿有效。

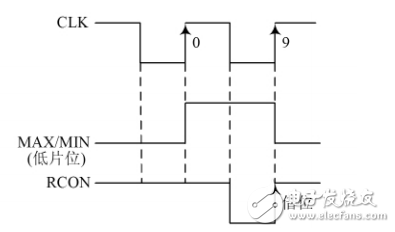

(6)当计数器输出QDQCQBQA为十进制加计数的最大状态码“1001”或为减计数的最小状态码全“0”时,极值状态码指示MAX/MIN输出为高电平。

(7)当极值状态码指示MAX/MIN为高电平且CLK为低电平时,溢出信号RCON为低电平,即RCON与计数脉冲同步。

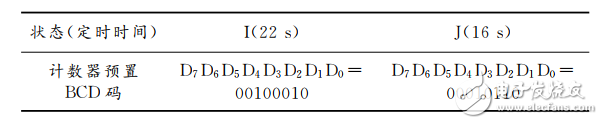

系统记数脉冲为1Hz时,如表2所示,当I状态(东西控制状态)的定时时间为22s,计数器应该先预置22的BCD码;同理,J状态(南北控制状态)之前应该预置16的BCD码。

表2定时计数器各状态预置数

图3 7490十分频电路

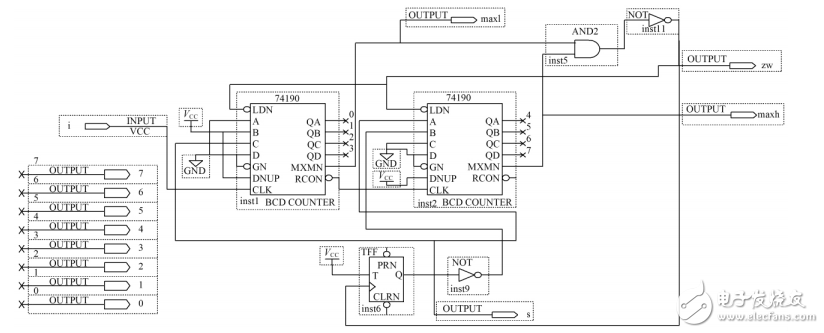

状态计时电路由两片74190级联而成,构成22和16自翻转的电路。其要解决的核心问题包括置数,翻转和借位。根据74190芯片的特点,可分析其实现原理如图4所示,通过溢出信号RCON的上升沿实现借位,使得数字能够从20到19,个位向十位借位,顺利过渡。

图4 74190借位原理

置数和翻转之间有先后关系,即须先置数后翻转。如表3所示,分析两个BCD码各位特点,可知两者D7D6D3D0位均为1,D1位均为0,而D5D4D2位不同,如图5,D5D4D2位由状态电平S来控制,当为I状态时,计数器的预置的数为D5=0,D4=D2=1,而为J状态时,计数器的预置的数为D5=1,D4=D2=0,根据74190的功能,将2片74190的MAX/MIN引出,通过与非门,分别连在高位和低位的LDN置数端,通过分析可知,当计数器从01减到00时候,高低位的MAX/MIN均为高电平,经过与非门以后为低电平,74190被置数,其置数值由状态S来决定,S是由LDN端信号经

过一个T’触发器决定的,即LDN信号每置数一次,S翻转1次,从而区分16和22状态。按这个结构,可分别置数16和22,使其实现自翻转。

图5为状态定时模块的实际连接图。

图5 状态定时模块的实际连接图

1.3.3、时间显示

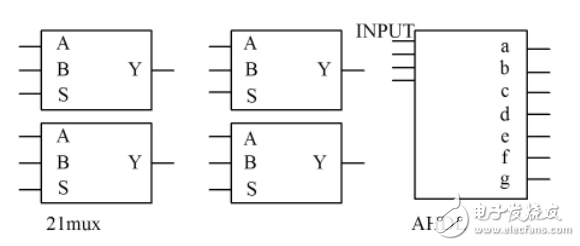

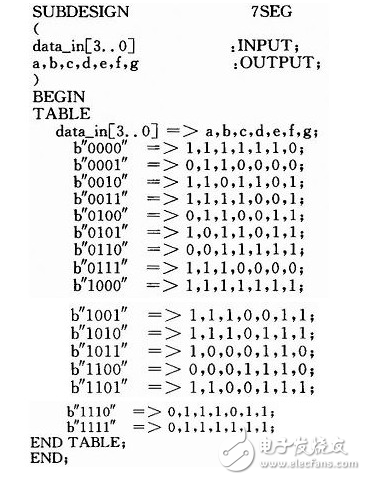

时间显示要用到7段显示译码电路,由于是两位BCD码,故用二选一数据选择器。选择端S接一个频率很高的方波(如1kHz);数据比较器的输出和1Hz脉冲作为AHDL模块的输入,即可正确显示时间。

图6 段显示译码电路

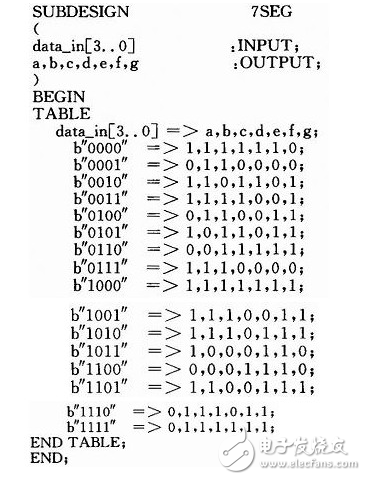

为正确显示时间,用AHDL文件自编译码真值表如下:

1.3.4、数字比较一组合逻辑控制

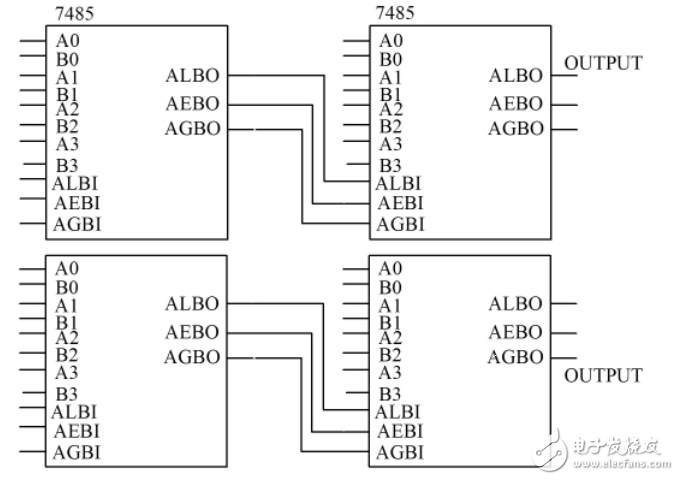

该模块将状态定时模块输出的时间与时间节点进行比较,从而确定电路处于22s或者16s的具体的某个状态。由表1可知,东西(I)或南北(J)的控制状态都有3个阶段的控制逻辑,分别对应3个时间段:1~3s,4~6s和大于6s,因此,采用数字比较器进行比较,确定定时值小于4s或大于6s,方法如图7所示,采用4片7485数字比较器,两两级联,其中一个由状态定时模块的输出与4即二进制0100比较;另一个由状态定时模块的输出与6即二进制0110比较。

图7 7485级联构成的两个8位数字比较器

编写组合逻辑真值表,将状态信号S,两个数字比较器的输出Y1,Y2和1Hz脉冲作为输入,各个灯的状态作为输出。从而根据逻辑关系得出对应时间电路的状态,控制红、黄、绿灯处于不同的状态。S判断电路处于22s状态还是16s状态,Y1,Y2区分东西、南北六个阶段状态,1Hz脉冲实现绿灯闪烁。

2、电路的组构与调试

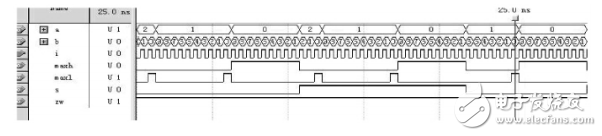

来用QuartusⅡ软件设计各个模块,并进行仿真。确认结果后,下载至FPGA实验板中,进行相应的硬件调试,调试结果与仿真结果相一致。图8为仿真波形,系统上电需要调整的过程,因此电路正常工作前重复了22s的状态。

图8 状态定时模块仿真波形

3、结语

本文利用QuartusⅡ软件环境下进行了编译及仿真测试,通过FPGA芯片实现了一个实用的交通信号灯控制系统。由于设计采用了EDA技术,提高了设计的效率和精确度。

-

十字路口的交通灯控制电路设计1.doc2013-05-16 0

-

请问labview中如何控制循迹小车检测并通过十字路口2018-08-19 0

-

有偿求助十字路口的交通灯2019-04-28 0

-

有偿求助,急急急基于FPGA的交通灯智能控制2019-04-28 0

-

51单片机的仿真实验——交通灯(十字路口演示)精选资料推荐2021-07-15 0

-

主要介绍十字路口红绿灯路口的单片机程序设计2021-12-01 0

-

基于单片机的十字路口交通灯控制器设计2023-09-20 0

-

十字路口交通灯控制2008-09-29 21507

-

plc控制十字路口交通灯2017-04-18 2187

-

基于单片机的十字路口交通灯控制系统设计2015-11-13 1172

-

十字路口交通灯控制设计2016-03-14 615

-

十字路口交通灯控制电路的设计2016-05-19 1448

-

AT89c52的十字路口交通灯2016-07-08 992

-

基于PLC的十字路口智能交通灯控制系统的设计2018-01-08 29918

-

基于51单片机的十字路口交通灯系统2021-11-04 700

全部0条评论

快来发表一下你的评论吧 !