分享STM32定时器输出比较模式的理解

电子说

描述

初学STM32,我这个地方卡了很久,现在终于有些明白了,现在把我的理解写下与大家共享,如果有不对的地方,还请指出。

TIM_OCMode选择定时器模式。该参数取值见下表:

TIM_OCInitStructure.TIM_Pulse = CCR1_Val; //设置跳变值,当计数器计数到这个值时,电平发生跳变

TIM_OC2PreloadConfig(TIM3, TIM_OCPreload_Enable); //使能TIMx在CCR1上的预装载寄存器 TIM_ARRPreloadConfig(TIM3, ENABLE); //使能TIMx在ARR上的预装载寄存器

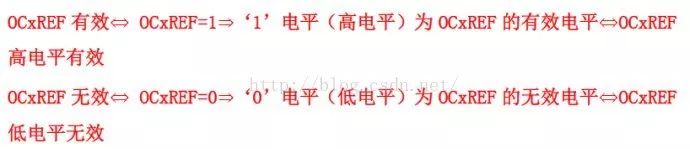

OCxREF就是一个参考信号,并且约定:OCxREF=1,称OCxREF有效。反之,OCxREF=0,称OCxREF无效; ‘1’电平(高电平)称为OCxREF的有效电平,‘0’ 电平(低电平)称为OCxREF的无效电平。——依据参考手册:The output stage generates an intermediate waveform which is then used for reference:OCxRef (active high). The polarity acts at the end of the chain.(翻译)输出阶段产生一个中间波形OCxRef(高有效)作为参考。输出信号的极性体现在信号链的末端。

现在解释几个名词之间的关系:

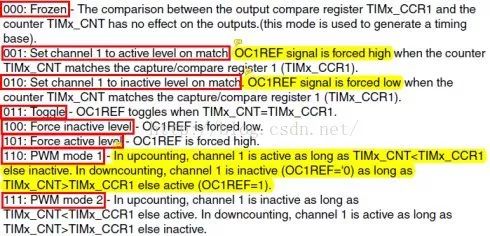

然后来理解输出比较的几个模式(PWM模式是输出比较模式的特例)查看TIMx_CCMR1寄存器的OC1M域,有如下定义(摘自最新版的参考手册

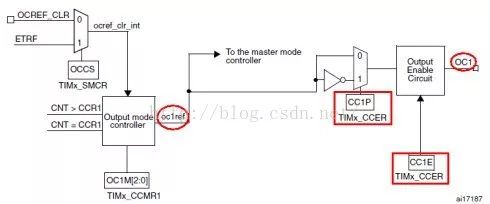

翻译如下:000:冻结——输出比较寄存器TIMx_CCR1中的内容与计数器TIMx_CNT中的内容之间的比较对输出无影响。(此模式用于时基的生成)001:当匹配时,设置通道1为有效电平。当计数器TIMx_CNT中的内容与捕捉/比较寄存器1(TIMx_CCR1)中的内容相匹配时,强行拉高OC1REF 信号。010:当匹配时,设置通道1为无效电平。当计数器TIMx_CNT中的内容与捕捉/比较寄存器1(TIMx_CCR1)中的内容相匹配时,强行拉低OC1REF 信号。011:翻转——当TIMx_CNT= TIMx_CCR1时,OC1REF信号取反。100:强制无效电平——强行拉低OC1REF 信号。101:强制有效电平——强行拉高OC1REF 信号。110:PWM模式1——向上计数模式中,只要TIMx_CNT< TIMx_CCR1,通道1有效,反之无效。向下计数模式中,只要TIMx_CNT> TIMx_CCR1,通道1无效(OC1REF=0),反之有效(OC1REF=1)。110:PWM模式2——向上计数模式中,只要TIMx_CNT< TIMx_CCR1,通道1无效,反之有效。向下计数模式中,只要TIMx_CNT> TIMx_CCR1,通道1有效,反之无效。我用红色标出了提到有效、无效的地方。不难发现,有效与无效分别对应OC1REF=1和OC1REF=0。这正是我们先前约定的结果。到此,不同模式下输出比较的结果对OC1REF信号的影响已经很清楚了,但是最终的输出信号是OC1,并不是OC1REF。而且前面有一句话(输出信号的极性体现在信号链的末端)还未做解释。到底OC1REF与OC1之间有何秘密呢?我们来看下面这个图:

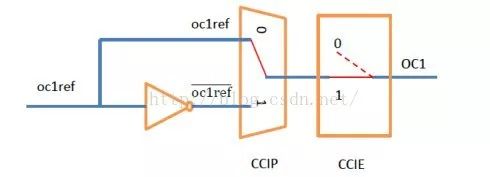

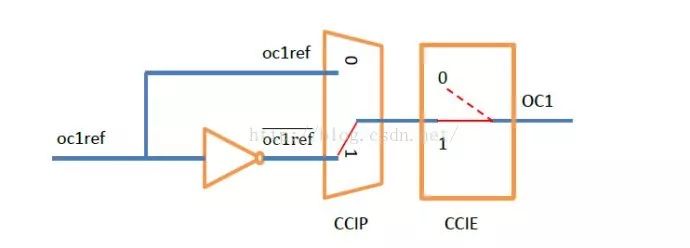

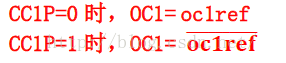

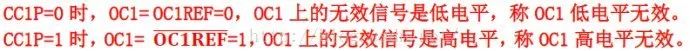

显然,我们只关心红色圈内的信号与方框内的寄存器位以及信号在它们之间是如何传播的。oc1ref从输出模式控制器(Output mode controller)开始,分为两路,上面一路至主模式控制器(To the master mode controller),这里我们不关心它的去向,我们关心的是下面一路,下面一路在进入双路开关之前又被分成了两路——一路是原信号,一路是原信号的非。显然TIMx_CCER中的CC1P位用来控制这个开关,CC1E位控制着整条信号链的通断。当CC1P=0时(CC1E=1):

当CC1P=1时(CC1E=1):

很显然,OC1与OC1REF的关系只受CC1P的影响(CC1E=1)

然而参考手册上对CC1P位是这么描述的:

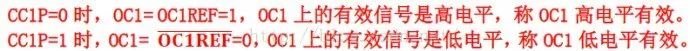

CC1P=0时:OC1高电平有效CC1P=1时:OC1低电平有效根据本文开篇的名词解释,可以这么理解:CC1P=0时:OC1有效电平是高电平CC1P=1时:OC1有效电平是低电平这时就迷惑了,这个高电平有效和低电平有效是啥意思呢?我们从头分析(整个过程CC1E=1,OC1的输出是允许的):①假定OC1REF有效(OC1REF=1),那么从OC1REF到OC1的整条信号链上的信号都是有效信号,我们称OC1输出了有效信号。那这个有效信号是高电平还是低电平呢?这就是由CC1P决定的:

②假定OC1REF无效(OC1REF=0),那么从OC1REF到OC1的整条信号链上的信号都是无效信号,我们称OC1输出了无效信号。无效信号的高电平和低电平也是由CC1P决定:

| OC1REF | CC1P | 功能 | OC1 | 描述 |

| 0 | 0 | OC1高电平有效 | 0(低电平) | 无效 |

| 1 | OC1低电平有效 | 1(高电平) | 无效 | |

| 1 | 0 | OC1高电平有效 | 1(高电平) | 有效 |

| 1 | OC1低电平有效 | 0(低电平) | 有效 |

显然,OC1REF决定了OC1输出电平是否有效,而CC1P决定了有效电平的极性。我们抽出上表的后四列

| CC1P | 功能 | OC1 | 描述 |

| 0 | OC1高电平有效 | 0(低电平) | 无效 |

| 1 | OC1低电平有效 | 1(高电平) | 无效 |

| 0 | OC1高电平有效 | 1(高电平) | 有效 |

| 1 | OC1低电平有效 | 0(低电平) | 有效 |

我们将表按1、2列合并:

| CC1P | 功能 | OC1 | 描述 |

| 0 | OC1高电平有效 | 0(低电平) | 无效 |

| OC1高电平有效 | 1(高电平) | 有效 | |

| 1 | OC1低电平有效 | 0(低电平) | 有效 |

| OC1低电平有效 | 1(高电平) | 无效 |

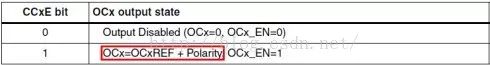

现在很清楚了,从上表中可以清楚地看到CC1P对OC1有效极性的控制。即,OC1的极性只有与CC1P指定的有效极性一致,OC1才能是有效的(绿色部分)。这样就解释了“输出信号的极性体现在信号链的末端”这句话。然而这条链还未结束,还有个CC1E呢。当然,它就是一个OC1输出使能位而已。但细心的你可能会发现,参考手册上对CC1E位有这样的描述:

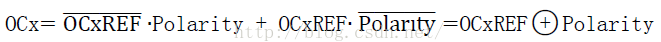

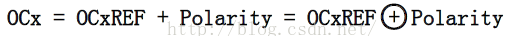

OCx = OCxREF + Polarity这个式子告诉我们OCx与OCxREF和Polarity(极性,即CCxP位)的关系。我们上面提到了它们的关系,是分了两种情况(CC1P=0和CC1P=1)表示的,这个式子帮我们将上面关系归纳成了一个。这个式子怎么得来的?回忆一下数字电路里面的半加器(就是不进位的加法),真值表如下:

| OCxREF | Polarity | OCx |

| 0(无效) | 0(高有效) | 0(无效) |

| 0(无效) | 1(低有效) | 1(无效) |

| 1(有效) | 0(高有效) | 1(有效) |

| 1(有效) | 1(低有效) | 0(有效) |

我们写逻辑函数(按黄色部分写):

注意:前面的“+”号表示半加运算(不进位加法),其实是逻辑上的“异或”。

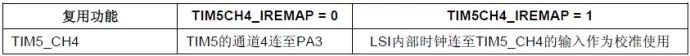

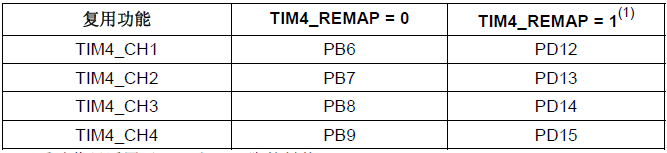

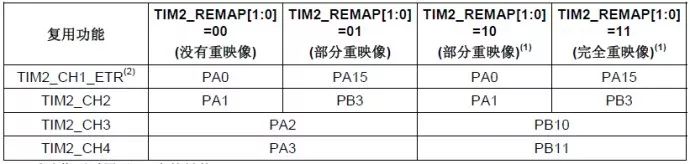

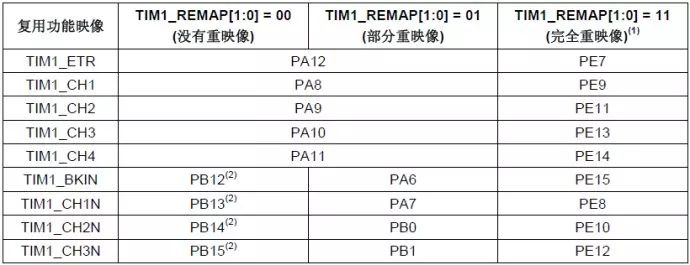

OC1连接到TIMx_CH1上,而TIMx_CH1是复用的。可在参考手册上定时器功能复用部分找到。下面给出一些定时器功能复用的表格:

-

STM32定时器输出一路PWM2021-08-04 0

-

STM32的通用定时器和高级定时器功能2021-08-18 0

-

STM32定时器比较输出相应的输出特征是什么2021-11-23 0

-

怎样去实现STM32通用定时器的输出比较模式呢2021-11-24 0

-

STM32通用定时器的输出比较功能2021-12-01 0

-

关于定时器输出比较模式中的电平理解2022-01-06 0

-

浅谈stm32定时器应用中的2个疑问2019-01-28 4057

-

单片机 | STM32定时器比较输出切换模式之应用实例2019-06-04 7007

-

[STM32]通用定时器的使用2021-11-22 713

-

STM32-通用定时器-PWM输出2021-11-26 1128

-

STM32F4单定时器独立输出四路PWM脉冲2021-11-30 737

-

STM32定时器单脉冲输出模式2021-12-08 1244

-

【捕获比较模式】msp430定时器比较捕获理解2021-12-16 457

-

STM32定时器的几种输出模式2023-01-12 4549

-

总结一下定时器的几种输出比较模式2023-07-21 4170

全部0条评论

快来发表一下你的评论吧 !