16进制计数器设计方案汇总(四种电路设计原理图及仿真程序分享)

应用电子电路

描述

本文为大家介绍四个16进制计数器设计方案。

16进制计数器设计方案一:16进制同步加法计数器

设计要求

(1)利用触发器和逻辑门电路,实现从0-15的加法进制

(2)利用触发器和逻辑门电路,实现串行序列发生器的设计(信号序列为00010011)。

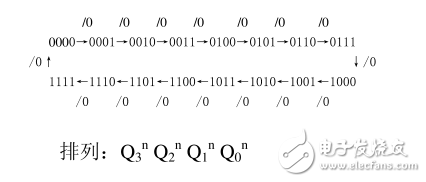

状态图

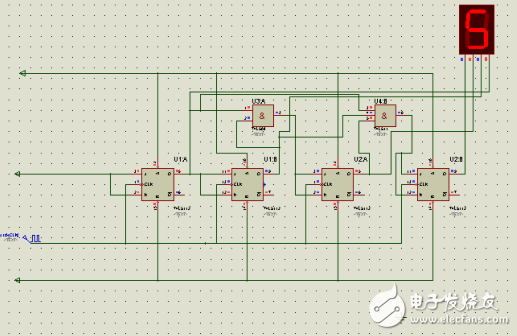

设计的逻辑电路图

16进制同步加法计数器电路图

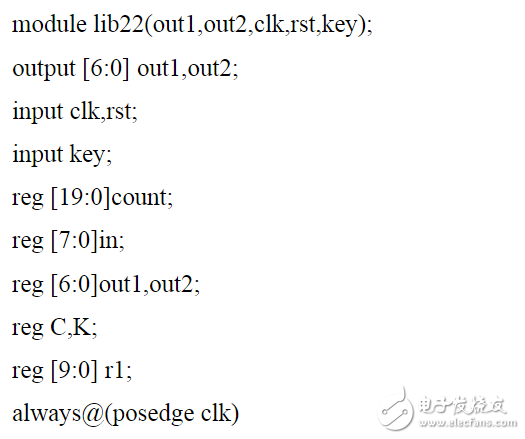

16进制计数器设计方案二:用Verilog HDL设计2位16进制计数器

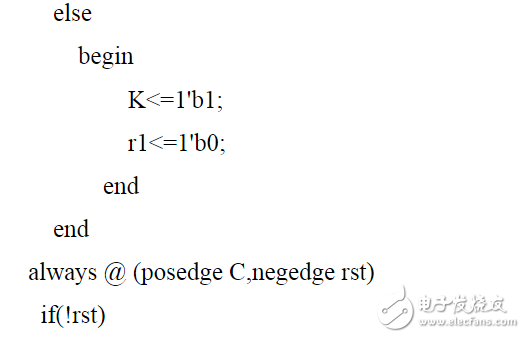

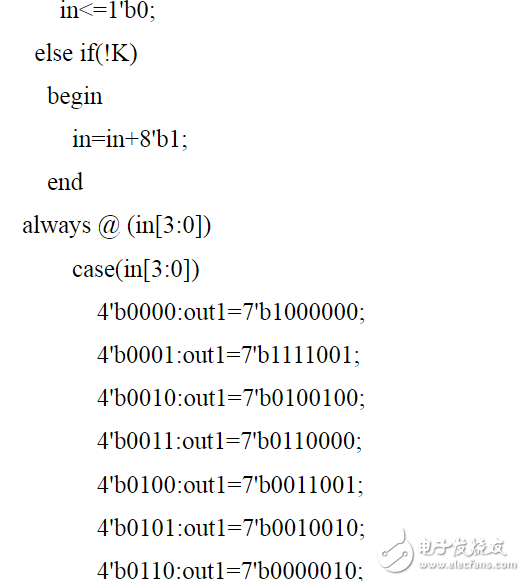

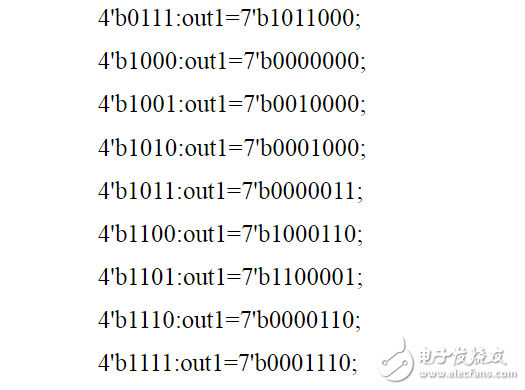

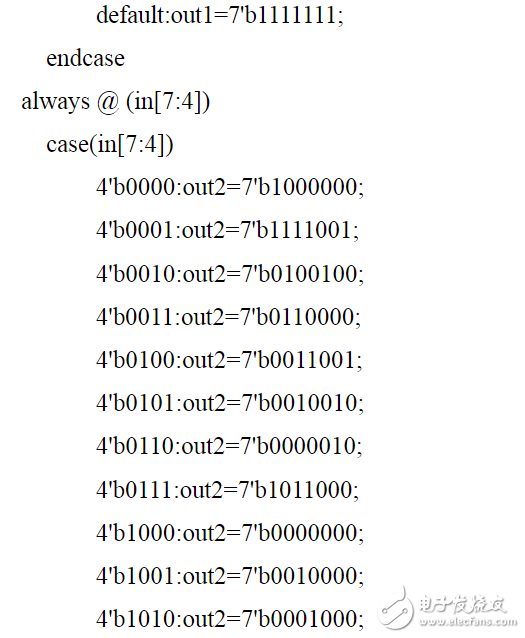

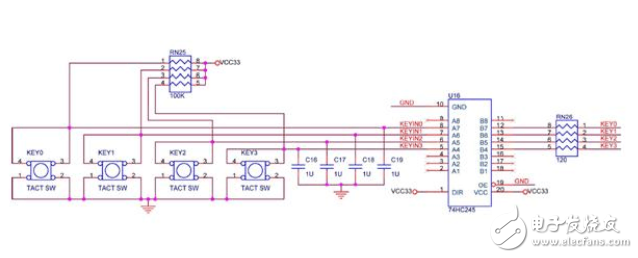

用Verilog HDL设计2位16进制计数器,由DE2的KEY0输入计数值,在HEX1,HEX0上显示计数值。

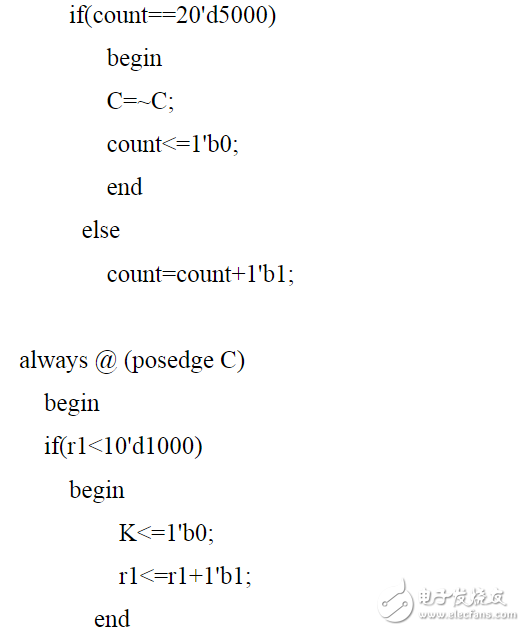

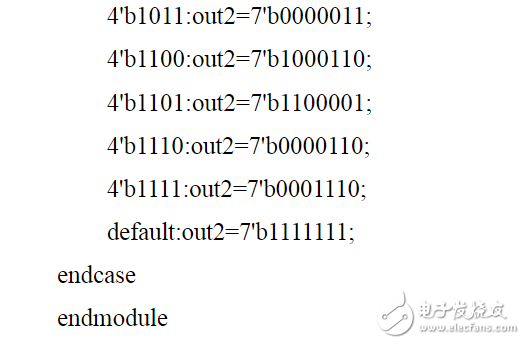

程序代码

DE2按键电路图

16进制计数器设计方案三:用触发器设计16进制计数器

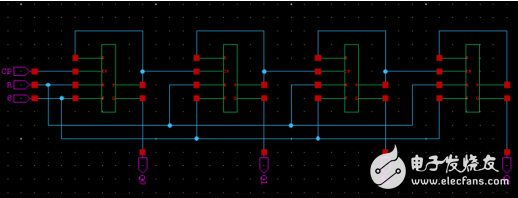

首先是将每个D触发器的P端与D端相连,构成T触发器,然后连接电路,计数器的计数脉冲输入端为CP,全部清0端为R,全部置1端为S,输出端由低位到高为分别为Q0、Q1、Q2、Q3。电路图如下。

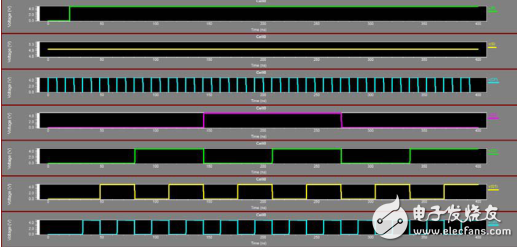

仿真波形

CP输入单位时间脉冲,R在第一个时钟脉冲置0,在以后的周期内都置高电平1,S在所有的时钟周期内都置1,然后仿真。其仿真波形截图如下图。

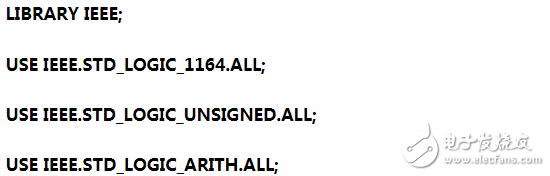

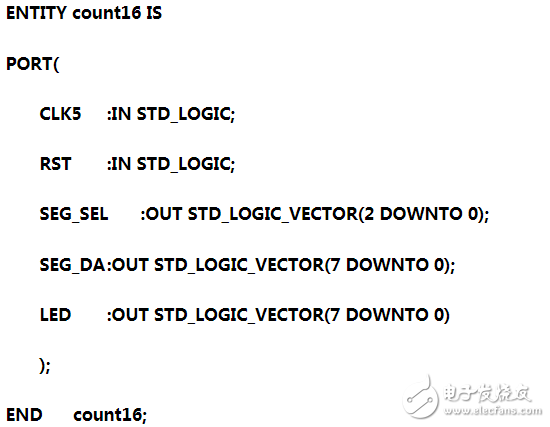

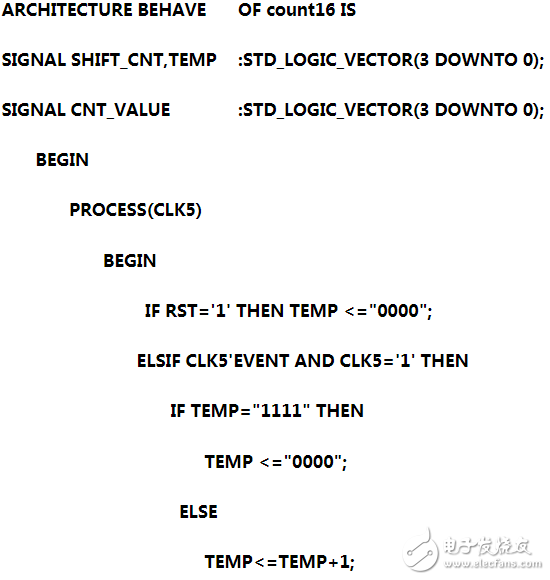

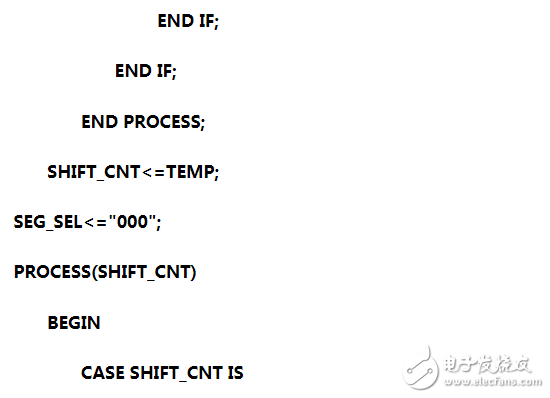

16进制计数器设计方案四:VHDL十六进制计数器

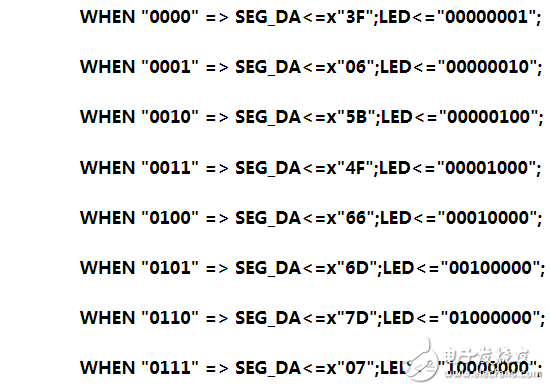

VHDL程序

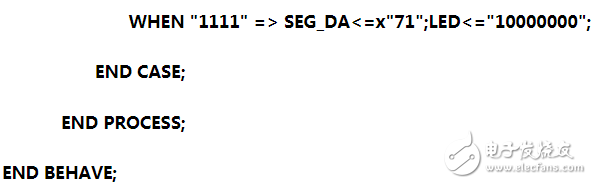

实验 QuarterII原理图

实验过程

1、用Quartus II 7.2 打开已经写好的程序,编译,建立仿真文件,进行仿真。

2、打开计算机和EP2C5实验箱,用串口线连接好,打开电源。

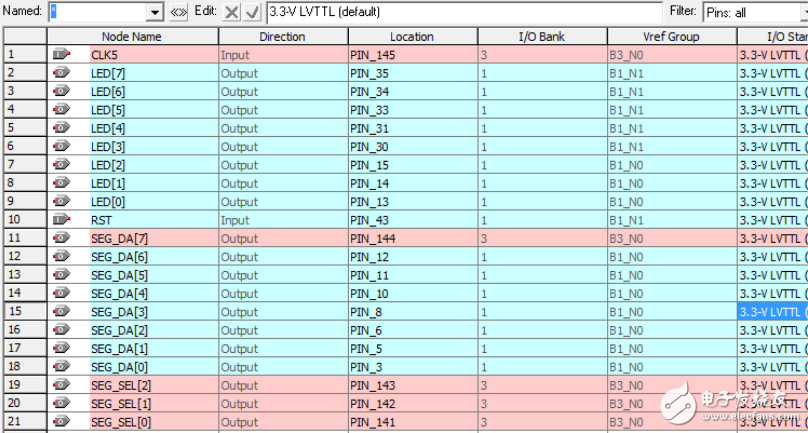

3、为输入输出分配好引脚:CLK5对应 PIN 145 RST 对应 PIN 43

SEG_SEL[2 to 0]对应 PIN 141 142 143

SEG_DATA[7 to 0]对应PIN 144 12 11 10 8 6 5 3 LED[7 to 0]对应PIN 34 33 31 30 15 14 13

4、添加硬件,点击start;观察实验现象;

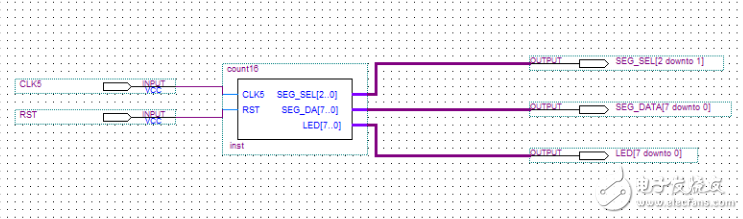

仿真波形

仿真分析:TEMP在时钟上升沿处计数,SEG_DATA[7 to 0],LED[7 to 0]显示对应 TEMP 的值:图中TEMP=0;SEG_DATA[7 to 0]=00111111;LED[7 to 0]=00000001;

引脚分配图

-

任意进制计数器设计方案汇总(七款模拟电路设计原理详解)2018-01-17 70789

-

顶层为原理图的能显示16进制减法计数器设计2009-10-11 0

-

计数器的仿真与设计2019-03-02 0

-

N进制异步计数器设计方案2011-10-24 3454

-

24进制计数器的设计2017-11-09 4420

-

基于74LS160的N进制计数器仿真设计2017-12-21 63242

-

10进制计数器设计方案汇总(六款电路设计原理及程序分享)2018-01-17 71730

-

2进制计数器设计方案汇总(五款模拟电路设计原理及过程详解)2018-01-17 20884

-

八进制计数器设计方案汇总(四款模拟电路原理实现过程)2018-01-17 88693

-

20进制计数器设计方案汇总(三款仿真电路设计原理详细)2018-01-17 11802

-

12进制计数器设计方案汇总(五款模拟电路设计原理及程序分享)2018-01-17 67293

-

5进制计数器设计方案汇总(三款计数器的电路原理图)2018-01-17 61998

-

6进制计数器设计方案汇总(三款模拟电路原理图分享)2018-01-17 66616

-

7进制计数器设计方案汇总(三种模拟电路设计过程详细)2018-01-17 55444

-

计数报警器电路设计方案汇总(多款模拟电路设计原理图详解)2018-01-29 23348

全部0条评论

快来发表一下你的评论吧 !