5进制计数器设计方案汇总(三款计数器的电路原理图)

应用电子电路

803人已加入

描述

本文为大家带来三种5进制计数器设计方案。

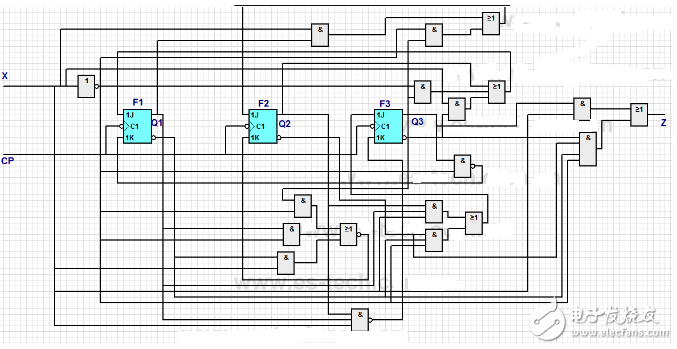

5进制计数器设计方案一:触发器组成的5进制计数器

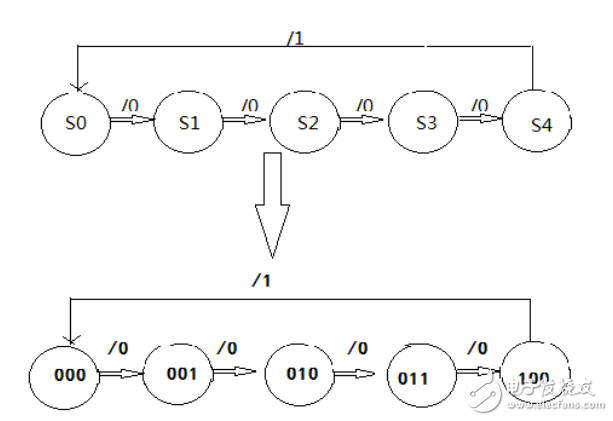

状态图

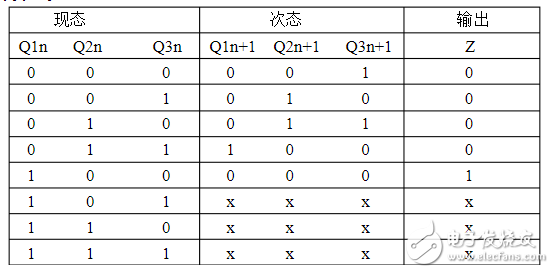

状态表

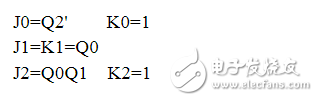

表达式

采用 JK 触发器,由状态表和触发器激励表可作出激励函数的卡诺图,根据卡图,得 J2、J1、J0,K2、K1.K0、Z 的表达式为

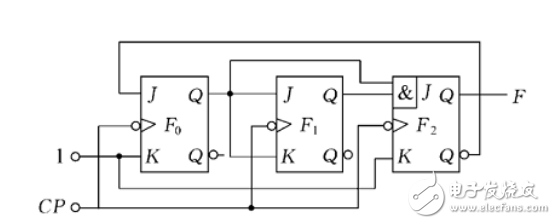

逻辑电路图

5进制计数器设计方案二:基于74ls160的5进制计数器设计

555 电路产生脉冲通过计数器74160进行计数,再经过译码器译码并由数码显示管显示具体的数字。在计数器和译码器之间用一个与非门7400 来控制数字显示的规律。

5进制计数器设计方案三:5进制加减法计数器设计

电路有三个无效状态:101,110,111。当电路进入任何一个无效状态后,当来一个脉冲,即有:Q3n+1=0,Q2n+1=1,Q1n+1=1,电路进入到状态S3=011,输出Z=0,由此可知该电路具有自启动能力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

八进制计数器设计方案汇总(四款模拟电路原理实现过程)2018-01-17 88441

-

计数器的仿真与设计2019-03-02 0

-

60进制计数器2008-06-30 15819

-

100进制计数器2009-06-28 7759

-

百进制计数器电路2009-09-16 5808

-

64进制计数器2009-09-16 4333

-

十进制计数器,十进制计数器原理是什么?2010-03-08 24149

-

N进制异步计数器设计方案2011-10-24 3449

-

集成计数器实现N进制计数2016-06-08 1089

-

10进制计数器设计方案汇总(六款电路设计原理及程序分享)2018-01-17 71530

-

20进制计数器设计方案汇总(三款仿真电路设计原理详细)2018-01-17 11730

-

16进制计数器设计方案汇总(四种电路设计原理图及仿真程序分享)2018-01-17 70314

-

12进制计数器设计方案汇总(五款模拟电路设计原理及程序分享)2018-01-17 67105

-

6进制计数器设计方案汇总(三款模拟电路原理图分享)2018-01-17 66271

-

7进制计数器设计方案汇总(三种模拟电路设计过程详细)2018-01-17 55368

全部0条评论

快来发表一下你的评论吧 !