SN74LS161在数字电路中的抗干扰应用

应用电子电路

描述

计数器除用于计数之外,通常还可以作为移存器、延时电路及各种脉冲波形产生器使用。本文以4位二进制计数器SN74LS161为例,介绍利用计数器实现在数字电路中消除干扰的一种行之有效的方法。

1、SN74LS161介绍

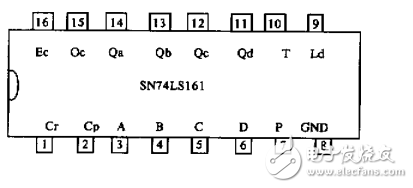

SN74LS161是同步、可预置的4位二进制计数器。图1是它的引脚图。

图1 SN74LS161引脚图

各引脚功能如下:

Cr为复位;Cp为时钟输入;A、B、C、D为预置数输入;P、T为计数控制(使能);Ld为置数控制;Qa、Qb、Qc、Qd:输出;Oc为串行进位输出。

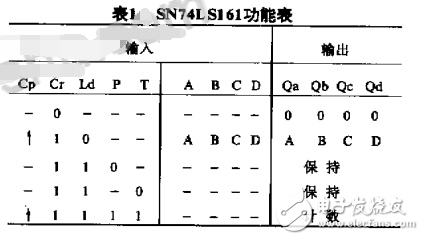

SN74LS161的逻辑功能见表1。由表可知其逻辑功能如下:

(1)异步清零由功能表第一行可见,无论时钟、置数或计数控制为何种状态,只要Cr=0,则计数器被清零,输出QdQcQbQa=0000。所以清零具有最高优先级。

(2)同步置数当Cr=1,即不清零时,若置数控制Ld=0,预置数输入端A、B、C、D预置某个外加数据,则Cp上升沿到达时,计数器的输出与预置数据一致:QdQcQbQa=DCBA,见功能表第二行。置数的优先级仅低于清零。

(3)保持当Cr=Ld=1时,计数控制端P和T中只要有一个为0,则无论有无Cp到达,计数器的状态保持不变,见功能表第3、4行。

(4)计数当Cr=Ld=P=T=1时,SN74LS161为模16的同步加1计数器。当计数脉冲送入Cp端,电路状态按二进制自然态序转换。当QdQcQbQa加至1111B时,进位输出Oc=QdQcQbQaT=1,产生一个高电平进位信号。

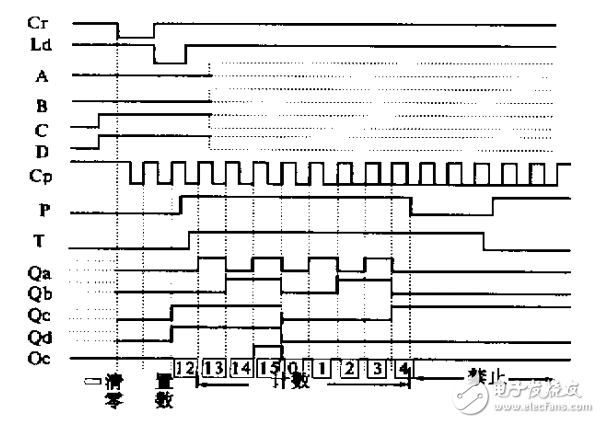

SN74LS161的工作时序如图2。图中顺序为:先将计数器异步清零,再预置数1100B,接着计数至OlOOB,然后禁止。

图2 SN74LS161时序图

2、SN74LS161在数字电路中的抗干扰应用

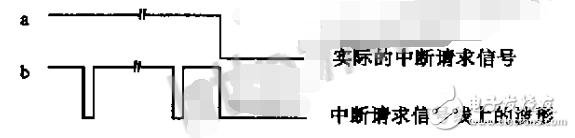

我们在某一微机控制系统的现场调试过程中,由于现场环境恶劣,导致来自外部设备的中断请求信号受到干扰,致使微处理器频繁地收到中断请求。用示波器观察中断请求信号线上的波形,证实了这一判断。图3是实际的中断请求信号及其干扰波形的比较。

图3 中断请求及其干扰波形图

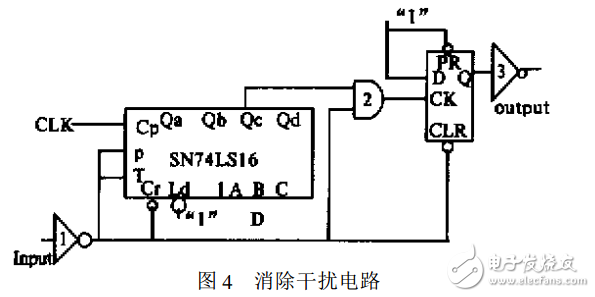

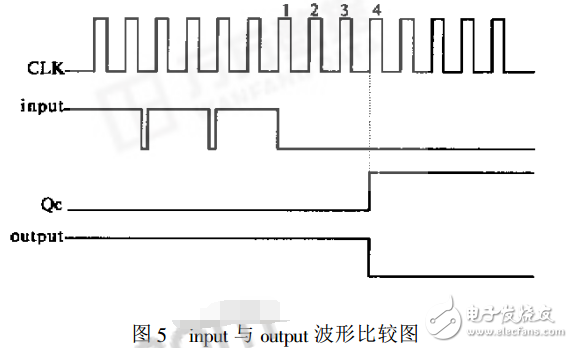

鉴于干扰信号瞬间产生后即刻消失,宽度很窄,于是我们用SN74LS161对中断请求线上受到干扰的信号进行整理。具体电路见图4。input端输入来自外设受到干扰的中断请求信号,output是对input整理之后送往微处理器的中断请求信号INT。当中断请求信号有效(为低电平或下降沿到达)时,SN74LS161开始计数(实质是计时),若其有效宽度达不到要求,说明不是外设发生的真正的中断请求。Qc输出维持低,D触发器没有CK到达,output不会下跳,微处理器接收不到中断请求。若有效宽度达到要求,则认可为真正的中断请求信号/INT,由Oc控制经D触发器送微处理器处理。图5为input和output的波形比较。由图可见,该电路一方面消除了瞬间出现的干扰信号,另一方面将外设发来的中断请求信号input的下降沿向后推迟了若干个CLK周期,这一特点恰好使我们后来遇到另一种干扰时再次使用了这一电路。

由SN74LS16的工作时序可以看出,根据实际信号及干扰信号宽度的不同,SN74LS161的输出可选用Qb、Qc、Qd或者0c。如果微处理器的中断请求信号要求高电平有效,如8086的INTR,则图4中的非门3应当去掉。另外还需根据外设中断请求信号的类型,确定非门1是否使用。在本电路中,当input回到高电平时,SN74LS161和D触发器被同时清零。采用这一电路之后,干扰顺利消除,系统运行一直正常。

此后,在另一数字信号系统中又出现了由于某个芯片的片选信号/cs不稳定,致使系统工作紊乱的情况。从示波器观察这一片选信号,其下降沿处隐约可见极细微的干扰线。这次我们用EPLD实现图4所示电路,截掉了/cs中的干扰部分后,系统工作非常稳定。

实践证明,这是一种非常实用的消除干扰的方法。显然,基于计算器的工作原理及图4的工作原理,不仅SN74LS161,其它型号的计数器同样可以简便、有效地用在数字电路中消除干扰。

-

labview在数字电路课程中的应用2012-05-06 0

-

数字电路抗干扰设计2012-12-05 0

-

74ls1612013-05-20 0

-

单片机和数字电路怎么抗干扰?2021-03-04 0

-

SN74LS161A,pdf(Synchronous 4-B2010-08-10 541

-

74LS161计数器及显示应用电路图2007-12-02 12386

-

考虑并满足数字电路抗干扰性2016-03-29 563

-

数字电路pcb设计的抗干扰考虑2016-03-29 584

-

数字电路、单片机的抗干扰设计2017-01-24 672

-

74ls160和74ls161区别2018-05-08 117374

-

74ls161与74ls163有什么区别2018-05-08 55917

-

74ls161引脚图及功能介绍2021-07-08 208105

-

数字电路中应如何抗干扰2023-11-21 104

全部0条评论

快来发表一下你的评论吧 !