STM32 GPIO工作原理及LED电路原理

模拟技术

描述

一、STM32F103ZET6介绍

1. STM32实物图:

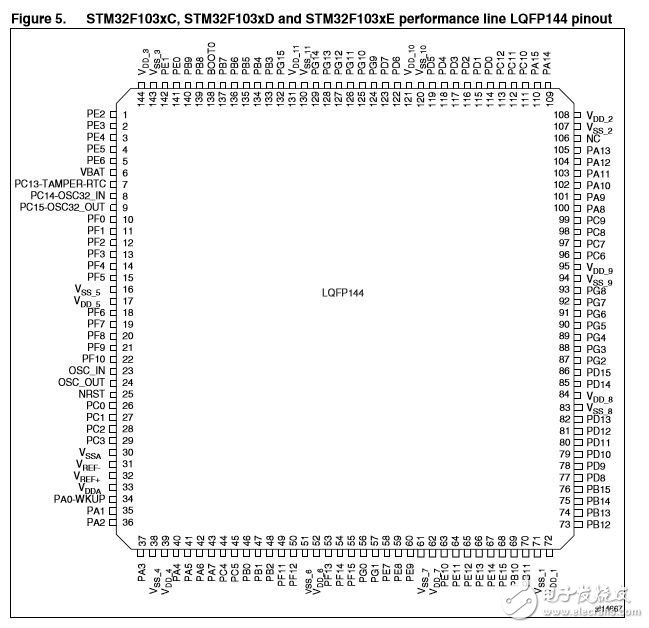

2. STM32引脚分布图:

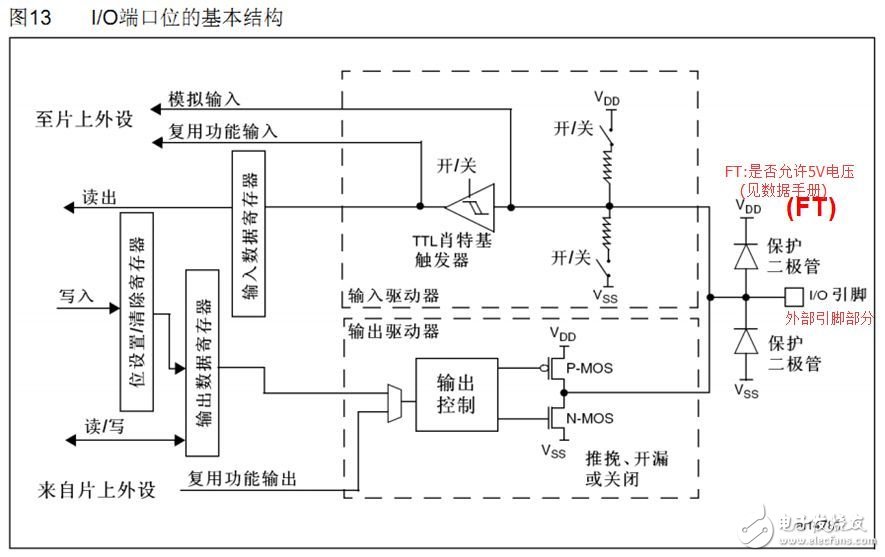

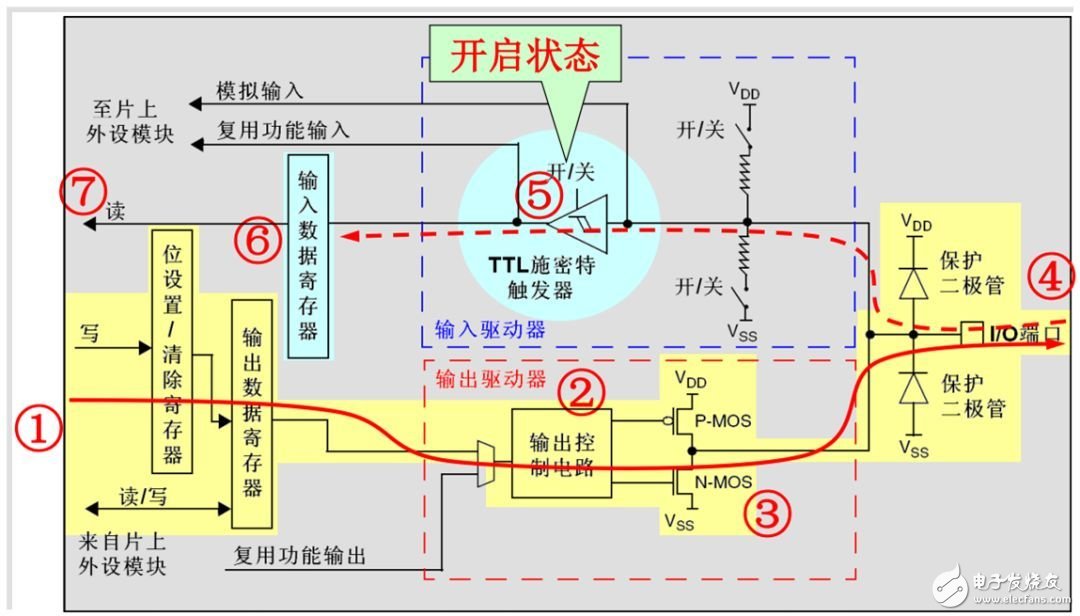

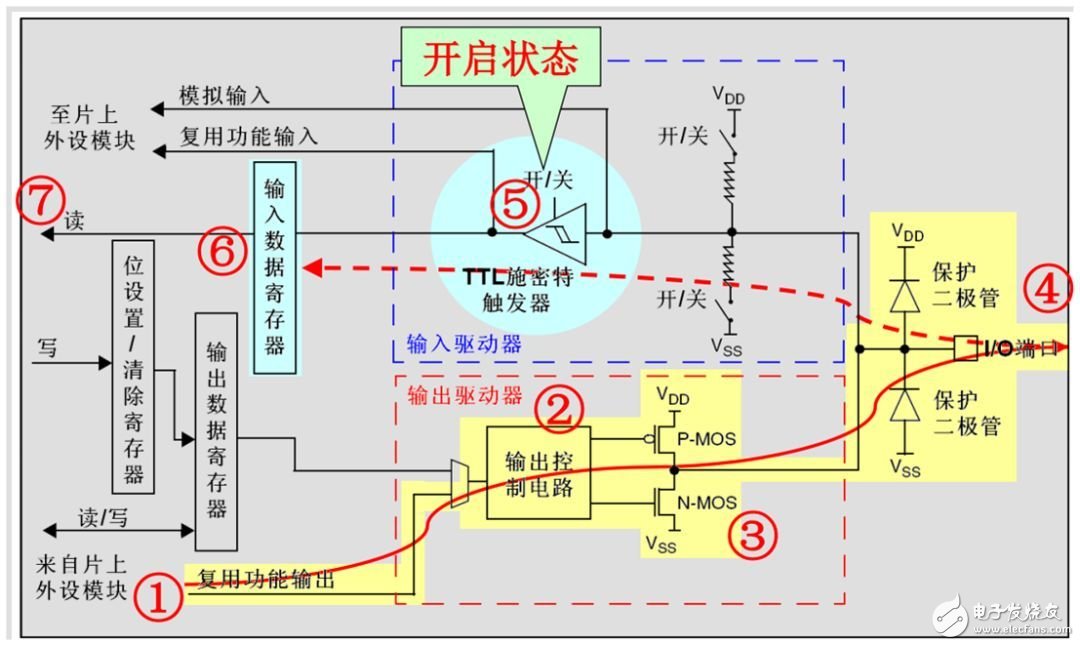

STM32F103ZET6:共144个引脚,7组IO口,每组16个IO口7*16=112个IO口(这7组IO口分别为GPIOA,GPIOB…GPIOG)例如:PGIOA包含PA0,PA1,PA2…PA15,每组16个IO口二、IO口的基本结构和工作方式1. STM32F1系列IO口的基本结构()IO口内部电路结构)

右侧I/O引脚部分为芯片暴露在外部的引脚每个引脚在数据手册都有说明是否支持(识别))5V电压三、PGIO的8种工作方式

4种输入模式

输入浮空

输入上拉

输入下拉

模拟输入

4种输出模式

开漏输出

开漏复用功能

推挽输出

推挽复用功能

可配置3种最大翻转速度

2MHz

10MHz

50MHz

四、八种工作方式讲解

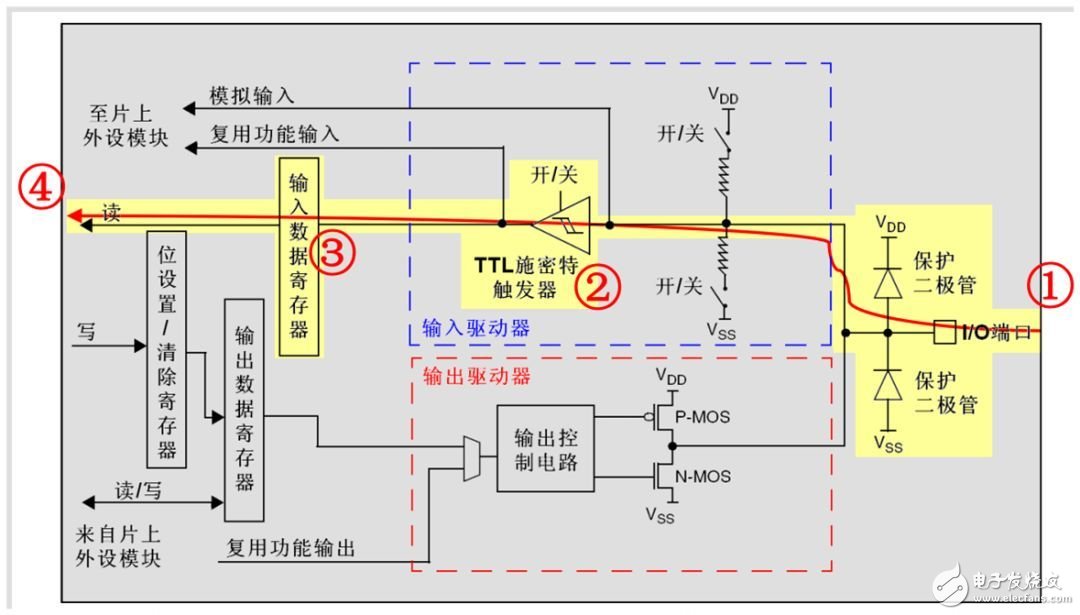

1、GPIO输入工作模式1-输入浮空模式

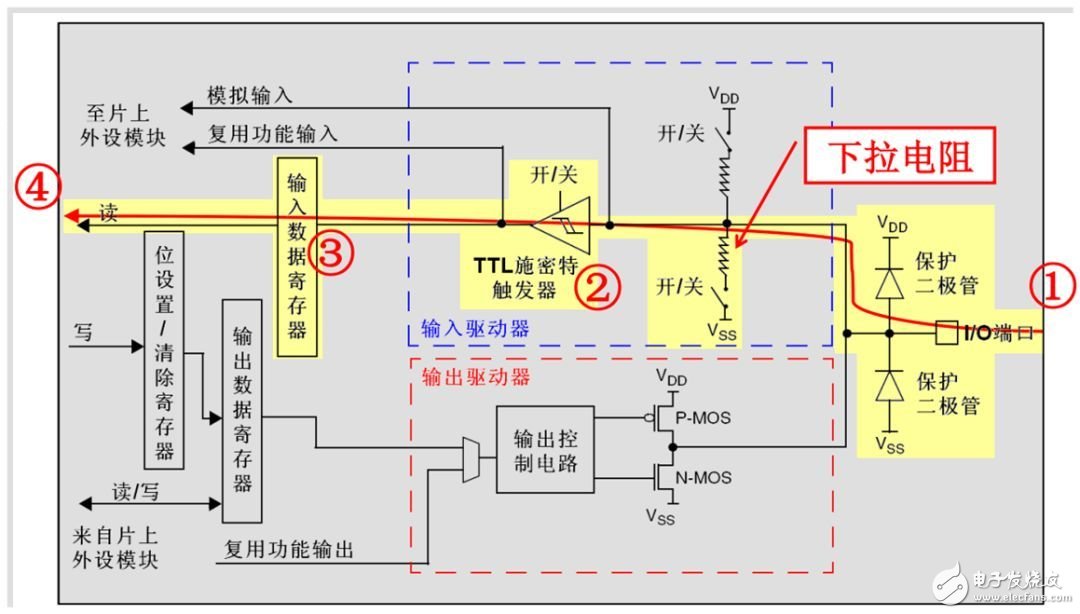

1)外部通过IO口输入电平,外部电平通过上下拉部分(浮空模式下都关闭,既无上拉也无下拉电阻)2)传输到施密特触发器(此时施密特触发器为打开状态)3)继续传输到输入数据寄存器IDR4)CPU通过读输入数据寄存器IDR实现读取外部输入电平值在输入浮空模式下可以读取外部输入电平2,GPIO输入工作模式2-输入上拉模式

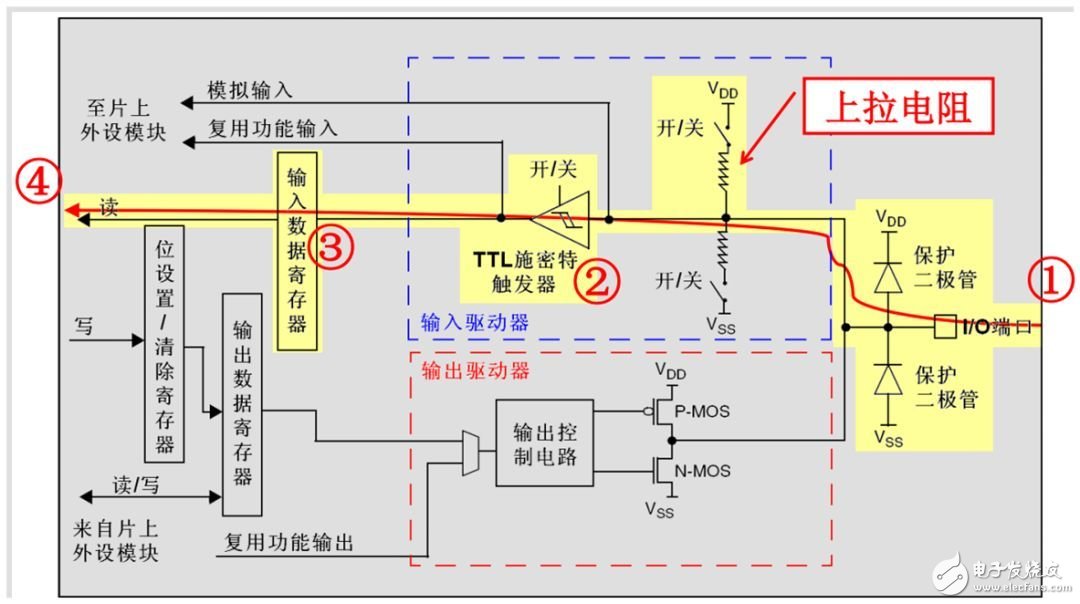

和输入浮空模式相比较,不同之处在于内部有一个上拉电阻连接到VDD(输入上拉模式下,上拉电阻开关接通,阻值约30-50K)外部输入通过上拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取3,GPIO输入工作模式3-输入下拉模式

和输入浮空模式相比较,不同之处在于内部有一个下拉电阻连接到VSS(输入下拉模式下,下拉电阻开关接通,阻值约30-50K)外部输入通过下拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取4,GPIO输入工作模式4-输入模拟模式

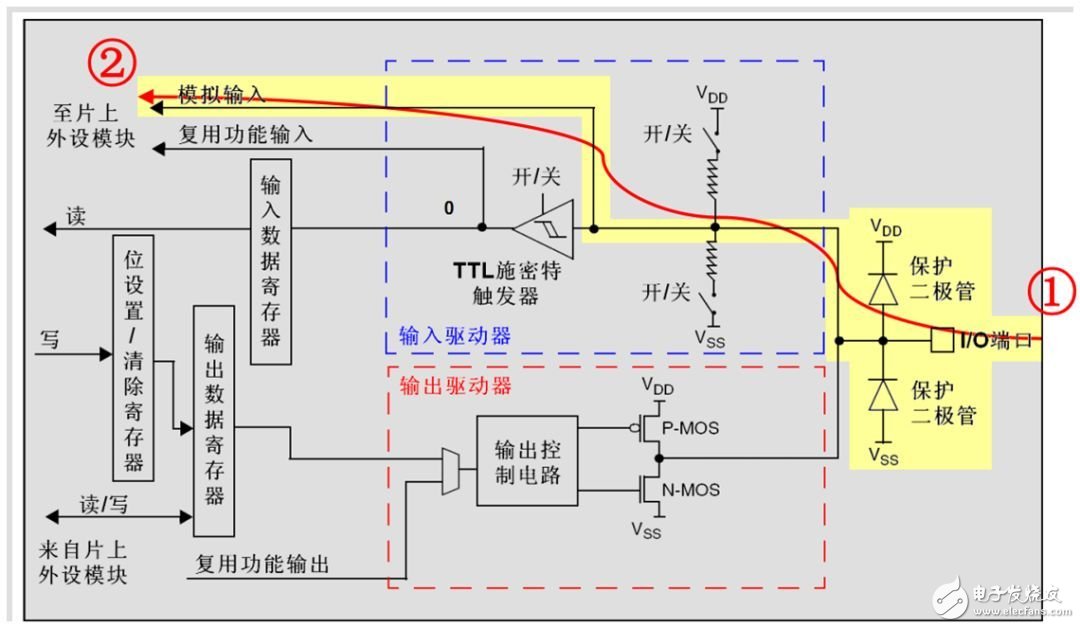

上拉和下拉部分均为关闭状态(AD转换-模拟量转换为数字量)施密特触发器为截止状态通过模拟输入通道输入到CPUIO口外部电压为模拟量(电压形式非电平形式),作为模拟输入范围一般为0~3.3V5,GPIO输出工作模式1-开漏输出模式

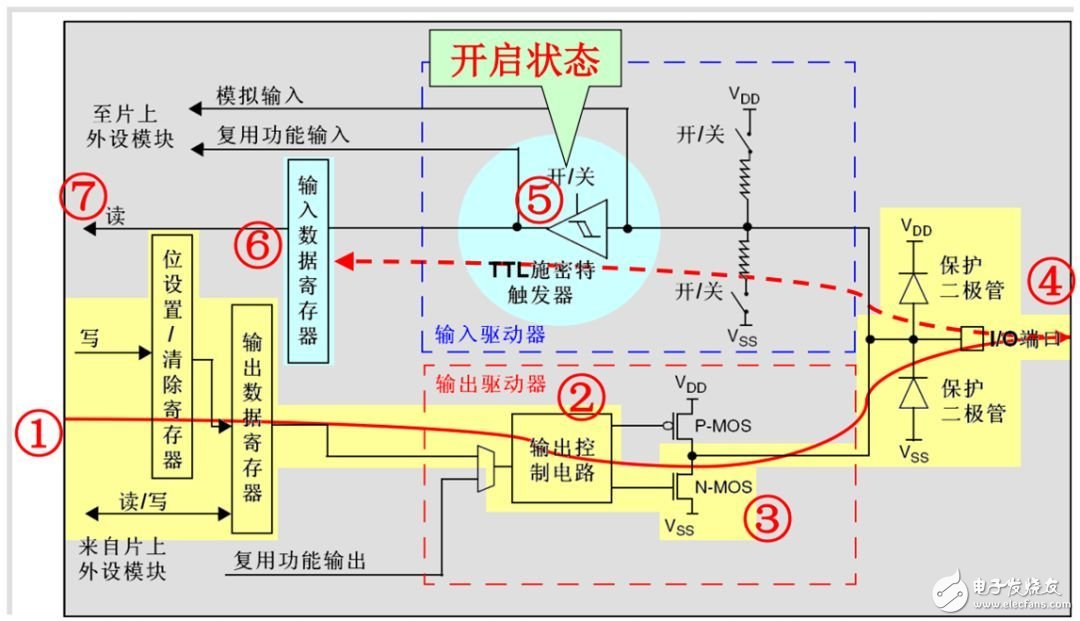

1,CPU写入位设置/清楚寄存器BSRR,映射到输出数据寄存器ODR2,联通到输出控制电路(也就是ODR的电平)3,ODR电平通过输出控制电路进入N-MOS管

ODR输出1:

N-MOS截止,IO端口电平不会由ODR输出决定,而由外部上拉/下拉决定 在输出状态下,输出的电平可以被读取,数据存入输入数据寄存器,由CPU读取,实现CPU读取输出电平 所以,当N-MOS截止时,如果读取到输出电平为1,不一定是我们输出的1,有可能是外部上拉产生的1

ODR输出0:

N-MOS开启,IO端口电平被N-MOS管拉倒VSS,使IO输出低电平 此时输出的低电平同样可以被CPU读取到

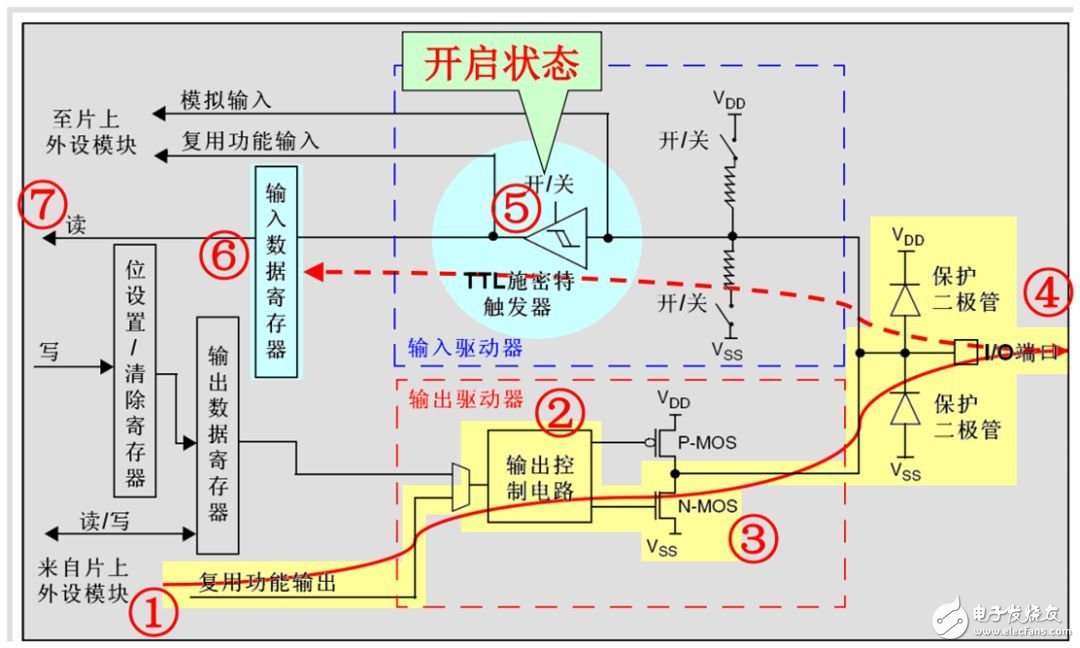

6,GPIO输出工作模式2-开漏复用输出模式

与开漏输出模式唯一的区别在于输出控制电路之前电平的来源开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的开漏推挽输出模式的输出电平是由复用功能外设输出决定的

其他与开漏输出模式相似:控制电路输出为1:N-MOS截止,IO口电平由外部上拉/下拉决定控制电路输出为0:N-MOS开启,IO口输出低电平7,GPIO输出工作模式3-推挽输出模式

与开漏输出相比较:输出控制寄存器部分相同输出驱动器部分加入了P-MOS管部分当输出控制电路输出1时:P-MOS管导通N-MOS管截止,被上拉到高电平,IO口输出为高电平1

当输出控制电路输出0时:P-MOS管截止N-MOS管导通,被下拉到低电平,IO口输出为低电平0同时IO口输出的电平可以通过输入电路读取8,GPIO输出工作模式4-复用推挽输出模式

与推挽输出模式唯一的区别在于输出控制电路之前电平的来源开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的开漏推挽输出模式的输出电平是由复用功能外设输出决定的9,推挽输出和开漏输出的区别:推挽输出:可以输出强高/强低电平,可以连接数字器件开漏输出:只能输出强低电平(高电平需要依靠外部上拉电子拉高),适合做电流型驱动,吸收电流能力较强(20ma之内)五、STM32-IO口相关寄存器每组GPIO包含系列7个寄存器(7组GPIO共包含7*7=49个寄存器)两个32位配置寄存器GPIOx_CRL 低16位GPIOx_CRH 高16位两个32位数据寄存器GPIOx_IDR 输入数据寄存器GPIOx_ODR 输出数据寄存器一个32位置位/复位寄存器GPIOx_BSRR

一个16位复位寄存器GPIOx_BRR

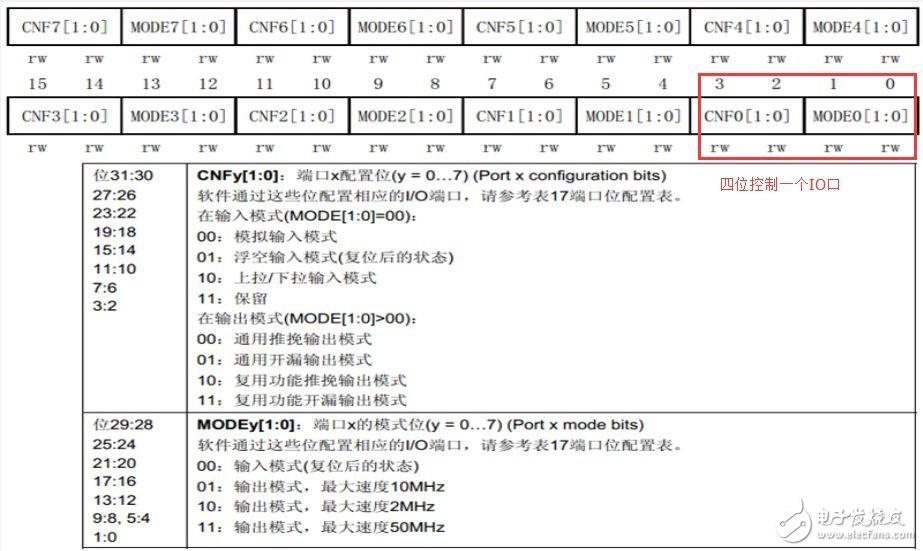

一个32位锁定寄存器GPIOx_LCKR六、STM32-IO口相关寄存器讲解1,端口配置寄存器:STM32每组GPIO位16个IO口,每4位控制一个IO口,所以32位控制8个IO口分为低16位:GPIOx_CRL和高16位:GPIOx_CRH共32位控制一组GPIO的16个IO口

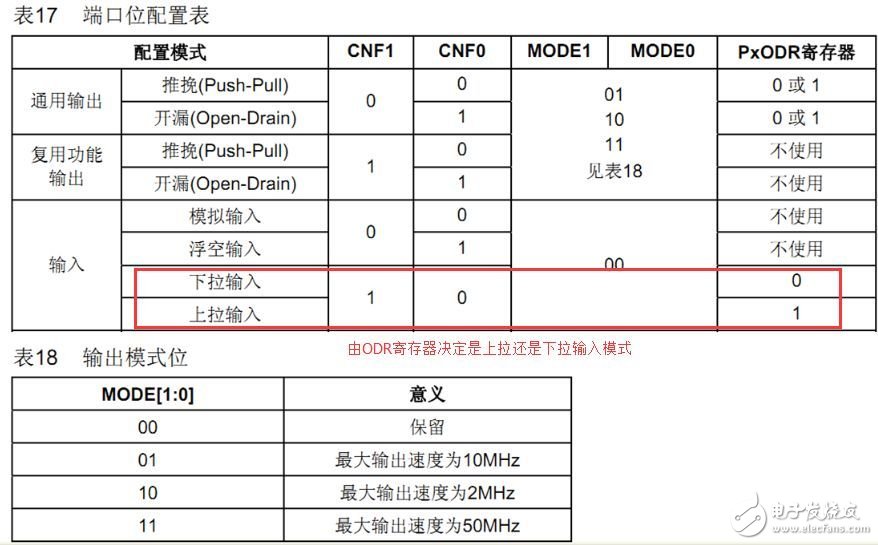

如图:以端口配置寄存器低16位为例,每四位控制一个IO口(高16位同理)MODEx的2位 : 配置IO口输出/输出模式(1种输出+3种不同速度的输出模式)CNFx的2位 : 配置IO口输入/输出状态下(由MODEx控制)的输入/输出模式

以GPIOA_CRL为例,配置IO口PA0 -》 MODE0=00(输入模式) CNF0=10(上拉/下拉输入模式)

此种配置下到底是上拉还是下拉输入模式还需由ODR寄存器决定

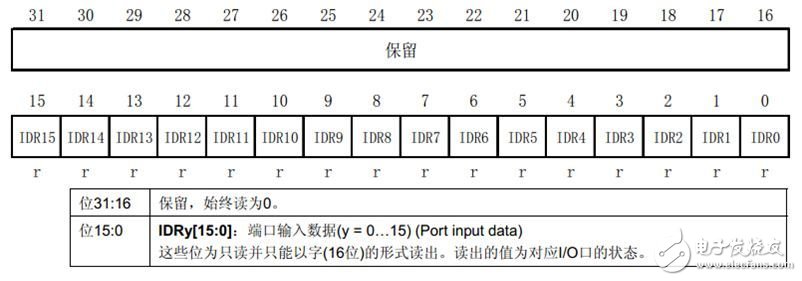

关于上拉/下拉的控制我们将在下面-数据寄存器-中介绍ODR输出寄存器时详细说明 2,数据寄存器(以输入数据寄存器GPIOx_IDR为例) 每一组IO口都具有一个GPIOx_IDR的32位寄存器(实际只使用低16位,高16位保留),即16位控制16个IO口,每一位控制一个

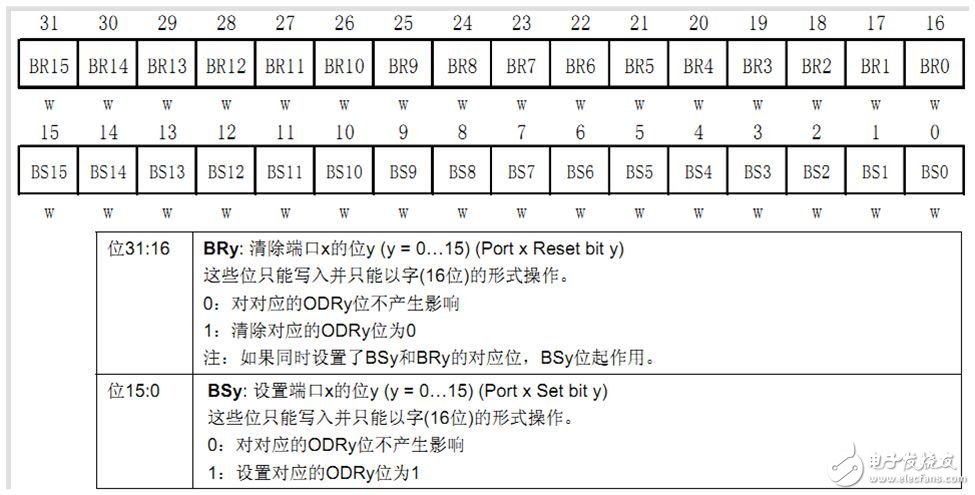

如图:IDR寄存器共32位,0~15位代表一组IO口16个IO当前值这里我们已经了解了输入/输出数据寄存器,现在说下上面提到的问题:当IO口配置为输入模式且配置为上拉/下拉输入模式(即MODEx=00 CNFx=10时),ODR决定到底是上拉还是下拉1)当输出模式时,ODR为输出数据寄存器2)当输入模式时,ODR用作区分当前位输入模式到底是上拉输入(ODRx=0)还是下拉输入(ODRx=1)3,端口位设置/清除寄存器(GPIOx_BSRR)

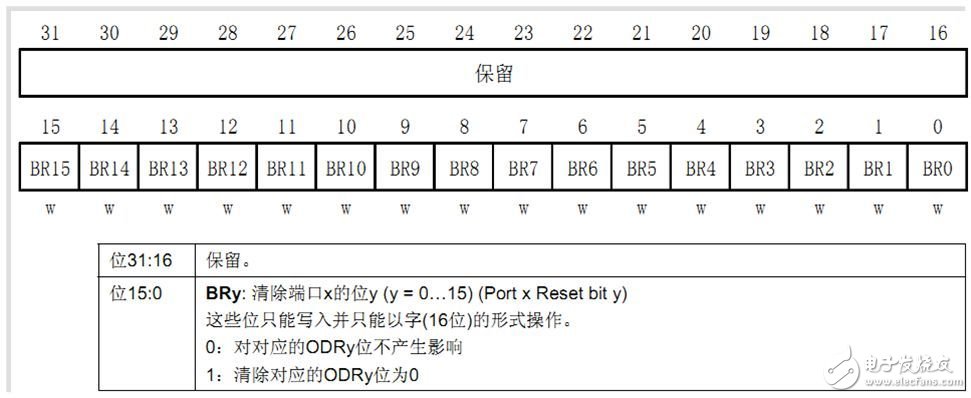

BSRR寄存器作用:BSRR寄存器为32位寄存器,低16位BSx为设置为(1设置0不变),高16位BRx为重置位(1:清除0:不变)当然,最终的目的还是通过BSRR间接设置ODR寄存器,改变IO口电平4,端口位清除寄存器(GPIOx_BRR)

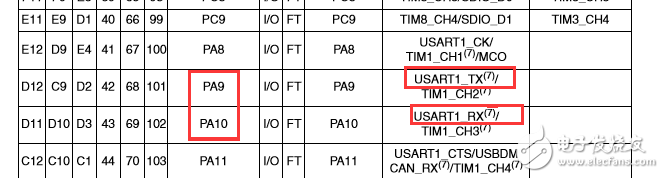

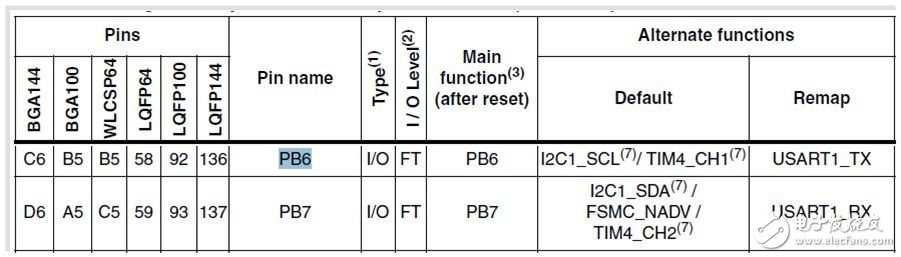

GPIOx_BRR寄存器作用同GPIOx_BSRR寄存器高16位一般我们使用BSRR低16位和BRR的低16位(STM32F4系列取消了BSRR的高16位)5,锁存寄存器:使用较少暂不分析七,端口的复用和重映射1,端口的复用:大部分IO口可复用为外部功能引脚,参考芯片数据手册(IO口复用和重映射)

例如:STM32F103ZET6的PA9和PA10引脚可复用为串口发送和接收功能引脚,也可复用为定时器1的通道2和通道3端口复用的作用:最大限度的利用端口资源2,端口的重映射:

-

什么是GPIO?GPIO工作原理是什么?2022-01-17 0

-

概述STM32中GPIO的8种工作模式2020-07-06 927

-

STM32的GPIO工作原理详解2020-12-18 7475

-

stm32复位电路工作原理2021-08-07 35698

-

stm32单片机的基本工作原理2021-08-19 26704

-

【STM32】STM32F4 GPIO八种模式及工作原理详解2021-11-26 614

-

STM32中GPIO工作原理详解2021-11-29 419

-

1 io口 stm32_GPIO口工作原理的超详细解释(附电路图)2021-11-29 575

-

GPIO工作原理2021-12-01 453

-

STM32F4 GPIO模式及工作原理详解2021-12-24 413

-

【STM32】GPIO工作原理(附电路图)2022-02-10 552

-

STM32 GPIO的工作模式2023-04-14 1349

-

STM32 GPIO结构图讲解 STM32中上拉电阻或下拉电阻的作用2023-08-06 1934

全部0条评论

快来发表一下你的评论吧 !