浅谈现场可编程门阵列发展三个阶段的驱动压力和基本特征

可编程逻辑

描述

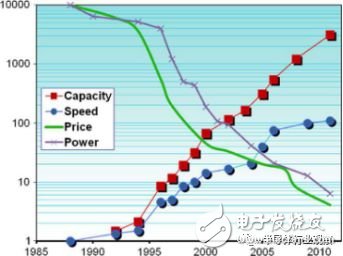

自引入以来,现场可编程门阵列(FPGA)的容量增加了10000倍以上, 性能增加了100倍。 单位功能的成本和功耗都减少了超过1000倍。 这些进步是由工艺缩放技术所推动的, 但是 FPGA 的故事比简单缩放技术的更复杂。 摩尔定律的数量效应推动了FPGA在体系结构、应用和方法方面发生质的变化。 因此, FPGA 已经经历了几个不同的发展阶段。 本文分别总结了发明、扩张、累积这三个阶段, 并讨论了它们的驱动压力和基本特征。 本文最后展望了未来的FPGA阶段。

Xilinx 在1984年引入了第一个现场可编程门阵列(FPGAs), 尽管直到Actel在1988年普及这个术语它们才被称为FPGAs. 在接下来的30年里,我们称之为FPGA的设备的容量增加了1万多倍,速度增加了100倍。 单位功能的成本和能耗降低了1000倍以上(见图1)。

图1 Xilinx FPGA属性相对于1988年。容量指逻辑细胞计数。速度指可编程织物的同功能性能。价格指每个逻辑单元。能量指每个逻辑单元。价格和能量按一万倍放大。数据来源: Xilinx发表的数据。

这些进步在很大程度上是由工艺技术驱动的, 随半导体的扩展, 很容易把 FPGA 的进化看成是一个简单的容量发展。 这种看法太简单了。FPGA 进展的真实故事要有趣得多。

自其引入以来, FPGA 设备经过几个不同的发展阶段已取得进展。 每个阶段都受到工艺技术机会和应用程序需求的驱动。这些驱动压力引起设备特性和工具的可观察变化。在本文中, 我们回顾了FPGA的三阶段。 每个阶段长达8年, 并且每一段在回顾中都很明显。

三个阶段分别是:

1)发明阶段, 1984–1991;

2)扩张阶段, 1992–1999;

3)累积阶段, 2000–2007.

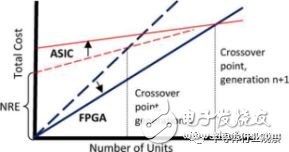

图2. FPGA与ASIC交叉点。 图表显示总成本与单位数量。 FPGA线条较暗,从左下角开始。 随着下一个工艺节点的采用(从较早节点的虚线箭头到稍后节点的实线箭头),由垂直虚线表示的交叉点变大。

二、前言: 关于FPGA的重大问题有哪些?

A.FPGA VS ASIC

20世纪80年代,专用集成电路(ASIC)公司为电子市场带来了一个惊人的产品:定制集成电路。 到20世纪80年代中期,有数十家公司在销售ASIC,在激烈的竞争中,成本低,容量大,速度快的技术更具受青睐。 当FPGA出现的时候,它在所有这几个方面上都并不突出,但却一枝独秀。这是为什么?

ASIC的功能是由自定义掩模工具决定的。ASIC的客户为这些掩模工具支付了前期的一次性工程(NRE)费用。由于没有定制的工具,FPGA降低了预付成本和建立定制数字逻辑的风险。通过制造一种可以被成百上千的客户使用的自定义硅设备,FPGA供应商可以有效地平摊所有客户的NRE成本,从而不会对任何一个客户收取任何费用,又同时增加了每个客户的单位芯片成本。

前期的NRE成本确保了FPGA在某些数量上比ASIC更具成本效益。FPGA供应商在他们的“交叉点”上吹嘘这个数字,这个数字证明了ASIC的更高的NRE开销。 在图2中,图线显示了购买数量单位的总成本。 ASIC具有NRE的初始成本,并且每个后续单元将其单位成本增加到总数。 FPGA没有NRE电荷,但是每个单元的成本都比功能相当的ASIC要高,因此斜率更陡峭。 两条线在交叉点相遇。 如果所需的单元数量少于此数量,则FPGA解决方案便宜; 超过该数量的单位表明ASIC具有较低的总体成本。

由于NRE成本占ASIC总体拥有成本的很大一部分,所以FPGA每单位成本超过ASIC成本的优势随着时间的推移而减少。 图2中的虚线表示某个工艺节点的总成本。 实线表示下一个工艺节点的情况,NRE成本增加,但是每个芯片的成本较低。 FPGA和ASIC都利用低成本制造,而ASIC NRE收费继续攀升,推高交叉点。 最终,交叉点变得如此之高,以至于大多数客户,单元的数量已经不再适用于ASIC。 定制芯片只保证非常高的性能或很高的体积; 所有其他人可以使用可编程解决方案。

摩尔定律最终将推动FPGA能力覆盖ASIC要求,这是对可编程逻辑业务的一个基本早期认识。如今,器件成本在性能,上市时间,功耗,I / O容量以及其他功能方面都不如FPGA。许多ASIC客户使用较老的工艺技术,降低了NRE成本,但降低了单芯片成本优势。

FPGA不仅消除了前期掩蔽费用并降低库存成本,而且通过消除整个类别的设计问题也降低了设计成本。这些设计问题包括晶体管级设计,测试,信号完整性,串扰,I / O设计和时钟分配。

与低前期成本和简单设计一样重要的是,主要的FPGA优势是即时可用性和降低的故障可见性。尽管大量的仿真时,ASIC第一次似乎很少是正确的。随着晶圆制造周转时间在几个星期或几个月内,芯片重新调整对时间安排造成重大影响,而且随着掩膜成本的上升,芯片重新调整对公司日益增长的水平而言是显而易见的。错误的高成本要求广泛的芯片验证。由于FPGA可以在几分钟内完成重做,因此FPGA设计不会因为错误而延误数周。因此,验证不一定要彻底。 “自我模仿”,俗称“下载试用”,可以代替大量的模拟。

最后看一下ASIC生产风险:ASIC公司只有在客户的设计投入生产时才赚钱。 在20世纪80年代,由于开发过程中需求的变化,产品故障或完全设计错误,只有三分之一的设计实际投入生产。 三分之二的设计损失了钱。 这些损失不仅由ASIC客户承担,还由ASIC供应商承担,这些供应商的NRE收费很少包括他们的实际成本,从未在快速贬值的制造设施中弥补失去机会的成本。 另一方面,可编程逻辑公司和客户仍然可以小批量赚钱,并且可以快速纠正小的错误,而不需要昂贵的掩模。

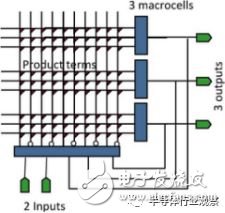

图3.通用PAL架构。

B. FPGA VS PAL

可编程逻辑在FPGA之前就已经建立起来了。在20世纪80年代早期,EPROM编程的可编程阵列逻辑(PAL)已经开辟了一个市场。但是,FPGA具有体系结构优势。为了理解FPGA的优势,我们首先看看这些早期的80年代器件的简单可编程逻辑结构。一个PAL设备,如图3所示,由一个两级逻辑结构组成。显示输入在底部。在左边,一个可编程和阵列产生产品条款,以及输入和它们的反转的任何组合。右侧块中的固定或门完成宏单元产品术语的组合逻辑功能。每个宏单元输出是芯片的输出。宏单元中的可选寄存器并反馈到和阵列的输入使得实现非常灵活的状态机成为可能。

不是每一个功能都可以通过PAL的宏单元阵列实现一次,但是几乎所有的常用功能都可以,而那些不可能通过阵列实现的功能。无论执行的功能还是位于阵列中的位置,通过PAL阵列的延迟都是相同的。 PAL具有简单的拟合软件,可将逻辑快速映射到阵列中的任意位置,而不会影响性能。 PAL适配软件可以从独立的EDA供应商处获得,使IC制造商可以轻松地将PAL添加到他们的产品线中。

从制造的角度来看,PAL是非常有效的。 PAL结构与EPROM存储器阵列非常相似,其中晶体管被密集地包装以产生有效的实现。 PAL与存储器非常相似,许多存储器制造商能够用PAL来扩展他们的产品线。当周期性内存业务出现停滞时,内存厂商进入可编程逻辑业务。

当考虑缩放时,PAL的架构问题是显而易见的。在和阵列中的可编程点的数量随着输入数量的平方(更确切地说,输入乘以乘积项)的平方增长。工艺缩放以收缩因数的平方来提供更多的晶体管。然而,阵列中的二次增加限制了PAL仅通过收缩因数线性增长逻辑。 PAL输入和产品期限也很重,所以延迟随着尺寸的增加而迅速增长。像任何这种类型的存储器,PAL都具有跨越整个芯片的字线和位线。随着每一代,所编程的晶体管的驱动与负载的比例下降。更多的投入或产品条款增加了这些线路的负载。增加晶体管尺寸以降低电阻也提高了总电容。为了保持速度,耗电量急剧上升。大型PAL在区域和性能上都是不切实际的。作为回应,在20世纪80年代,Altera率先推出了复杂可编程逻辑器件(CPLD),由多个PAL型块组成,其中较小的交叉开关连接。但FPGA具有更具可扩展性的解决方案。

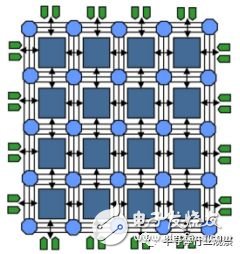

图4.通用阵列FPGA架构。 4 4阵列,每行和每列有三条接线轨迹。 开关位于交叉点的圆上。 设备输入和输出分布在阵列周围。

FPGA的创新是消除了提供可编程性的数组和阵列。相反,配置存储器单元分布在阵列周围以控制功能和布线。这种改变放弃了PAL结构的类似存储器阵列的效率,有利于架构的可扩展性。如图4所示,FPGA的架构由一系列可编程逻辑块组成,并与现场可编程开关互连。 FPGA的容量和性能不再受到阵列的二次增长和布线布局的限制。并不是每一个功能都是芯片的输出,所以容量可以随着摩尔定律而增长。

•FPGA架构看起来不像内存。 设计和制造与内存非常不同。

•逻辑块较小。 不能保证一个单一的功能可以融入其中。 因此,提前确定将有多少逻辑适合FPGA是很困难的。

•FPGA的性能取决于逻辑放置在FPGA中的位置。 FPGA需要布局和布线,所以完成的设

[1] [2] [3] [4] [5]

- 相关推荐

- FPGA

-

现场可编程门阵列2015-03-13 0

-

现场可编程门阵列有哪些应用?2019-08-06 0

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 0

-

XC6SLX16-2FTG256C现场可编程门阵列2021-04-13 0

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 0

-

XC3SD1800A-4CSG484LI现场可编程门阵列2021-04-26 0

-

XC5VLX85-1FF676C现场可编程门阵列2021-04-26 0

-

XC6SLX75T-2CSG484I现场可编程门阵列2021-04-26 0

-

XC7A200T-2FFV1156I现场可编程门阵列2021-04-26 0

-

FPGA-现场可编程门阵列2021-07-30 0

-

现场可编程门阵列的结构与设计2009-07-07 1369

-

现场可编程门阵列的供电原理及应用2010-03-17 1405

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 832

-

基于现场可编程门阵列的电机控制器测试2021-07-02 546

-

现场可编程门阵列是什么2024-03-16 1689

全部0条评论

快来发表一下你的评论吧 !