资料下载

×

双相动态电路暨设计自动化流程

消耗积分:2 |

格式:rar |

大小:0.99 MB |

2018-01-24

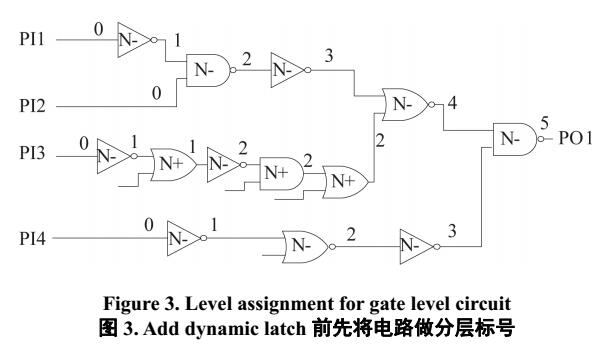

由于骨牌逻辑电路通常较互补式金氧半组件电路计具有较小的面积与更快的速度,所以已经被广泛使用于设计高速电路如微处理器的设计中。虽然有许多关于动态电路的研究,然而大部份的研究却忽略探讨如何实现其研究成果。在本论文中,我们设计了一个创新的双相操作高速动态电路,它具有管线式(pipeline)的电路结构,运作速度不受电路复杂度的影响,使得它的效能较传统动态电路的提升极多,因具容忍频率歪斜(skew tolerant)的特性,可使用标准组件之设计流程来设计。最后,芯片测量结果证明完成了下述设计目标:一个Performance Scalable的very high speed dynamic 32×32 bits之multiplier具有下列特性:1)高速频率操作,工作效能较一般传统动态电路改善甚多。2)可以为容忍clock skew,使用Duty Cycle Pulse Generator (DCPG)的技术来产生double clocking的时间,可借由DCPG来克服process variation及cell based design clock tree routing所造成的skew的问题。3)使用BIST技术作为正常效能的自测功能,此功能可转为本芯片在process后仍可以调整电路效能,做为电路performance management的机制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章