架构/颗粒/接口/可靠性全面解析:最全面的闪存技术大普及

存储技术

描述

闪存最明显特点就是稳定性能,低时延和高随机IOPS。对于闪存,在评估性能时,我们一般主要关注90% IO落入规定的时延范围(性能是一个线性范围,而不是某一个点)。数据保护等追求所有软件特性都基于Inline实现,如Inline重删、压缩、Thin-Provisioning(尤其是重删,一方面SSD价格还是偏高,重删压缩可以节约投入成本;另一方面也减少了IO下盘次数提高SSD寿命)。但对于闪存,我们所关注的特性和技术指标远远不止这些。

闪存架构

闪存的Scale out能力:横向扩展能力是应对并发访问和提升性能容量的最基本特性,所以闪存是必须具备的功能。目前XtremIO支持16控,solidfire已经支持但100个控制器节点。

控制器对称A/A 能力:闪存的主要应用场景如OLTP等,传统的A/P、ALUA阵列在主控制器故障切换时都需要时间切换,并导致IO归零;并且在闪存阵列下,一般系统CPU是瓶颈,所以只有无归属、性能均衡的A/A对称架构才能更好应对。目前传统存储(如EMC VMAX/VNX,HP 3PAR, HDS USP/VSP)都已经支持,但是闪存阵列还没看见宣传;好多闪存产品,如 PureStorage还是 A/P模式。

元数据管理

闪存的设计主要是考虑如何发挥出SSD的随机访问性能,不像HDD那样,需要通过预取、IO聚合技术来提高下盘的顺序性,减少对机械盘的操作来提升性能。所以闪存在设计上要考虑如何优化元数据(系统元数据、重删压缩指纹、FTL映射等)管理,IO调度策略,垃圾回收和磨损均衡等设计。

两层元数据管理架构是实现元数据管理的趋势,其基本思想是元数据映射基于LBA-》块ID-》Block位置的Map形式,卷的数据LBA映射到块ID,而不是磁盘上的物理Block地址;数据变化后只需改变对应块ID映射关系,块ID就可以映射到新的物理空间,这样相比单层方式就简化重删压缩实现和效率。

SolidFire采用两层元数据管理架构实现元数管理,元数据管理采用Key-Value方式;元数据映射基于LBA-》块ID-》位置的Map形式,卷的数据LBA对应块ID,而不是磁盘上的物理地址;所以数据变化后计算指纹只需改变对应块ID映射关系,天然就支持重删。在垃圾回收时,是采用块标记法实现对未使用块的清除。

GFTL功能

GFTL称作Global FTL,闪存阵列可以配合SSD控制器(需要SSD开放内部接口给阵列),通过阵列完成一些如ROW写满条带下盘,全局负载均衡,整块对齐擦除、垃圾回收等高级优化功能。另外,GFLT也可记录重删压缩数据库,指纹元数据管理,实现RAID功能,进行IO聚合,通过元数据记录实现RAID满条带下盘,从而规避读、修改、写放大操作,解决Write-Hole问题等。

SSD自身的FTL只能完成数据LAB/重删后数据块、到真实颗粒块(block)的影射,只能实现简单的垃圾回收和ROW数据写,内部把不同Block组织在一起组成RAID。很多外购SSD磁盘的闪存厂商都还不支持GFTL技术,但是该技术是提高闪存效率和竞争力的有力武器。

重删特性

重删是闪存最基本特性之一,分为Inline和Postline,但对闪存Inline才能体现真正价值。重删一般分为HASH指纹算法(以SHA-1为例说明,存在碰撞问题)和按字节对比法两种,逐字节对比可靠性高,但会严重影响闪存性能,所以很少使用,只在数据一致性要求非常严格的场景下使用。

SHA-1算法会有Hash冲突的概率,Hash输出长度一般为160字节的数字,对不同数据块(大小可设置)其输出是随机的,在0-2^(160-1)间分布,不同数据产生相同Hash值的概率2^(-160),只有数据量(固定数据块大小)超过这些数字能表示的值时,才会发生Hash冲突,但到目前位置,所有产生的数据量总和都不至于产生Hash冲突。

所以Hash方式在产品中最为常见。场见的强Hash算法有SHA-1, SHA-256等;常见的弱Hash算法有Murmur3, CRC, MD5等;强Hash发生冲突的概率低。

但是在某些场景,如在8K业务数据块大小的数据库场景下,Key值基本上是唯一的,如果重删粒度也是8K则根本起不到重删的效果,可以让客户选择关闭该功能(XtremIO的Inline重删功能是无法关闭的),只开启压缩。

IO基本流程

数据从主机下发到闪存阵列控制器,对于非A/A架构的闪存来说,首先盘判断IO对应LUN的归属,如果LUN归属在在本地控制器,IO就写到到对应Cache并镜像,否则转发给LUN归属控制器处理。Cache到水位时再切分块LBA为相应大小后,交给增值模块(如重删压缩模块)处理,计算出指纹后,将指纹和数据(重复数据只保留指纹)交给归属控制器来完成下盘,相关模块下盘时分配分条,凑满条带后顺序写入磁盘,记录真实地址和指纹关系,保存指纹到指纹数据库。

Block磨损均衡

Block磨损均衡是为了让数据均匀分布在SSD的所有Block中,从而能达到冷热点均匀分布提高SSD寿命的目的。闪存必须提供磨损均衡来实现,磨损均衡分为动态磨损均衡和静态磨损均衡;动态磨损均衡是由主机更新数据触发的,通过主机读写保证数据的擦写平均分布到所有的Block上,因为每种应用都有冷热数据,所以静态磨损均衡并不能保证冷热度均匀分布。

静态磨损均衡是由SSD内部机制实现,将冷Block上的数据进行转移(不同于垃圾回收),擦写冷Block上面的数据来接受经常变化的热点数据,使冷Block有机会成为热Block,从而使SSD中所有Block的冷热度达到平衡。

SSD掉电保护

为了防止SSD磁盘中缓存数据由于掉电丢失,SSD还需要提供掉电保护功能。一般SSD会设计电压检测模块来实时检测电压值,当电压低于设置阈值时,SSD电压检测模块会通知SSD控制器进入掉电数据刷写流程,此时会有超级电容作为备电源供电,把磁盘缓存数据刷到Flash颗粒中,防止数据丢失。

另一方面,闪存阵列也应该提供一种机制,当阵列主动下电或升级维护时,下发命令给SSD,让SSD进入掉电缓存数据刷新流程,保证数据一致性。

闪存(Flash)是相对于HDD而言的一种非易失性存储器,Flash分为NOR Flash和NANDFlash,NOR Flash可以当作内存使用直接执行程序,相比DDR 、 SDRAM 或者 RDRAM具有掉电数据不丢失等特点,所以在嵌入式设备(ARM/MIPS等体系架构)中,一般采用NOR Flash存储BootLoader和OS程序。但今天我们的重点是NAND Flash。

Flash颗粒解析

学习过模拟电路的同学都知道,在模电原理里三极管分两种,一种是双极性三极管,主要基于载流子用来做电流放大,另一种叫做CMOS场效应三极管,通过电场控制的金属氧化物半导体。NAND Flash就是基于场效应P/N沟道和漏极、栅极技术通过浮栅Mosfet对栅极充电实现数非易失据储存的。一个晶体单元称作一个Cell,向Cell中充电就是编程或写入数据,通过电平的高低来判断数据是0还是1。在SLC颗粒类型的Flash中,冲入电荷读取到阈值电平为高电平,一般表示数据0。

NAND Flash SSD和HDD的最大区别,其一是SSD通过Flash控制电路选通原理来读/写对应地址数据,不必采用笨拙的机械磁头定位数据外;其二是SSD在充电写入数据前,必需要擦除原有的数据,每次充电和放电称为一次P/E(编程/擦出),一块SSD的寿命和可以执行P/E操作的次数强相关。每种Flash颗粒的P/E操作次数是不同的,P/E操作次数越多,对应Flash颗粒的SSD寿命越长,可靠性越好,价格也越高。

NAND Flash颗粒分类

NAND Flash可根据Cell储存bit数据位的不同分为SLC,MLC,TLC,其中MLC还分为eMLC,MLC和cMLC。由于不同类型颗粒结构不同,所有导致了不同颗粒间数据储存能力,性能和可靠性存在差异。

SLC(single level Cell) 是单层存储单元,一个Cell中只存储1bit数据(0/1),在写入数据后就高低2为电平,由于判定写入数据值电压的区间小,所以可擦写次数和可靠性也是最好的,一般在5W-10W之间,但是存储容量相对较少,成本也最高。

MLC(multi-level Cell) 多层式储存单元,存储密度较大,一个Cell中可以存储2bit数据(00/01/10/11),相比SLC,判定写入Cell中电压值区间比2bit数据就比较复杂了,由于NAND Flash的物理属性(擦写会对颗粒的绝缘层造成损坏),也使得随着擦写次数增多,很难判断出写入的数据具体代表的bit位。其擦写次数一般3K左右,另外,2bit数据读写使得MLC速度比SLC慢,但容量较大,价格比较便宜。

eMLC(enterprise MLC)和cMLC(consumer MLC)都是采用MLC技术,主要差别就是NAND Flash颗粒筛选参数,制作工艺和测试方法不同。通过不同标准来界定颗粒,eMLC是经过严格测试和企业级标准筛选,所以可靠性和寿命最高;MLC次之;把挑选完eMLC/MLC之后颗粒成为 cMLC,可靠性和寿命都要稍差一些,但成本低,一般总在个人消费和企业非关键应用中。

TLC(Triple level Cell)三层式存储单元,一个Cell中存放3bit数据(000-111),数据密度更大,通过判定电压确定写入Cell数据的难度更大,所以SLC的擦写次数(P/E)操作只有几百次到上千次;可靠性和性能很低,具有成本优势,一般用在个人消费产品中(不能满足企业产品要求)。

SSD的可靠性问题

为了进一步提高SSD磁盘的寿命,一方面,存储(SSD/HDD)厂商还会在颗粒之上通过ECC(随用户数据生成一起写入磁盘)纠错技术纠正静默错误。在数据写入时采用ECC编码写入检验位,当数据由于位翻转导致静默错误,读取数据时可以利用ECC检验位校正数据,并把正确数据返回主机。常用的ECC校正机制有8bit/512bit, 32bit/2KB,分别可以实现512bit中8bit数据检验和2KB中32bit数据错误的检验,如果错误的bit位数超过8/32bit(称为Uncorrectable bit error),ECC是无法检验恢复的,必须采用RIAD机制来恢复。

另一方面,SSD厂商采用Over-provisioning技术提高闪存寿命。SSD的写入单位是Page, 擦除单位是Block,对某一块Block擦写达到一定次数就会导致Block失效(写入的数据无法判定识别)作废,所以SSD也提供了额外的容量(称为 Over- provisioning),以便替换坏块提高整个SSD寿命,当失效Block的容量超过Over-provisioning容量(MLC的Over-provisioning一般为SSD总容量的28%,不同介质和厂商有所不同),使得整个SSD容量小于其宣称容量时,该SSD就失效了。

颗粒的发展和未来

虽然NAND Flash目前处于绝对的王者地位,但是传统的NAND Flash是一种线性串列的Mosfet存储结构,这种结果限制其容量很难做大。一个可行的方式就是增加存储密度,目前NAND Flash的存储密度已经可以做到微米、甚至到纳米级别;但是随着密度增高,存储单元Cell的浮栅周围产生电容耦合,存储数据能力和可靠性极速降低。

所以,3D Flash技术的出现给闪存的发展指明了方向,3D-Flash技术主要有下面三个方向。

忆阻Memristor存储技术

忆阻器本质上是一种有记忆功能的非线性电阻,通过控制电流的变化可改变其阻值,如果把高阻值定义为“1”,低阻值定义为“0”,通过这种电阻变化实现存储数据的功能。

美光/英特尔联合推出3D XPoint忆阻器存储技术,SanDisk/惠普也达成合作协议,此次合作以惠普忆阻器技术和SanDisk的非易失性存储器技术创造一个新的企业级忆阻器存储方案。忆阻器存储在访问速度上Flash存储快1000倍。

3D XPoint是一种立体化的存储技术,它看起来与同为3D设计的NAND技术相似,但本质却不同,3D XPoint并不单纯是NAND,而是一种新的非易失性存储技术。3D XPoint技术还允许存储单元被堆叠到多个层中,这样就可以有效提升存储介质的容量。

3D-水平NAND Flash堆叠技术

基本思路实现对现有的NAND浮栅结构进行堆叠,获得与普通 NAND 浮栅相同的横向可扩展性和存储密度,另外采用氮化硅串接技术来代替浮栅的电荷捕获闪存方法。

串联存储器的存取可通过在低级非存储器中形成一个反型沟道来避免Cell的浮栅电容耦合。这种反型沟道及其相关耗尽区为存储介质中所捕获的电荷提供了高水平电荷保护,免受应用于这些底部存取器的传输电压的干扰。

此外,这种双栅结构是公认的良好横向可微缩性方法,它通过使顶部和底部设备之间实现密切的静电相互作用来消除短通道效应。

3D-垂直NAND Flash堆叠技术

三星电子推出独家专利3D V-NAND闪存技术,提升了产品的容量、速度和可靠性。3D V-NAND不是使用新工艺来缩小Cell单元和提供存储密度,而是选择了堆叠更多层数。

传统NAND Flash使用的是浮栅极Mosfet技术,充电/放电容易损坏栅极;三星采用控制栅极和绝缘层将Mosfet环形包裹起来提升了储存电荷的的物理区域,从而提高性能和可靠性。

3D V-NAND技术把Cell3D化,使得在垂直方向无限堆叠扩展,三星放弃了传统的浮栅极Mosfet,降低了写入时的电荷消耗,闪存寿命得到大幅提升,为未来SSD的发展开辟非常广阔的空间。

SSD接口技术

我们知道闪存磁盘是在HDD以后出现的,由于SSD优异的随机性能、越来越大的容量和越来越低的成本等优势,使得闪存热度上升、乃至替换HDD的趋势。由于历史继承性等原因,SSD在设计是也是借鉴了部分HDD技术,包含接口技术,现在绝大多数SSD都是采用SATA/SAS接口。SATA接口和AHCI(基于SATA接口和ATA数据指令)已是存储的性能瓶颈凸显,SCSI/SAS/FC接口(SCSI数据指令)组合在闪存中也是昨日黄花, NVMe指令和PCIe的组合将是未来趋势。

PCIe SSD存储接口

到目前为止,大部分存储厂商都推出了对应的PCIe闪存卡(如 EMC XtremSF PCIe SSD卡 )和磁盘。

Fusion-io开发的专利PCIe闪存卡(IO-Drive),可以加入到服务器中进而实现对应用的加速,并达到微秒级的低访问延迟。SATA/SAS则无论如何无法达到这个水平。因此,闪存浪潮下接口规范的重大变革势所难免。

NVM Express标准

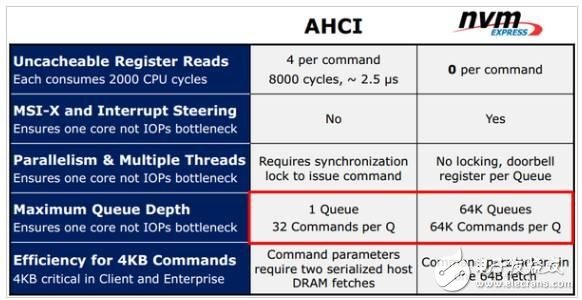

NVM Express是硬盘的新传输标准,是来取代为机械盘设计AHCI(高级主机控制器接口)的接口标准,AHCI无法发挥固态磁盘的优势,每条指令都需要读取4次寄存器,而VNMe不需要读取。从下面图上可以看出NVM Express的优势。

NVM Express是一个针对使用PCI Express SSD的企业和普通客户端系统开发的可扩展的主机控制芯片接口标准。该标准针对PCIe SSD定义了最优化的寄存器接口、指令集和功能集,并提供可扩展接口以实现SSD 技术现在和将来的性能潜力。NVMe走的是PCIE通道性能高,并且是统一的通信规范,只要服务器和PCIE接口卡都遵循NVMe规范, PCIE接口卡可以安装在任何服务器上而不用担心兼容性问题。

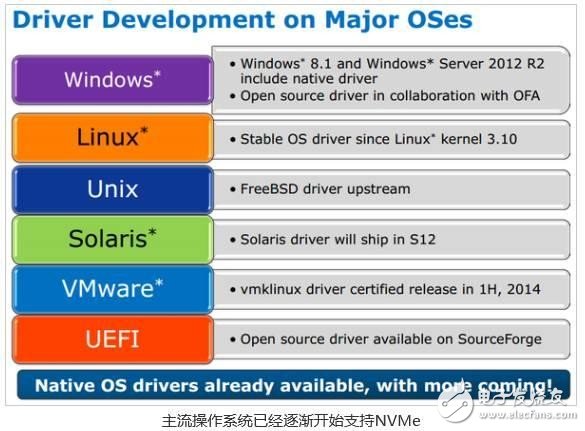

NVMe标准的也解决了不同PCIe SSD之间的驱动适用性问题。此前的PCIe SSD,均需要安装驱动程序后才能正常使用,而不同的厂商又各自为政,每个厂商产品都有自己的驱动,SSD也不能作为引导使用。但支持NVMe标准之后,PCIe SSD就可适用于多个不同平台,也不需要厂商独立提供驱动支持。目前Windows、Linux、Solaris、Unix、VMware、UEFI等都加入了对NVMe SSD的支持。

针对PCIe接口提出了NVMe标准(但NVMe的使用不仅限于PCIe)。该标准由包括IDT、Dell、Intel、EMC、NetApp、Oracle以及Cisco在内的13家发起企业主导,并由80余家业界领军公司合作开发。NVM Express是一个针对使用PCI Express SSD的企业和普通客户端系统开发的可扩展的主机控制芯片接口标准。该标准针对PCIe SSD定义了最优化的寄存器接口、指令集和功能集,并提供可扩展接口以实现SSD 技术现在和将来的性能潜力。这让原始设备制造商无需标准化多个SSD驱动器,从而加速PCIe SSD 的推广使用。

但是NVMe作为针对下一代存储设备提出的指令和协议规范,除了支持PCIe接口,VNMe规范可以应用到不同的硬件接口规范上。如支持U.2接口(即SFF-8639接口,包含4组PCIeLanes和2组SAS/SATA Lanes),SATA Express和M.2接口等等。另外,PCIe SSD并不一定支持NVMe规范,但是NVMe PCIe 是需要考虑符合NVMe规范。

东芝集团下存储解决方案提供商OCZ,推出了全新的基于NVMe技术的Z-Drive 6000系列SSD,结合了第三代PCIe和非易失性存储器专用(NVMe)技术,提供给系统集成商和存储供应商一个流线型的存储器接口、命令集、队列设计,用于快速访问关键性数据和获取高弹性的能力。

OCZ推出的Z-Drive 6000 SSD的产品有三种型号。它们包括带有2.5英寸的机箱大小和高达3.2TB的可用容量的Z-Drive 6000 SFF系列、性能略低但是可用容量高达6.4TB的Z-Drive 6300 SFF系列和带有半高、半长的插卡式外形,同时可用容量可以达到6.4TB的Z-Drive 6300 AIC系列。

NOR flash接口技术

传统NOR闪存带有SRAM接口(相比NAND Flash并行接口管脚多、需要统一编址,支持代码本地执行XIP,但容量比较小),可以在随意地址存入任意字节数据。

美光也开始探索串行NOR闪存接口。美光技术公司对传统NOR 闪存进行优化,推出全新XTREMFlash 串行NOR Flash存储器方案,具有每秒3.2 Gb的强大的数据读写能力,而且能够兼容目前所广泛使用的串行NOR闪存接口。在性能表现上超越除超大规模NAND闪存阵列之外的全部闪存存储方案类型。

XTRMFlash将提供并行、串行以及Quad-SPI型NOR闪存产品,且其针脚数量较现有并行NOR闪存将下降75%。兼容目前串行NOR闪存所普遍使用的Quad SPI闪存针脚设计。XTRMFlash能够以针脚兼容形式运行,而且只需对电路板稍加调整即可达成上述性能参数。

-

#硬声创作季 #可靠性 电子封装可靠性评价中的实验力学方法-3水管工 2022-09-29

-

#硬声创作季 #可靠性 电子封装可靠性评价中的实验力学方法-5水管工 2022-09-29

-

#硬声创作季 #可靠性 电子封装可靠性评价中的实验力学方法-6水管工 2022-09-29

-

最安全最全面的注册表清理器2008-06-16 0

-

[原创]最全面的protel99 元件库最近更新2009-02-25 0

-

史上最全面示波器教材2012-08-01 0

-

最经典最全面的嵌入式资料合集!!!2012-08-19 0

-

全面解析无线充电技术2016-07-28 0

-

最全面的继电保护知识2020-12-14 0

-

最全面的PROTEUS教程资料2009-04-23 1077

-

全面解析多点触控技术2017-01-14 886

-

最全面的电源电路图PCB+原理图汇总资料下载2018-03-29 1807

-

最全面的AD元器件封装库资料合集2020-11-05 3761

-

2021 QLC闪存会更普及:性能、可靠性追上TLC闪存,全面迈进100+层2020-12-25 1953

-

最全面的USB封装+FPC连接器封装.zip2023-03-01 455

全部0条评论

快来发表一下你的评论吧 !