关于外部时钟晶振频率选择方法

电子常识

描述

晶体振荡器是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振;而在封装内部添加IC组成振荡电路的晶体元件称为晶体振荡器。其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

晶振的使用

晶振,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低 的频率是串联谐振,较高的频率是并联谐振。由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶 振的两端并联上合适的电容它就会组成并联谐振电路。这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感的频率范围很窄, 所以即使其他元件的参数变化很大,这个振荡器的频率也不会有很大的变化。

晶振有一个重要的参数,那就是负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。

一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两端接入晶振,再有两个电容分别接到晶振的两端,每个电容的另一端再接到地,这两个电容串联的容量值就应该等于负载电容,请注意一般IC的引脚都有等效输入电容,这个不能忽略。

一般的晶振的负载电容为15p或12.5p ,如果再考虑元件引脚的等效输入电容,则两个22p的电容构成晶振的振荡电路就是比较好的选择。

晶振是为电路提供频率基准的元器件,通常分成有源晶振和无源晶振两个大类,无源晶振需要芯片内部有振荡器,并且晶振的信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确匹配外围电路(电感、电容、电阻等),如需更换晶振时要同时更换外围的电路。有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。

每种芯片的手册上都会提供外部晶振输入的标准电路,会表明芯片的最高可使用频率等参数,在设计电路时要掌握。与计算机用CPU不同,单片机现在所能接收的晶振频率相对较低,但对于一般控制电路来说足够了。

晶体振荡器也分为无源晶振和有源晶振两种类型。无源晶振与有源晶振(谐振)的英文名称不同,无源晶振为crystal(晶体),而有源晶振则叫做oscillator(振荡器)。无源晶振需要借助于时钟电路才能产生振荡信号,自身无法振荡起来,所以“无源晶振”这个说法并不准确;有源晶振是一个完整的谐振振荡器。

谐振振荡器包括石英(或其晶体材料)晶体谐振器,陶瓷谐振器,LC谐振器等。

晶振与谐振振荡器有其共同的交集有源晶体谐振振荡器。

石英晶片所以能做振荡电路(谐振)是基于它的压电效应,从物理学中知道,若在晶片的两个极板间加一电场,会使晶体产生机械变形;反之,若在极板间施加机械力,又会在相应的方向上产生电场,这种现象称为压电效应。如在极板间所加的是交变电压,就会产生机械变形振动,同时机械变形振动又会产生交变电场。一般来说,这种机械振动的振幅是比较小的,其振动频率则是很稳定的。但当外加交变电压的频率与晶片的固有频率(决定于晶片的尺寸)相等时,机械振动的幅度将急剧增加,这种现象称为压电谐振,因此石英晶体又称为石英晶体谐振器。 其特点是频率稳定度很高。

石英晶体振荡器与石英晶体谐振器都是提供稳定电路频率的一种电子器件。石英晶体振荡器是利用石英晶体的压电效应来起振,而石英晶体谐振器是利用石英晶体和内置IC来共同作用来工作的。振荡器直接应用于电路中,谐振器工作时一般需要提供3.3V电压来维持工作。振荡器比谐振器多了一个重要技术参数为:谐振电阻(RR),谐振器没有电阻要求。RR的大小直接影响电路的性能,也是各商家竞争的一个重要参数。

关于外部时钟晶振频率选择

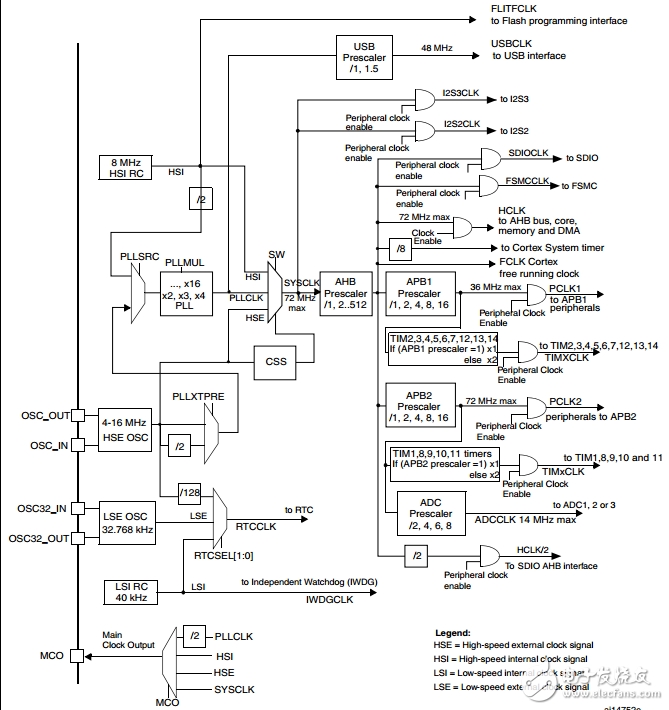

下图是时钟树(Figure 8. Clock tree),它完全地列出来STM32这个芯片内部各个模块的时钟来源以及相关的从属关系。

在这个图的正中央,有一个核心时钟:SYSCLK,它最大频率是72MHz,它的时钟信号通过选择器SW可以由PLLCLK提供(也可由HIS、HSE提供)。

PLL,毫无疑问,它是用来倍频的,可以*2,*3,*4……*16,它的时钟信号通过选择器PLLSRC可以由8MHz的高速内部RC振荡器经过二分频提供,也可由PLLXTPRE的选择器输出提供,

而PLLXTPRE的选择器就接的是我们的8MHz的高速外部时钟(直接接入或二分频接入)。

总的来说,对于我们这个板子,若使用高速外部时钟给STM32内核提供时钟源,一般以下两条路:

① [高速外部时钟:8MHz]》》》[不分频:8MHz]》》》》[PLL倍频,2到16倍]》》》[SYSCLK,16MHz-128MHz]

②[高速外部时钟:8MHz]》》》[二分频:4MHz]》》》》[PLL倍频,2到16倍]》》》[SYSCLK,8MHz-64MHz]

我们注意到,在8MHz外部时钟给PLL之前若分频的话,那么最大(×16)才64MHz,因此,我们都会给PLL以8MHz的时钟源让其倍频,这样能使它发挥到72MHz的高频率

正因如此,系统时钟总是8的倍数。

我们看这个芯片的数据手册,立刻就能明白,不是必须得接8MHz的晶振的

① 高速外部时钟源频率范围(P55-P58):1MHz~25MHz(有源);4MHz~16MHz(无源)

② PLL输入时钟源频率范围(P62):1MHz-25MHz

③ PLL输出时钟源频率范围(P62):16MHz~72MHz

我们自己设计板子的时候只要满足它的范围就可以了。

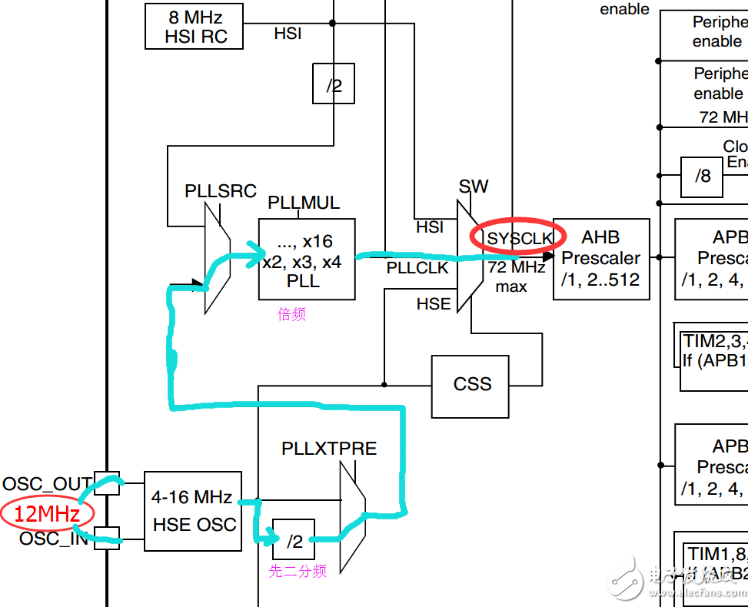

例如:我们可以选择一个12MHz的无源晶体接到STM32芯片上。

在给STM32进行时钟配置的时候,

① 选择PLLXTMRE的输入源为12MHz/2 = 6MHz

② 选择PLLSRC的输入源为PLLXTMRE的输出6MHz,

③ 在PLL内进行3到12倍的倍频(最小16MHz,最大72MHz),

最终我们可选择的频率就有:18MHz、24MHz、30MHz、36MHz、42MHz、48MHz、54MHz、60MHz、66MHz、72MHz

图示:

- 相关推荐

- 晶振

-

请问F28035使用外部有源晶振时和使用内部晶振在寄存器的配置上除了选择外部晶振源还有其他的注意事项吗?2018-06-14 0

-

OMAP的SYSBIOS是如何识别外部晶振频率的?2018-06-21 0

-

请问AD9956如果选择直接用外部晶振时钟对晶振的频率有要求吗?2018-08-15 0

-

F28377D内部晶振与外部晶振问题2018-10-11 0

-

请问AD9956若选择直接用外部晶振时钟,对晶振的频率有要求吗?2019-01-15 0

-

FAQ0093 AT32更换外部晶振后BSP修改方法2021-02-19 0

-

有关晶振频率的选择问题2021-07-13 0

-

使用外部晶振的方案配置RTC2021-08-09 0

-

STM32外部晶振和内部晶振是如何进行切换的2021-08-10 0

-

关于STM32 RTC时钟使用内部/外部晶振的切换方法 精选资料推荐2021-08-12 0

-

stm32的时钟通过pll锁相环把外部晶振的频率顶上去2021-08-12 0

-

选择外部时钟晶振频率的方法2021-11-25 0

-

STM32时钟源和晶振的相关资料分享2022-01-26 0

-

请问AD9956如果选择直接用外部晶振时钟,对晶振的频率有要求吗?2023-12-13 0

-

关于外部时钟晶振频率选择2021-11-16 878

全部0条评论

快来发表一下你的评论吧 !