基于74ls192设计4/7进制计数器详解

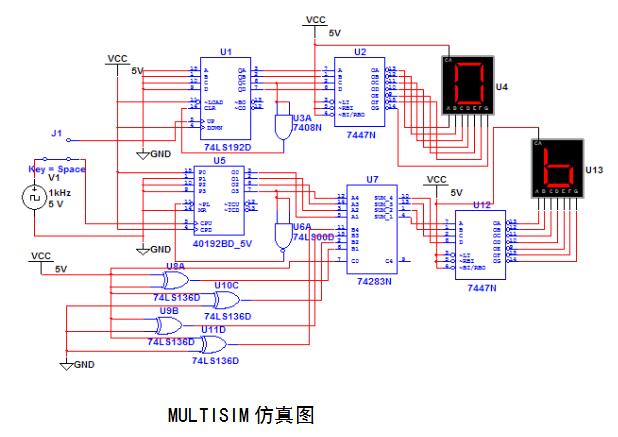

IC应用电路图

描述

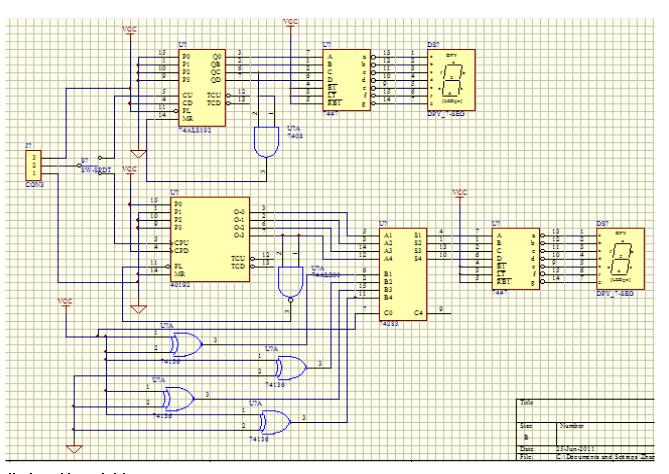

由题目及其要求分析可知,首先要使用74LS192或40192设计一个4进制计数器和一个7进制计数器,然后通过数码管来显示状态。两种进制间的切换可以通过一个单刀双掷开关来实现。其重点和难点在于设计一个4进制计数器和一个7进制计数器。

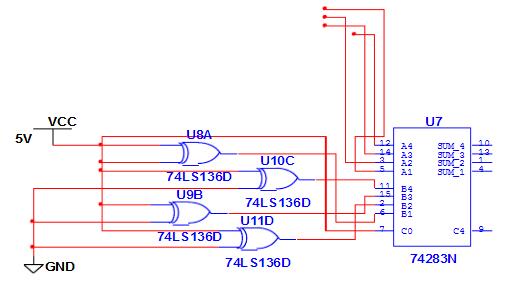

通过分析74LS192和40192的特点,发现可以使用清零法来设计一个4进制计数器,而7进制则不能直接通过置数或者清零获得。因此我选择采用置数法将74LS192或40192设计的从0到7的8进制计数器改装为从1到7的计数器,然后再通过一个减法器使从1到7的计数器变为从0到6的7进制计数器。而减法器可以使用集成加法器和四个异或门来实现。

在本课程设计中,主要用到了74LS192计数器、7447译码器、74LS00与非门、7408与门、74LS136异或门、74283加法器、七段数码显示器和一个单刀双掷开关等元器件。

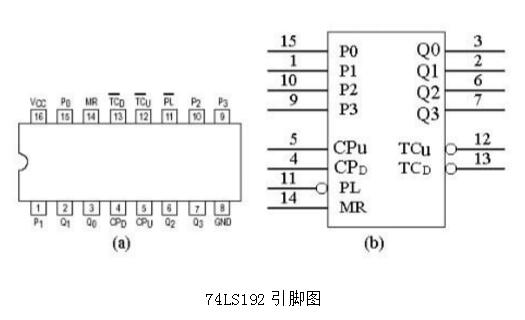

一、十进制同步可逆计数器74LS192 功能如下:

1、异步清零。74LS192的输入端异步清零信号CR,高电平有效。仅当CR=1时,计数器输出清零,与其他控制状态无关。

2、异步置数控制。LD非为异步置数控制端,低电平有效。当CR=0,LD非=0时,D1D2D3D4被置数,不受CP控制。

3、加法计数器,当CR和LD非均无有效输入时,即当CR=0、LD非=1,而减数计数器输入端CPd为高电平,计数脉冲从加法计数端CPu输入时,进行加法计数;当CPd和CPu条件互换时,则进行减法计数。 4. 保持。当CR=0、LD非=1(无有效输入),且当CRd=CPu=1时,计数器处于保持状态。

5、进行加计数,并在Q3、Q0均为1、CPu=0时,即在计数状态为1001时,给出一进位信号。进行减计数,当Q3Q2Q1Q0=0000,且CPd=0时,BO非给出一错位信号。这就是十进制的技术规律。

在设计过程中,我主要利用74LS192的计数功能,通过置数法和清零法将其改造为一个4进制计数器和一个7进制计数器。

二、显示译码器

七段数码显示器

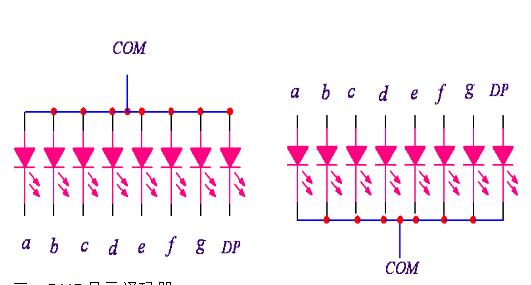

七段式数码显示器是目前使用最广泛的一种数码显示器。这种数码显示器有分布在同一平面的七段可发光的线段组成,可用来显示数字、文字、符号。最常用的七段数码显示器有半导体数码管和液晶显示器两种。根据发光二极管的连接形式不同,分为共阴极显示器和共阳极显示器(如图)。共阴极显示器将七个发光二极管的阴极连接在一起,作为公共端。在电路中,将公共端接于低电平,将某段二极管的阳极为高电平时,相应段发光。共阳极的显示方式和共阴极相反。

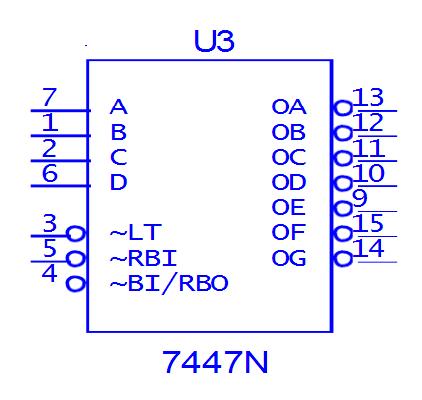

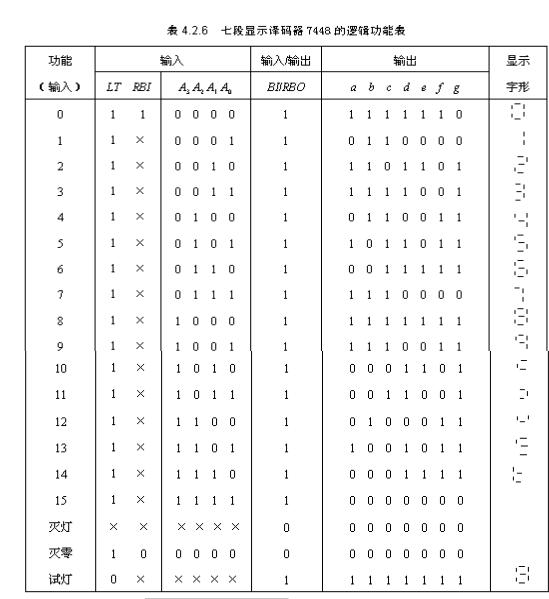

三、7447显示译码器

七段显示器译码器把输入的BCD码,翻译成驱动七段LED数码管各对应段所需的电平。七段显示译码器7447是一种与共阴极数字显示器配合使用的集成译码器。它用于对十进制数的8421BCD码进行译码,以驱动七段显示器显示十进制数字。其输入为8421BCD码,输出高电平有效,可直接驱动阴极显示器,其功能表和7448的功能表一样如图所示,表中10~15六个状态一般不用。除了译码输入、输出外,7447还有三个辅助控制端,以增强器件功能。

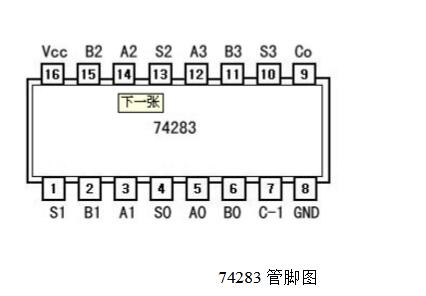

四、74283加法器

每一位的进位信号送给高位作为输入信号,因此,任一位的加法运算必须在低一位的运算完成之后才能进行,这种进位方式成为串行进位,这种加法器的逻辑电路较为简单。

五、电路设计及计算

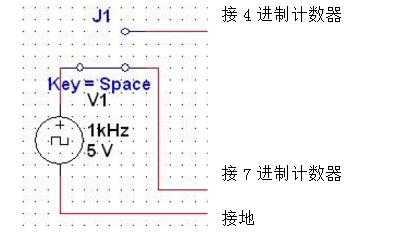

1、选择一个方波信号发生器作为输入信号源;

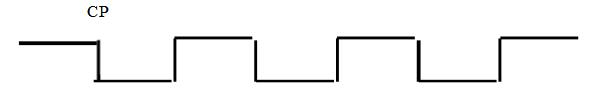

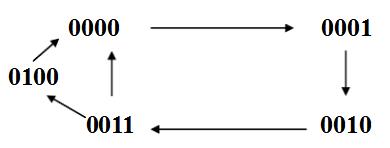

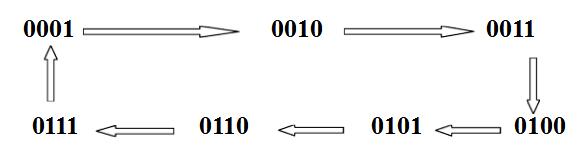

2、利用74LS192,通过清零法设计一个四进制计数器,状态图如下:

3、利用74S192通过置数法设计一个从1到7的计数器,状态图如下:

然后通过减法器在每一个状态的基础上减去一个1,从而实现一个7进制计数器。

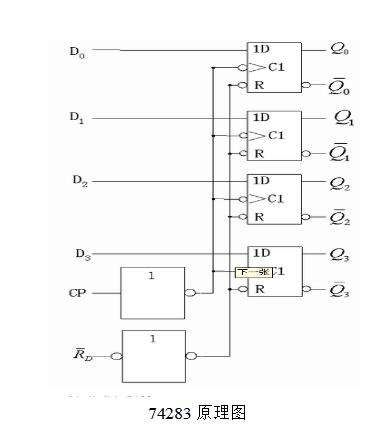

减法器电路如图所示

4、通过一个单刀双掷开关控制信号源,从而进行四进制和七进制之间的转换。

5、进行四进制计数时,在74LS192后面接一个7447显示译码管,将8421BCD码转换成十进制,最后通过一个七段显示数码管来显示数据输出状态。

6、在进行七进制计数时,用40192进行置数法计数,预置数为0001,计数到1000后反馈到置数端,循环计数,后面接一个74238加法器构成的减法器,使输出显示数字在0000~0110之间计数,在经过7447译码管将其转化为十进制数0~6,从而实现七进制计数器功能。

六、原理图、仿真图及结果分析、PCB版图

原理图如下所示:

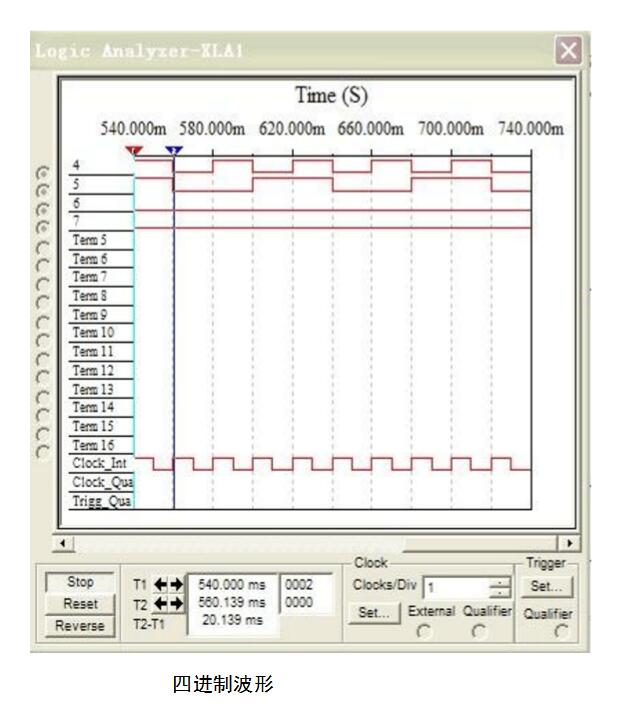

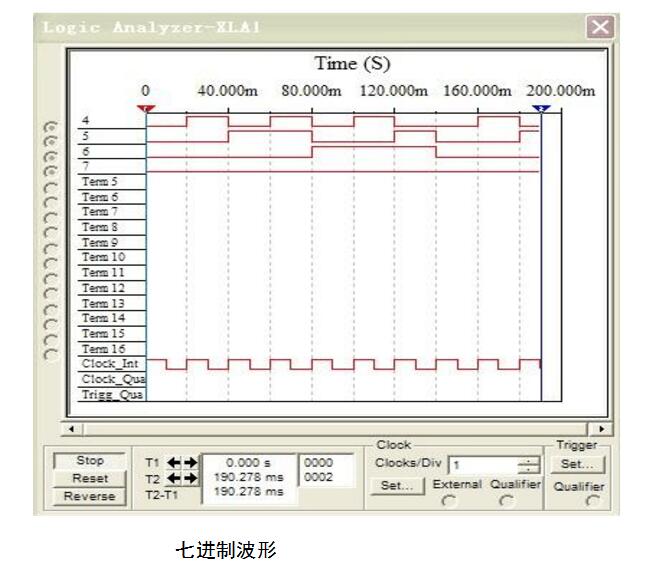

仿真及结果分析

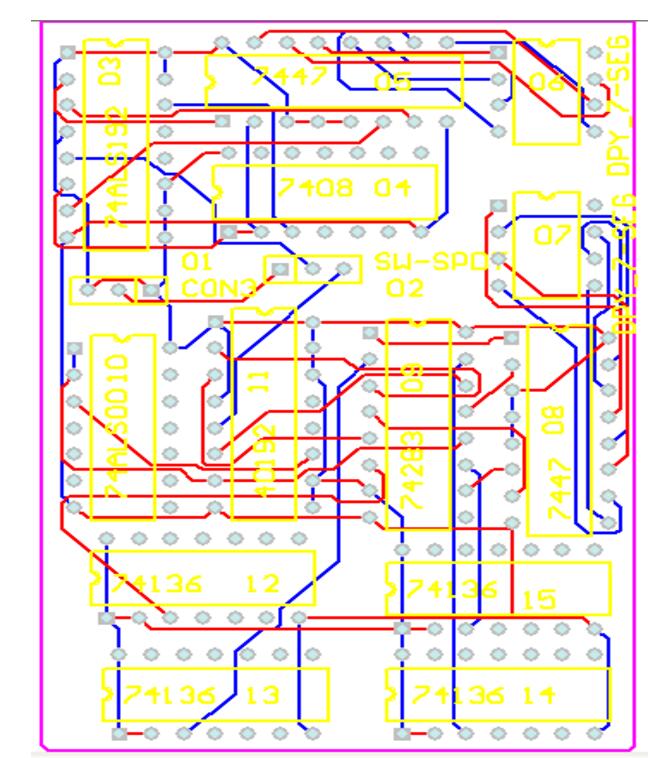

七、PCB板排布

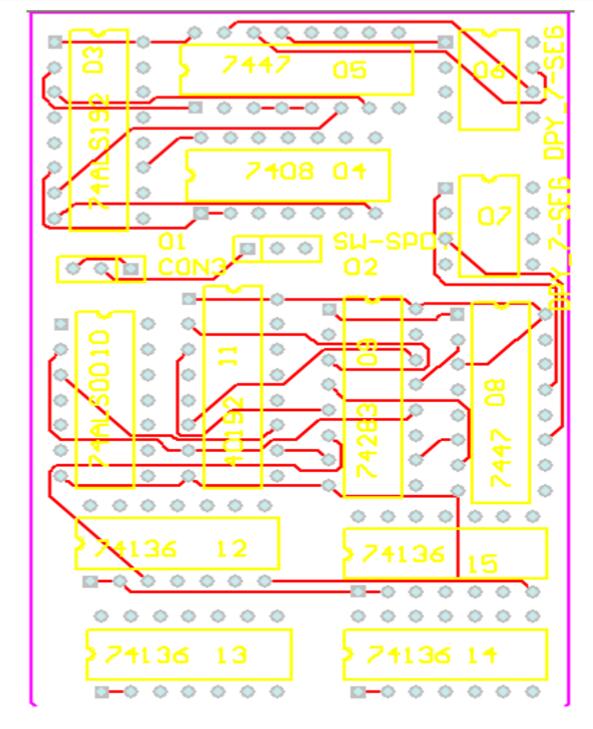

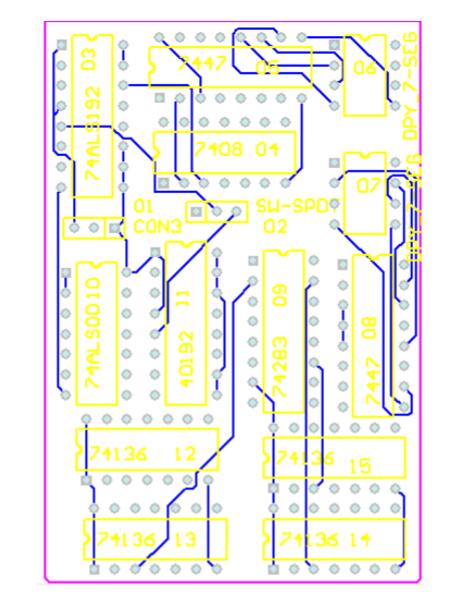

1、PCB原理图如下

pcb板顶层

PCB板底层

- 相关推荐

- 74LS192

-

计数器设计目的2021-07-29 0

-

如何去实现基于74ls192芯片和与非门的进制加法计数器设计呢2021-11-02 0

-

74LS192中文资料pdf2008-03-18 6498

-

74LS192 pdf datasheet2008-08-06 1651

-

十进制可逆计数器74LS192引脚图管脚及功能表2011-05-19 121472

-

74LS192 英版数据手册2016-08-31 1606

-

74ls192和74ls160的区别有哪些2017-12-21 32288

-

74ls192工作原理详解_使用说明_内部逻辑图及应用电路2017-12-21 252444

-

基于74LS192千进制可逆计数器的设计与研究2017-12-21 8201

-

利用74ls192的倒计时计数器2017-12-21 103630

-

基于74LS192的任意进制计数器的设计2017-12-21 95760

-

两个74LS192级联构成两位十进制计数器2018-05-09 56689

-

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)2018-05-28 126042

-

74ls192的功能及原理2024-01-22 3147

-

74LS192/74LS193计数器数据手册2024-02-18 239

全部0条评论

快来发表一下你的评论吧 !