74LS148的4路抢答器

IC应用电路图

描述

抢答器是通过设计电路,以实现如字面上意思的能准确判断出抢答者的电器。在知识竞赛、文体娱乐活动(抢答赛活动)中,能准确、公正、直观地判断出抢答者的座位号。更好的促进各个团体的竞争意识,让选手门体验到战场般的压力感。

传统抢答器只是大概判断出抢答成功或犯规选手台号,无法显示出每个选手的抢答时间。而今抢答器可以通过数据来说明裁决结果的准确性、公平性。使比赛大大增加了娱乐性的同时,也更加公平、公正。新增无线抢答器更是抢答器史上的一大改革。

本文主要介绍一下基于74LS148的4路抢答器的设计详解,一起来了解一下。

一、 设计任务和要求:

1.1、设计任务

设计一台可供4名选手参加比赛的智力竞赛抢答器。 用数字显示抢答倒计时间,由“9”倒计到“0”时,无人抢答,蜂鸣器鸣响。选手抢答时,数码显示选手组号,同时蜂鸣器鸣响,倒计时停止。

1.2、设计要求

1) 4名选手编号为:1,2,3,4。各有一个抢答按钮,按钮的编号与选手

的编号对应,也分别为1,2,3,4。

2) 给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭

灯)和抢答的开始。

3) 抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答

按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时扬声器给出音响提示,封锁输入编码电路,禁止其他选手抢答。抢答选手的编号一直保持到主持人将系统清零为止。抢答器具有定时(15秒)抢答的功能。

4) 当主持人按下开始按钮后,定时器开始倒计时,定时显示器显示倒计

时间,若无人抢答,倒计时结束时,扬声器响。参赛选手在设定时间(15秒)内抢答有效,抢答成功,扬声器响,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止。

5) 如果抢答定时已到,却没有选手抢答时,本次抢答无效。系统扬声器

报警,并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。 6) 用石英晶体振荡器产生频率为1Hz的脉冲信号,作为定时计数器的CP信号。

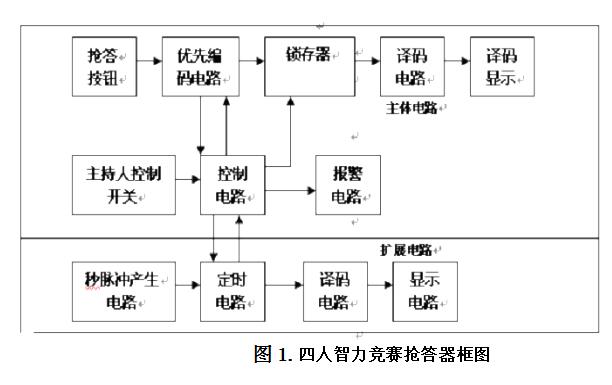

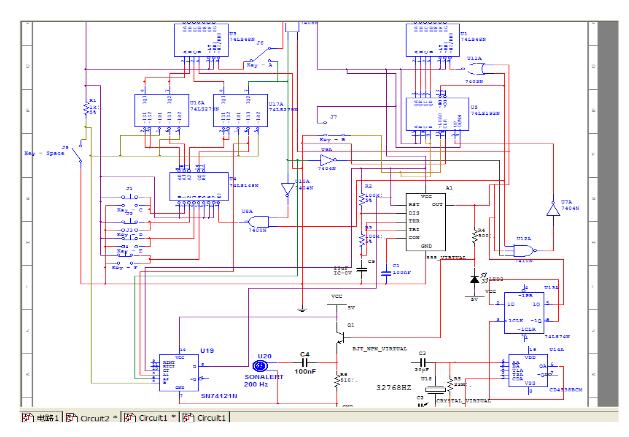

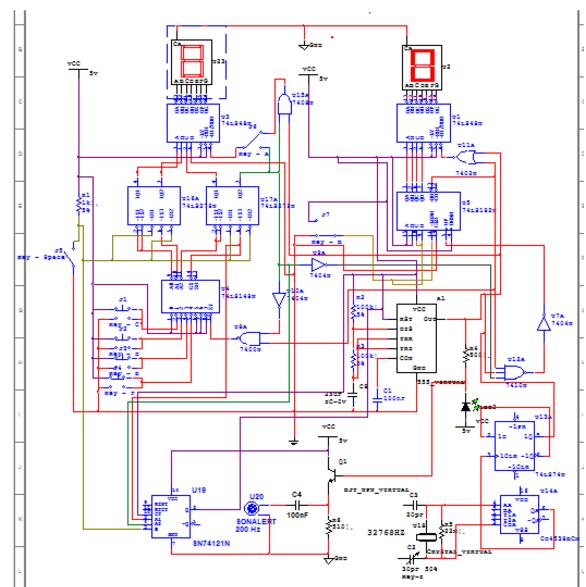

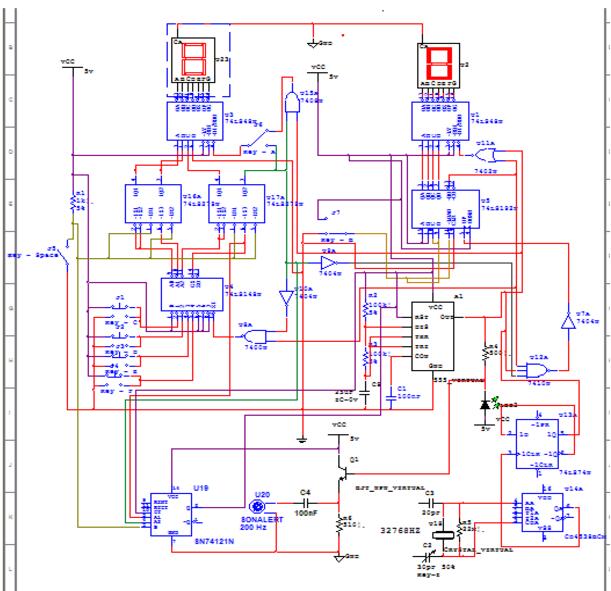

二、设计总方案

本设计电路主要由控制电路、脉冲产生电路、锁存电路、编码及译码显示电路、倒计时电路和报警产生电路组成。如图1所示为总体方框图。其工作原理为:接通电源后,主持人将开关拨到“清零”状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置;开始“状态,宣布”开始“抢答器工作。定时器倒计时。选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示。当一轮抢答之后,定时器停止、禁止二次抢答、定时器显示剩余时间。如果再次抢答必须由主持人再次操作”清除“和”开始“状态开关。

三、电路设计计算与分析

3.1 抢答器控制电路设计

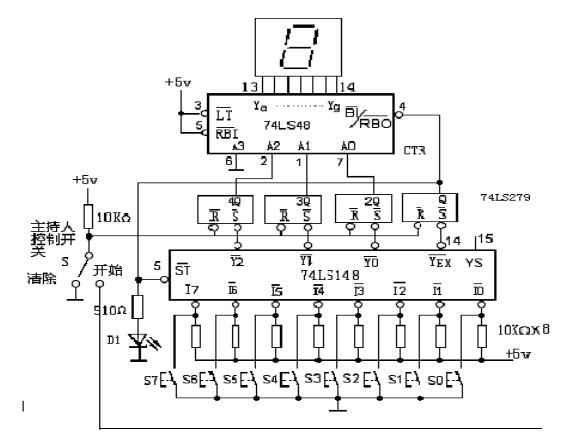

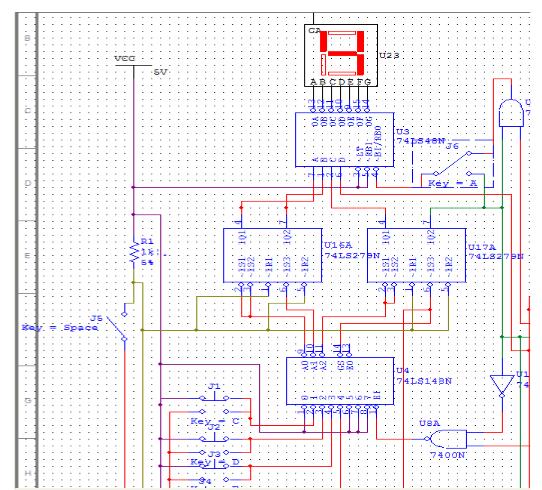

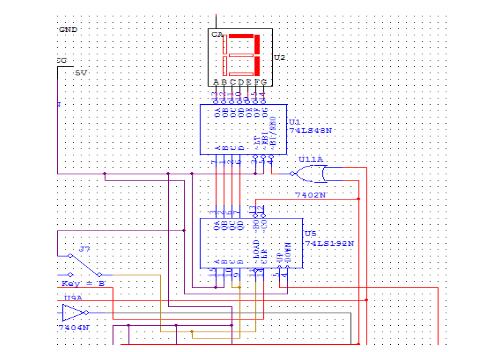

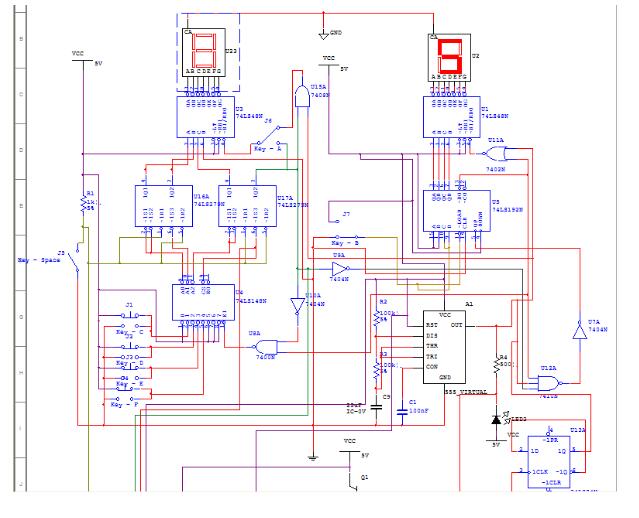

设计电路见图2所示。电路选用优先编码器 74LS148 和锁存器 74LS279 来完成。

抢答器控制电路是抢答器设计的关键,它要完成以下三项功能:

1) 当参赛选手按动抢答键时,扬声器发声,抢答电路和定时电路停止工作,

同时译码显示电路显示编号(显示电路采用七段数字数码管显示)。

2) 当设定的抢答时间到,无人抢答时,扬声器发声,同时抢答电路和定时电路停止工作。

3)当主持人清零后,可再次进行抢答。

工作过程:

开关J5置于“清除”端时,RS触发器的 R、S端均为0,4个触发器输出置0,使74LS148的优先编码工作标志端(图中5号端)=0,使之处于工作状态。当开关J5断开,J6置于“开始”时,抢答器处于等待工作状态,当有选手将抢答按键按下时(如按下J2),74LS148的输出经RS锁存后,CTR = 1,RBO(图中4端) =1,七段显示电路74LS48处于工作状态,4Q3Q2Q = 010,经译码显示为“2”。此外,CTR=1,使74LS148 优先编码工作标志端(图中2号端)=1,处于禁止状态,封锁其他按键的输入。当按键松开即按下时,74LS148的 此时由于仍为CTR=1,使优先编码工作标志端为1,所以74LS148仍处于禁止状态,确保不会出二次按键时输入信号,保证了抢答者的优先性。如有再次抢答需由主持人将J5开关重新置“清除”然后才可能进行。

仿真结果

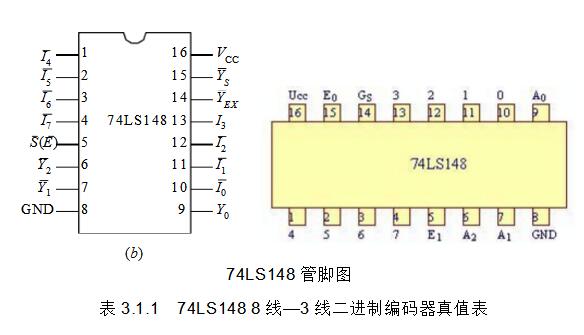

3.1.1、优先编码器 74LS148

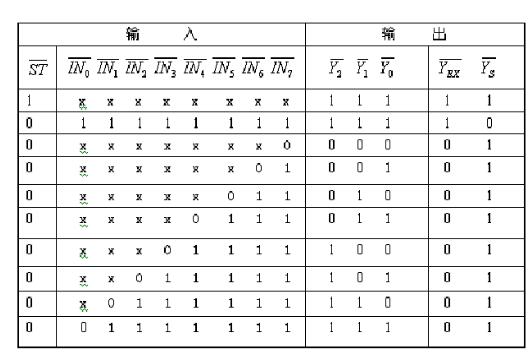

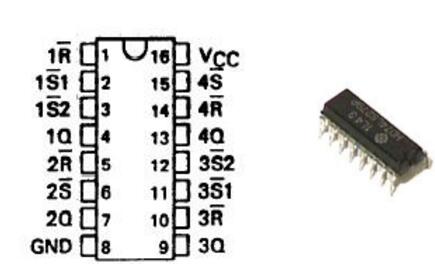

74LS148为8线-3线优先编码器,表3.1.1为其真值表,下图为其管脚图。

74LS148工作原理如下:

该编码器有8个信号输入端,3个二进制码输出端。此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。当EI=0时,编码器工作;而当EI=1时,则不论8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。这种情况被称为输入低电平有效,输出也为低电来有效的情况。当EI为0,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS为0。表明编码器处于工作状态,否则为1。

由功能表可知,在8个输入端均无低电平输入信号和只有输入0端(优先级别最低位)有低电平输入时,A2A1A0均为111,出现了输入条件不同而输出代码相同的情况,这可由GS的状态加以区别,当GS=1时,表示8个输入端均无低电平输入,此时A2A1A0=111为非编码输出;GS=0时,A2A1A0=111表示响应输入0端为低电平时的输出代码(编码输出)。EO只有在EI为0,且所有输入端都为1时,输出为0,它可与另一片同样器件的EI连接,以便组成更多输入端的优先编码器。

从功能表不难看出,输入优先级别的次为7,6,„„,0。输入有效信号为低电平,当某一输入端有低电平输入,且比它优先级别高的输入端无低电平输入时,输出端才输出相对应的输入端的代码。例如5为0。且优先级别比它高的输入6和输入7均为1时,输出代码为010,这就是优先编码器的工作原理。

3.1.2 锁存器74LS279

原理:在74ls279中,由于4回路中2回路置位端子为两个,所以使用其一时,整理两个置位输入作为1个使用,或将另一个输入固定为“H”使用。另外,作为稍微变化74LS279 的使用方法,也可将3组作为RS锁存器使用,剩余的RS锁存器作为2输入NAND门电路使用,复位输入例如①管脚固定为”L”时其输入为“H”,所以可构成将②和③作为输入,输出为④的2输入NAND,此变换如图4.2.所示。

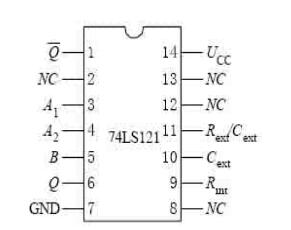

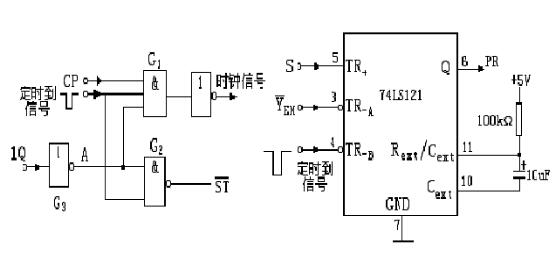

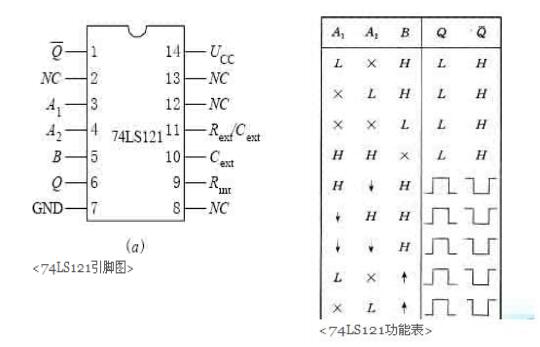

3.1.3 74LS121单稳态触发器:

3.2 定时时间电路的设计

原理及设计:

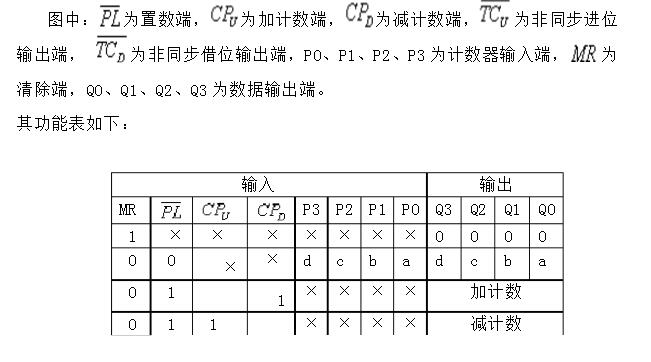

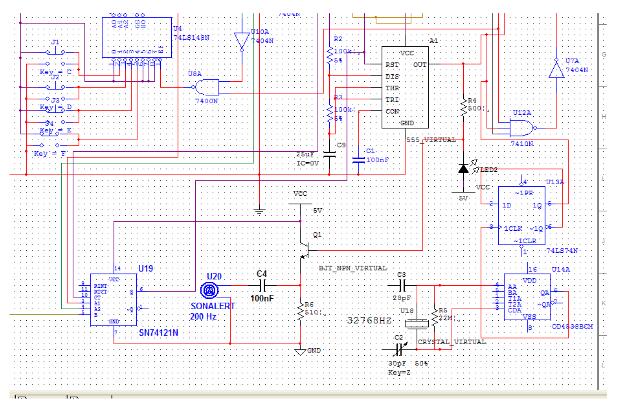

该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、74LS48译码电路和1个7段数码管即相关电路组成。具体电路如图3所示。一块74LS192实现减法计数,通过译码电路74LS48显示到数码管上,其时钟信号由时钟产生电路提供。74192的预置数控制端实现预置数,由节目主持人根据共阴极七段数码显示管DPY_7-SEG 上,当有人抢答时,停止计数并显示此时的倒计时时间;如果没有人抢答,且倒计时时间到时, 输出低电平到时序控制电路,控制74LS48使0闪烁,同时以后选手抢答无效。 由555定时器产生时间基准信号秒脉冲。振荡周期为15秒脉冲信号经两级有预置功能的可逆十进制计数器74LS192对时钟信号进行计数,当计数到达预置的时间,计数器产生溢出而封锁计数脉冲,使计数器停止计数。数码管指示时间值。

具体电路如下图:

仿真结果

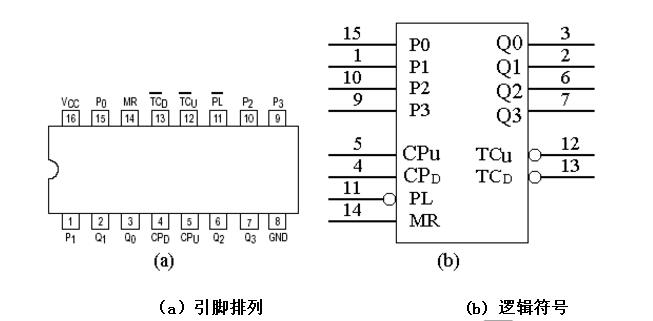

3.2.1 计数器74LS192

十进制可逆计数器74LS192(54/74194)两个引脚图管脚及功能表如下:74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

3.3 控制电路和报警电路

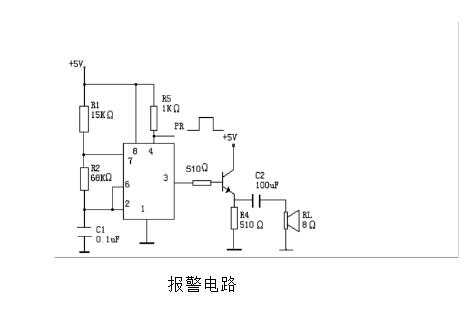

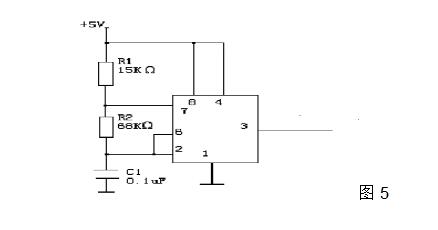

由555 芯片构成多谐振荡电路,震荡频率 f=1/(R1+R2)C㏑2≈1.43/(R1+R2)C

555 的输出信号再经或门控制显示闪烁。控制电路包括时序和报警两个电路,如图所示。控制电路需具有以下几个功能:

1、主持人闭合开关,多路抢答器电路和计时电路进入正常状态;

2、参赛者按键时,抢答电路和计时电路停止工作;

3、抢答时间到,无人抢答,0闪烁 ,抢答电路和计时电路停止工作。

由功能表可以看出,要使电路实现倒计时(减法)功能,应使CR=0,PE非=1,CP+=1,CP-=CP。可用CR端接电平开关来控制计时器的工作与否。 闪烁显示电路需要在一种情况下做出反应当裁判员给出“请回答”指令后,计时器开始倒计时,若回答问题时间到达限定的时间,扬声器发声及灯闪烁。

控制电路由两部分组成:

一是由门电路组成的抢答与定时控制的时序控制电路,二是74LS121驱动报警电路的时序电路。

门控电路主要由或门组成,它的两个输入,一个来自由555 芯片构成多谐振荡电路,另一个来自计时系统高位计数器的借位信号QB,它说明计时电路在3秒,2秒,1秒,0秒倒计时再向9秒转化时向高位借位时给出一个负脉冲经反相器得到一个高电平。这个高电平信号或上方波信号就使显示器闪烁。

集成单稳态触发器74LS121用于控制报警电路及发声的时间,具体原理如下:主要由555时钟电路(用于控制报警声音频率)、蜂鸣器即相关的延时电路和控制电路组成。单稳态触发器74121通过信号/Ys、BO2、S控制报警与否和报警时间,555时钟电路产生脉冲时钟。在规定的时间有人抢答时,/Ys由1跳变到0,74121有状态2,即Q输出暂态高电平,蜂鸣器连续发声报警,持续时间为 =2.15秒;如果在规定时间内无人抢答,BO2由1跳变到0,74121有状态1。

Q输出暂态高电平,蜂鸣器连续发声报警持续时间为

结合警电路,分析 计算如下: 。取C=100uF, R=25K,。有=2.15秒。

仿真结果

1、倒计时

2、时间到,蜂鸣器响,绿灯闪烁

3.3.1 振荡电路

本系统需要产生频率为500KHZ的脉冲信号,用于触发器的CP信号,及频率为1HZ信号用于计时电路。以上电路可用555定时器组成,也可用石英晶体组成的振荡器经过分频得到。

主要参数:电源电压为4.5-18V,最大输出电流为200mA,工作温度范围为-55oC-125oC。

3.3.2 74LS121单稳态触发器

3.4 整体仿真

- 相关推荐

- 74LS148

-

数字抢答器设计毕业论文2009-03-20 0

-

数字抢答器设计2009-03-20 0

-

proteus中74LS148的问题2013-01-24 0

-

8路抢答器电子设计2013-08-18 0

-

四路抢答器的设计2016-12-20 0

-

数字抢答器2017-05-24 0

-

请问利用多片74ls148八-三编码器怎么完成88路数据输入的编码2019-03-11 0

-

74ls148中文资料pdf下载2008-03-06 1860

-

基于8051的Proteus仿真-74LS148扩展中断2016-09-06 710

-

74ls148做八路抢答器2017-11-07 49087

-

74ls148可以用什么代替2018-02-01 7806

-

74ls147和74ls148有什么区别2018-05-07 32506

-

74ls148应用电路图大全(优先编码器\抢答器)2018-05-07 38037

-

使用74LS148设计的抢答器仿真电路免费下载2018-12-20 3236

全部0条评论

快来发表一下你的评论吧 !