8-3线优先编码器74LS148的级联分析

IC应用电路图

描述

74LS148是带有扩展功能的8-3线优先编码器,它有8个信号输入端,3个二进制码输出端,一个输入使能端,一个选通输出端和一个扩展端。使能端为“0”时,该芯片被选中,否则不被选中。选通输出端和扩展端主要用于功能扩展。

1、74LS148简介

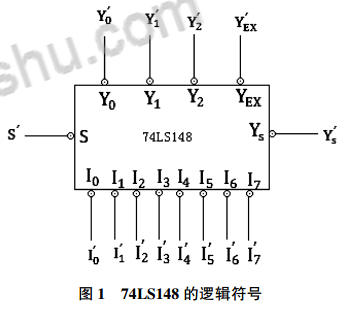

图1是74LS148的逻辑符号,其中,I′0—I′7 是8个信号输入端,Y′2—Y′0是3个二进制码输出端,S′是输入使能端,Y′S是选通输出端,Y′EX是扩展端,其逻辑功能表如表1所示。

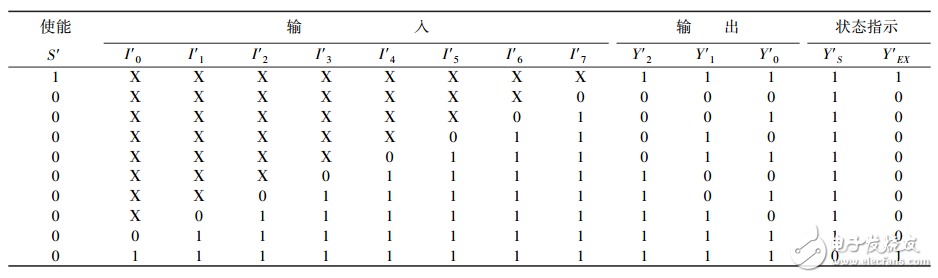

表1 74LS148的逻辑功能表

表1中的Χ代表0、1中的任何数,从表1可以看出,编码输入I′0-I′7低电平有效,且I′7的优先级别最高,I′0的优先级别最低,使能端S′为“0”时,该芯片被选中,否则不被选中,电路处于禁止工作状态时,Y′SY′EX=11,电路处于工作状态时,Y′SY′EX=10,电路处于工作状态但无编码输入时,Y′SY′EX=01。

2、用两片74LS148构成16-4线优先编码器

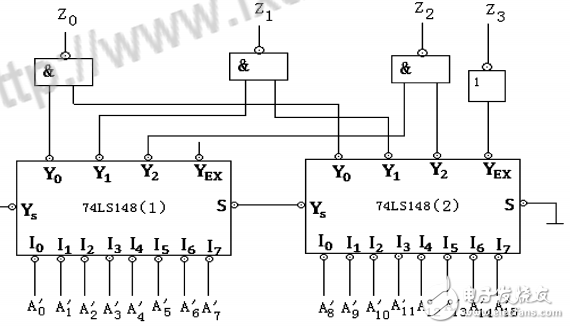

两片74LS148有16个输入端,可以构成16-4线优先编码器,在构成16-4线优先编码器时,低位片74LS148(1)的I′0-I′7作为16-4线优先编码器码器的低8位输入端A′0-A′7,高位片74LS148(2)的I′0-I′7作为16-4线优先编码器码器的高8位输入端A′8-A′15,16-4线优先编码器应该有4个输出端,可将74LS148(2)的Y′EX端通过与非门连接,非门的输出端作为16-4线优先编码器的Z3输出端,两片的Y′2端接与非门的输入端,与非门的输出端作为16-4线优先编码器的Z2输出端,两片的Y′1端接与非门的输入端,与非门的输出端作为16-4线优先编码器的Z1输出端,两片的Y′0端接与非门的输入端,与非门的输出端作为16-4线优先编码器的Z0输出端,并把高位片的S′接低电平,这样可构成16-4线优先编码器,图2为两片74LS148构成16-4优先编码器。

图2 两片74LS148构成16线-4线优先编码器

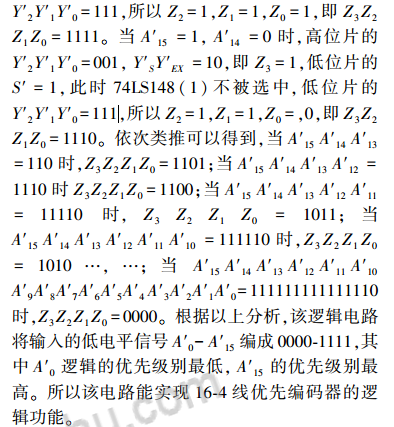

下面对图2的工作原理进行分析:由于74LS148(2)的S′接地,它满足S′为低电平的要求,74LS148(2)被选中,当A′15=0时,高位片的Y′2Y′1Y′0=000,Y′SY′EX=10,即Z3=1,低位片的S′=1,此时74LS148(1)不被选中,低位片的

3、用3片74LS148构成24-5线优先编码器

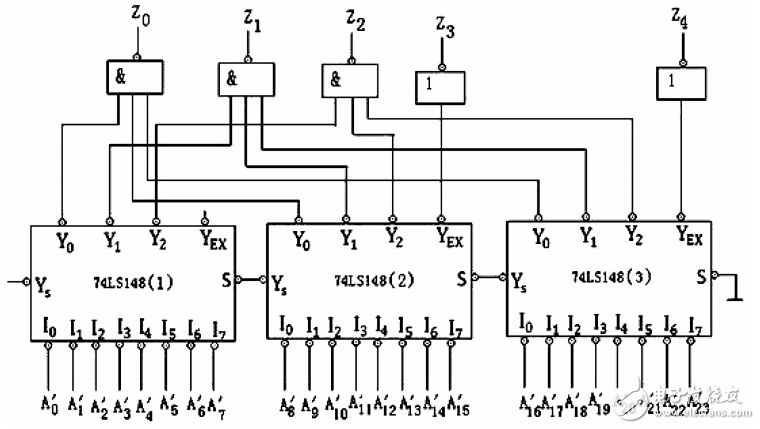

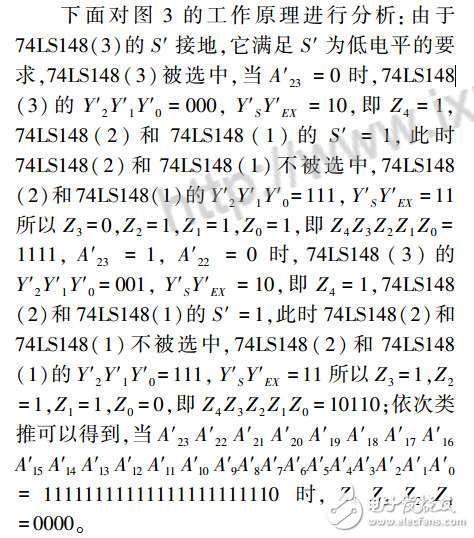

3片74LS148有24个输入端,可以构成24-5线优先编码器,在构成24-5线优先编码器时,最低位片74LS148(1)的I′0-I′7作为24-5线优先编码器码器的最低8位输入端A′0-A′7,次低位片74LS148(2)的I′0-I′7作为24-5线优先编码器码器的次低8位输入端A′8-A′15,高位片74LS148(3)的I′0-I′7作为24-5线优先编码器码器的高8位输入端A′16-A′23,24-5线优先编码器应该有5个输出端,可将74LS148(3)的Y′EX端通过与非门连接,非门的输出端作为24-5线优先编码器的Z4输出端,74LS148(2)的Y′EX和74LS148(3)的Y′EX接与非门的输入端,与非门的输出端作为24-5线优先编码器的Z3输出端,3片的Y′2端接与非门的输入端,与非门的输出端作为24-5线优先编码器的Z2输出端,3片的Y′1端接与非门的输入端,与非门的输出端作为24-5线优先编码器的Z1输出端,3片的Y′0端接与非门的输入端,与非门的输出端作为24-5线优先编码器的Z0输出端,并把高位片74LS148(3)的S′接低电平,这样可构成24-5线优先编码器,图3为3片74LS148构成的24-5线优先编码器。

图3 3片74LS148构成的24-5线编码器

根据以上分析,该逻辑电路将输入的低电平信号A′0-A′23编成00000-10111,其中A′0逻辑的优先级别最低,A′23的优先级别最高,所以该电路能实现24-5线优先编码器的逻辑功能,由于5个输出端,可以用5位二进制代码来表示,5位二进制代码有32种取值组合,我们可以选择32种中的任意24种来对A′0-A′23进行编码,根据选择的不同,可以形成不同的编码方式,这样可以得到不同的实现24线-5线优先编码器的逻辑功能的逻辑电路,另外,也可以用3片74LS148构成23-5线、22-5线、21-5线、20-5线码器,在构成23-5线优先编码器时,把图3中的A′23接高电平即可,在构成21-5线优先编码器时,把图3中的A′23、A′22接高电平,其它依次类推。

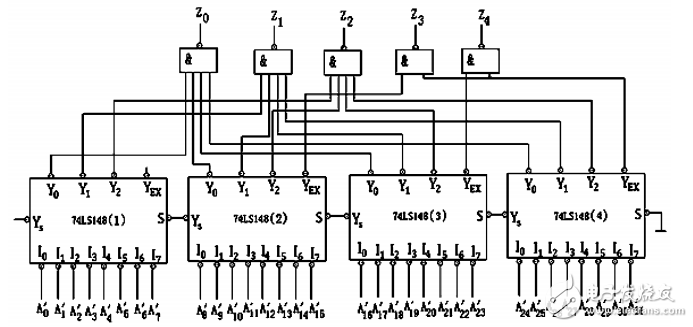

4、用4片74LS148构成32-5线优先编码器

4片74LS148有32个输入端,可以构成32-5线优先编码器,在构成32-5线优先编码器时,74LS148(1)的I′0-I′7作为32-5线优先编码器码器的A′0-A′7输入端,74LS148(2)的I′0-I′7作为32-5线优先编码器码器的A′8-A′15输入端,74LS148(3)的I′0-I′7作为32-5线优先编码器码器的A′16-A′23输入端,74LS148(4)的I′0-I′7作为32-5线优先编码器码器的A′24-A′31输入端,32-5线优先编码器应该有5个输出端,可将74LS148(3)和74LS148(4)的Y′EX端接与非门的输入端,与非门的输出端作为32-5线优先编码器的Z4输出端,74LS148(2)的Y′EX和74LS148(4)的Y′EX接与非门的输入端,与非门的输出端作为32-5线优先编码器的Z3输出端,4片的Y′2端接与非门的输入端,与非门的输出端作为32-5线优先编码器的Z2输出端,3片的Y′1端接与非门的输入端,与非门的输出端作为32-5线优先编码器的Z1输出端,3片的Y′0端接与非门的输入端,与非门的输出端作为32-5线优先编码器的Z0输出端,并把高位片74LS148(3)的S′接低电平,这样可构成32-5线优先编码器,图4为4片74LS148构成的32-5线优先编码器。

图4 用4片74LS148构成32线-5线优先编码器

在图4的逻辑电路中,该电路将输入的低电平信号A′0-A′31编成00000-11111,其中A′0逻辑的优先级别最低,A′31的优先级别最高,所以该电路能实现32-5线优先编码器的逻辑功能,其工作原理分析与24-5线译码器工作原理分析类似。

5、结论

以上对4片及其以下74LS148级联作了介绍和分析,对于其他更多片74LS148的级联可依次类推进行设计和分析,可以看出,不同的74LS148进行级联时,可以有多个输入信号请求编码,但编码器只对优先级别最高的进行编码,只有优先级别高的输入端为无效信号时,才对优先级别低的信号进行编码。

-

基于8051的Proteus仿真-74LS148扩展中断2016-09-06 710

-

protens仿真74ls148零管脚触发问题2012-05-05 0

-

proteus中74LS148的问题2013-01-24 0

-

请问利用多片74ls148八-三编码器怎么完成88路数据输入的编码2019-03-11 0

-

编码器和译码器(数电实验报告)精选资料分享2021-07-30 0

-

74ls148中文资料pdf下载2008-03-06 1857

-

74LS148中文资料pdf2008-03-19 3174

-

74ls148工作原理2017-11-07 30261

-

74ls148做八路抢答器2017-11-07 49074

-

优先编码器74ls148引脚图及功能介绍(工作原理,逻辑图及应用电路)2017-12-05 543766

-

用74LS148芯片实现32线-5线优先编码器2018-02-01 62399

-

74ls148可以用什么代替2018-02-01 7793

-

74ls147和74ls148有什么区别2018-05-07 32457

-

74ls148应用电路图大全(优先编码器\抢答器)2018-05-07 37956

-

74LS148优先编码器的数据手册免费下载2020-12-17 2424

全部0条评论

快来发表一下你的评论吧 !