74ls160设计数字秒表方案汇总(二款基于74ls160的数字秒表设计方案)

应用电子电路

描述

74ls160设计数字秒表方案汇总(一)

现场可编程门阵列(简称 FPGA)是20 世纪 80 年代中期出现的高密度可编程逻辑器件,采用SRAM开关元件的 FPGA 是易失性的,每次重新加电,FPGA 都要重新装入配置数据。突出优点是可反复编程,系统上电时,给 FPGA 加载不同的配置数据,即可令其完成不同的硬件功能。这种配置的改变甚至可以在系统的运行中进行,实现系统功能的动态重构。

“在系统可编程”(简称 ISP)是指对器件、电路或整个电子系统的逻辑功能可随时进行修改或重构的能力,支持 ISP 技术的可编程逻辑器件称为在系统可编程逻辑器件,它不需要专门的编程器,利用计算机接口和一根下载电缆就可以对器件编程了。

1、总体结构

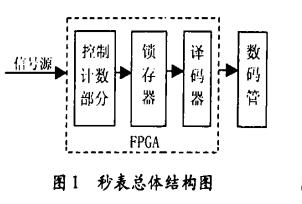

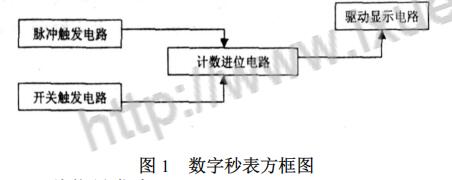

本文利用 EDA 技术中的 Max + plus Ⅱ作为开发工具,设计了一款基于 FPGA 的数字式秒表 ,并下载到在系统可编程实验板的 EPF10K10LC84 - 4 器件中测试实现。其总体结构框架如图1 所示。图中的信号源是由实验板上的时钟信号经分频而得到的 0. 1 秒信号;控制计数部分由一个计数模块 ctrl 构成,用来实现计时功能,锁存器模块 latch 用来对数据进行锁存 ;而译码器模块 DISP 用来对计数结果进行扫描译码;数码管用来显示秒表的工作结果。

2、电路设计

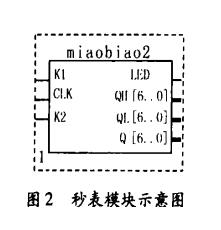

图2为数字式秒表的模块示意图。输入信号有三个,分别是 K1 , K2 和 CLK;输出信号有四个,分别是 LED ,QH[ 6. 。 0 ] ,QL[6. 。 0 ] 及 Q[ 6. 。 0 ]。其中 K1 为“开始/ 清零键”,接的是控制计数部分的整体清零端,该清零信号低电平有效。要求按下 K1 时计时开始 ,再按一下,停止计时,恢复到零状态。K2 为“固定显示键”,接的是锁存器 74373 的允许锁存端 G,该信号是高电平有效。在计时过程中,按下 K2 时,锁存数据 ,显示固定 ,但计时仍继续 ;按第二下时 ,显示从新时间开始。CLK 为时钟信号 ,必须是秒表计时所需的最小单位 0. 1S。

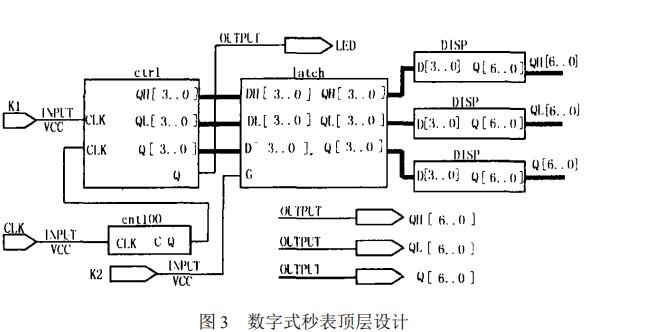

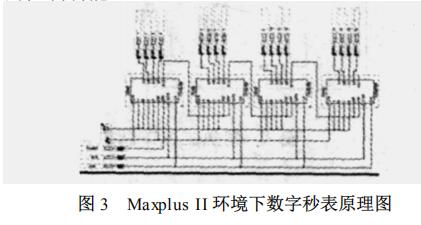

QH[6. 。 0 ] ,QL[6. 。 0 ] 及 Q[6. 。 0 ] 接三个数码管,分别表示秒十位,秒个位和秒十分位。LED 接发光二极管用来表示秒表的分位,当秒表计时超过59. 9 秒时 LED 灯亮,且能持续表示到 1分 59. 9 秒,然后灯灭,同时数码管重新计时显示,即该数字式秒表的计时范围从0 到2 分钟。基于原理图编辑和VHDL语言,并使用从上到下的设计方法设计的秒表,其具体的线路构成如图3 所示。

在总体电路图中,根据设计要求,输入信号 K1、K2 应采用脉冲开关。由于实验板上除了拨动开关就是瞬时的按键开关,且按键开关平时都呈高电平,按一下为低电平。故在实际测试时采用了拨动开关来模拟脉冲开关。根据设计要求将K1、K2 平时置于相应的高、低电平状态,需要清零或固定显示时再将它们分别置于相应的位置上即可。

3、模块设计

在设计电路时,要遵循从上到下的设计原则。首先从系统设计入手,在顶层进行功能划分和结构设计,顶层模块中的每个次层模块均可完成一个较为独立的功能,次模块在调试成功后可生成一个默认符号,以供上一层模块调用。

3. 1、时钟信号模块 cnt100

由于最终的设计结果要下载到可编程逻辑器件中测试,而承载该芯片的“在系统”可编程实验板上最小也是1 kHz 的时钟源,而秒表计时所需的最小单位为 0. 1s,故采用 2 片 74160,利用并行输入方式,接成 100 进制计数器(00~99),将 1 kHz 信号变成 10 Hz (即 0. 1 s),从而达到分频的目的。编译通过后创建的默认符号为 cnt100,其输入信号为 CLK,输出信号为 CQ(即高位的进位端 RCO) 。

3. 2、控制计时模块 ctrl

从 Maxplus2 器件库中调用 3 片 74160,采用串行时钟方式,连接成六百进制计数器(即 0~599),用来表示秒位。将 3 片 74160 的清零端 CLR 连接在一起,用来做秒表的整体清零端。再调用器件库中的 J K触发器,连接相应控制端形成 T′触发器,将六百进制计数器的进位信号接 T′触发器的时钟端。平时其输出端 Q 保持低电平,所接发光二极管不亮 ;当计时到 59. 9 秒时,由于有进位信号到来,因此时钟端出现脉冲下降沿,触发器翻转,Q 由低电平变为高电平,发光二极管点亮,表示已计时到 1 分钟。再计到 1分 59. 9 秒时,过 1 秒,灯灭,同时数码管重新计时显示。该控制模块为图 3 中 ctrl 模块。

3. 3、锁存器模块 latch

因为秒表设计中要求在计时过程中能随时固定显示时间,而计时仍然继续,所以要用到锁存器。在本例中适宜采用 CD4511 芯片,因为它集合了锁存、译码和驱动功能。但由于 Maxplus2 器件库中没有此类芯片,故以锁存器 74373 外加译码器 7447 (DISP) 代替。在设计时从器件库中调用 2 片 74373 (8 位锁存器), 将它们的 OEN 统统接低电平,允许数据输出。G端接一起,作为允许数据锁存端 (高电平有效) 。锁存器部分编译通过后创建的默认符号见图 3 中的 latch 模块,输入信号有四个,分别是 DH[ 3. 。 0 ] 、DL[3. 。 0 ] 、D[3. 。 0 ] 及 G,输出有三个,分别是 QH[3. 。 0 ] 、QL[3. 。 0 ]及 Q[3. 。 0 ] 。

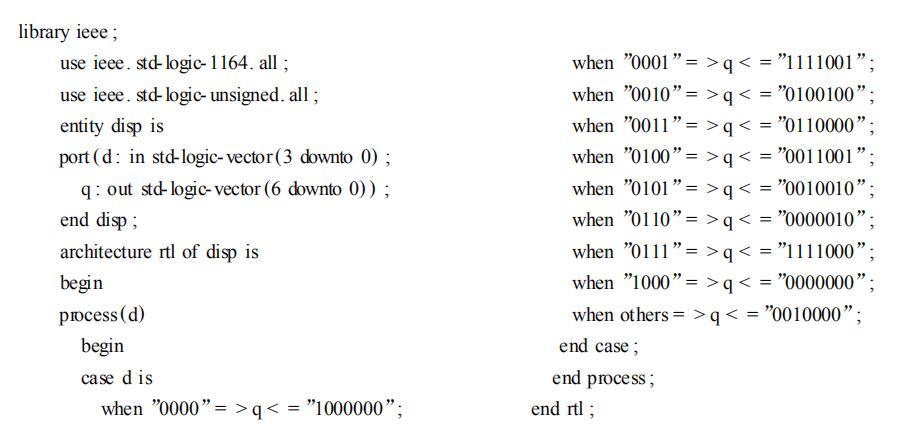

3. 4、译码显示模块 DISP

译码器可直接从器件库中调用 7447 (共阳极译码器),将它的控制端按要求接好,形成默认符号 ;也可用 VHDL 语言编程,将 4 位 BCD 码译成 7 段数码管的编码(0~9),现采用 VHDL 语言编程,编译无误后创建默认文件符号 DISP 以供上层电路调用。显示部分直接采用实验板上的 3 个共阳极数码管,不用将译码器的输出 a~g 具体连线到实验板上数码管的 7 个段,只需将其输出端口定义到可用作数码管显示的器件的 I/ O 引脚上即可。7 段数码管译码器源程序如下

4、编程及测试

为设计项目选定 FLEX10K系列中的 EPF10K10LC84 - 4 器件,锁定顶层设计中各端口所对应的引脚号,并编译通过。然后对器件编程,使用 ByteBlaste 下载电缆把项目以在线配置的方式下载到 ISP 实验板的 EPF10K10LC84 - 4 器件中,按相应的 K1、K2 键,观测数码管及发光二极管的状态,发现显示结果正确。该数字式秒表具有清零功能,能够在计时过程中随时停止计时,恢复到初始状态。且具有锁存/ 计时功能,能在计时过程中通过按“固定显示键”,将显示固定住,而计时仍继续 ;再按下键,显示从新时间开始。实验证明该秒表工作正常,基本上已达到了预期的设计要求。

5、结束语

在Max + plus Ⅱ开发环境下,采用自顶向下的设计方法有利于在早期发现结构设计中的错误,避免不必要的重复设计。再结合基于 FPGA 的“在系统”可编程实验板,轻轻松松就能实现各种电子产品的设计,现场观察实验测试结果。大大缩短了产品的设计周期和调试周期,提高了设计的可靠性和成功率,充分体现了可编程逻辑器件在数字电路设计中的优越性。

74ls160设计数字秒表方案汇总(二)

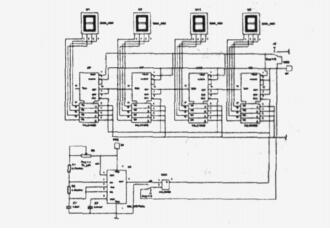

数字秒表是一种常用的计时工具,以其价格低廉、走时精确、使用方便、功能多而广泛应用于体育比赛中。下文介绍了如何利用中小规模集成电路和半导体器件进行数字秒表的设计。本设计中数字秒表的最大计时为 99. 99s,分辨率为 0. 01s,数码管显示,具有清零、启动计时、暂停及继续计时等功能。当计时停止时,秒表保持所计时间直至被清零复位。本设计由四个 74LS160 计数器实现计数功能,一个555 定时器产生 100 Hz 脉冲,四个数码显像管显示计时,再加两个控制开关,一个控制启动和暂停,另一个控制清零。

1、数字秒表的工作原理

电子秒表要求能够对时间进行精确记时并显示出来,因此要有时钟发生器,记数及译码显示,控制等模块,系统框图如下 :

1. 1 秒信号发生器

利用 555 定时器构成的多谐振荡器产生秒脉冲发生器。由于 555 定时器的比较器灵敏度高,输出驱动电流大,功能灵活,再加上电路结构简单,计算比较简单。利用 555 定时器构成的多谐振荡,在电路中我们选择数据如下 : C = 1 uF, R1 = R2 。利用公式 : f = 1/ ( R1 + 2 R2) Cl n2根据 设 计 要 求, 需 要 精 确 到 0. 01s, 故 f =100Hz,带入上式得 :R1 = R2 = 4. 8 KΩ。在 Multisim环境下的原理图中,取 R1 = R2 = 4. 7 KΩ,并且在 R1支路串联一个 1 KΩ的电位器,来调节脉冲信号的精度。此信号从 555 定时器的 3 引脚 OU T 端输出,送到计数器 74LS160 的脉冲输入端 CP,作为计时脉冲。

1. 2 计数进位部分

利用 74LS160 同步十进制加法计数器实现计数功能。这个计数器是十进制的,在设计时电路比较简单。而且可以实现清零功能, EP, ET,可以实现保持功能。可以很方便的实现清零,开始,暂停和继续这四个功能。具体电路原理如图 2 所示。

1. 3 译码及显示电路

将秒计时器 74LS160 的 4 个输出端 QD、QC、QB 和 QA 分别对应接至译码器 74LS48 的输入端,译码后的输出端接至共阴级 7 段数码管的 a~g 端,则显示器将进行 0~9 十进制数字显示。我们在Multisim 环境下绘制原 理 图 的 过 程 中, 选 用 将74LS48 和 7 段数码管合二为一的 DCD -HEX。

1. 4 控制电路

采用J1 和 J2 这样 2 个开关,实现相关的控制功能。J1 接高电平时,与非门 U4A 打开,时钟脉冲送入计数器进行计数显示 ;J1 接低电平时,与非门U4A 被封锁,计数器保持原来计数状态暂停计数。J2 接高电平时,计数器正常计数 ;J2 接低电平时,所有计数器清零,实现清零复位的功能。

2、Multisim 环境下的原理图与仿真

电路的四个 74LS160 计数器从右往左,分别为0. 01s,0. 1s,1s,10s 的计数器。同时四个计数器都为十进制。每个计数器均有四个接口接到后面的显示电路的 QD、QC、QB 和 QA。74LS160 具有自启动,避免电路进入死锁状态。显示电路由四个七段译码显示管组成,并由数字电子实验箱集成。整个电路由 555 定时器产生 100Hz 时钟信号,对电路进行时钟控制。逻辑开关由高低电平控制电路的开始暂停以及复位清零。当开关J1 处于高电平时,电路正常计数 ;转换为低电平时开始暂停保持 ;再次换为高电平继续计数。开关J2 处于高电平时,电路正常工作 ;处于低电平时,电路清零复位。Multisim 环境下数字秒表总电路原理图如图 2。

3、Maxplus II 环境下的原理图与仿真

图 3 为 Maxplus II 环境下的原理图。CL K 接100Hz 的时钟脉冲,为了方便观察结果,实验中设置的频率可高于 100Hz。CLR 是清零按钮。PAUSE是暂停继续按钮。74LS160 的输出端 QD、QC、QB和 QA 从 0000 到 1001 从图 2 可以看出在中水进水温度相同的条件下,热泵机组制热量随冷凝器出水温度的上升有所降低,而且蒸发器侧中水进水温度的上升时,制热量随之上升的比较明显。并从图中知,在蒸发器侧中水温度从 13 ℃上升到 15 ℃时,制热量的变化速度要小于从 15 ℃上升到 17 ℃的过程,说明蒸发器侧中水进水温度愈高对制热量越有帮助。

图 3 可知 :在蒸发器侧中水进水温度不变的情况下,随着冷凝器出水温度的上升,机组的输入功率呈明显上升的趋势,结合图 2 中表现的制热量下降的趋势,导致了图 4 中制热性能系数下降 ;在冷凝器出水温度不变时,随着蒸发器侧中水进水温度的上升,输入功率呈缓慢增大的趋势,机组的制热量也在增大,对应制热工况下的性能系数曲线可看出性能系数也在上升,但它的上升趋势比较平缓。说明制热量的变化趋势要快于输入功率的变化趋势,热泵机组能够以较高的性能运行。

图 4 为 Maxplus II 环境下仿真结果。仿真结果表明,所设计 99. 99 数字秒表电路可正常工作。编程下载后, 将 CL K 接固定频率的信号, CLR 和PAUSE 分别接两个开关。将 74LS160 的输出端QD、QC、QB 和 QA 分别接不同的发光二极管以显示各个计数状态,或通过显示译码器接数码显示。显示结果验证了所设计电路能够正常计数。通过CLR 和 PAUSE 开关对电路工作状态进行控制实验,测试结果表明所设计控制单元电路能实现相关的控制功能。

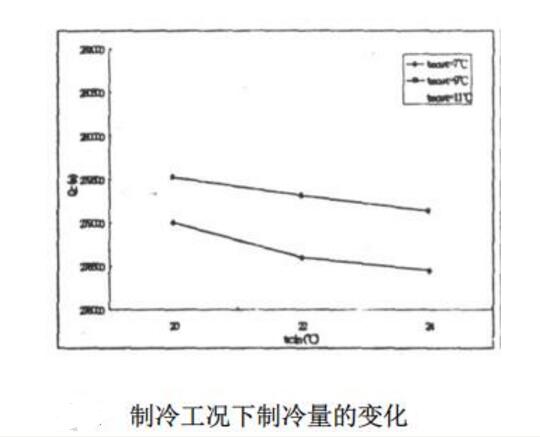

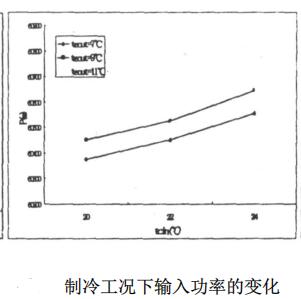

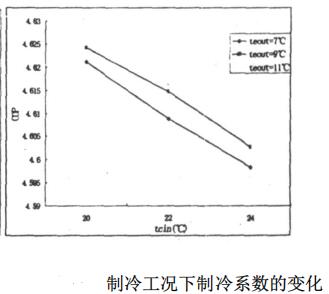

3. 2、制冷工况下 :保证中水源热泵机组冷凝器侧进

水温度相同进行测试。图 5、6、7 分别为制冷工况下制冷量、输入功率和制冷性能系数的变化曲线。由图 5 可以看出,在冷凝器进水温度相同条件下,制冷量随蒸发器出水温度的上升而增大 ;在蒸发器出水温度不变时,机组制冷量随冷凝器进水温度上升而减小趋势很明显。但机组的制冷量随冷凝器进水温度的变化的过程中,其变化趋势的大小是不同的,从图中可看出 20~22 ℃的变化趋势要比 22~24 ℃的趋势要快一些。可见 :中水温度的变化对热泵机组的制冷量产生十分重要的影响。由图 6、7 可以看出 :在蒸发器出水温度不变的情况下,随着冷凝器进水温度的上升,机组的输入功率上升,制冷性能系数下降 ;在冷凝器进水温度不变,蒸发器出水温度上升时,输入功率增大缓慢,增长幅度低于制冷量上升幅度,因此,制冷性能系数呈现逐渐增加的趋势。

4、结论

4. 1、对于供暖期较长的内蒙古地区来说,由于中水的温度高于同季节地表水、地下水的水温,中水更适合作为热泵机组的冷源。

4. 2、中水作为热泵的冷热源时,各种工况下热泵机组均能在较高的性能下运行,可以达到节能减排的目的。

4. 3、该实验研究为内蒙古地区中水源热泵的应用提供了有价值的数据。

- 相关推荐

- 74ls160

-

如何采用两种方法利用74LS160设计24进制计数器?2021-11-24 0

-

74LS160中文资料pdf2008-03-19 4324

-

74ls160引脚图管脚图及功能真值表2008-01-06 127131

-

74ls160系列电路2008-01-06 4328

-

74LS160构成的100进制同步加法计数器2009-03-30 23300

-

74LS160 VHDL程序2016-11-11 3011

-

74ls192和74ls160的区别有哪些2017-12-21 32235

-

74ls160设计60进制计数器2017-12-21 233196

-

74ls160十进制计数器2018-01-18 202708

-

74ls160构成24进制计数器2018-01-18 154292

-

74ls160数字钟仿真电路(振荡器\74LS47D\计数器\74LS48)2018-05-08 68260

-

74ls160和74ls161区别2018-05-08 117281

-

74ls160引脚图与真值表2021-06-04 88342

-

74ls160价格 74ls160十进制计数器简介2021-06-05 14219

-

74ls160引脚图及功能真值表介绍2022-05-25 129669

全部0条评论

快来发表一下你的评论吧 !