74hc165使用方法(74hc165功能_内部结构图_时序图)

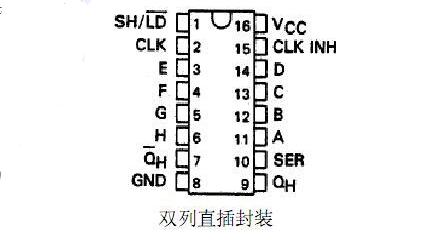

芯片引脚图

描述

74HC165概述

74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0→Q1→Q2,等等)。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。只有在CP为高时,才允许CE由低转高。在PL上升沿来临之前,不论是CP还是CE,都应当置高,以防止数据在PL的活动状态发生位移。

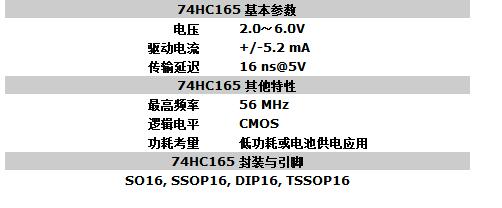

74HC165参数

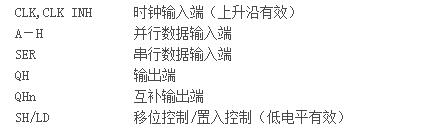

74hc165引脚及功能

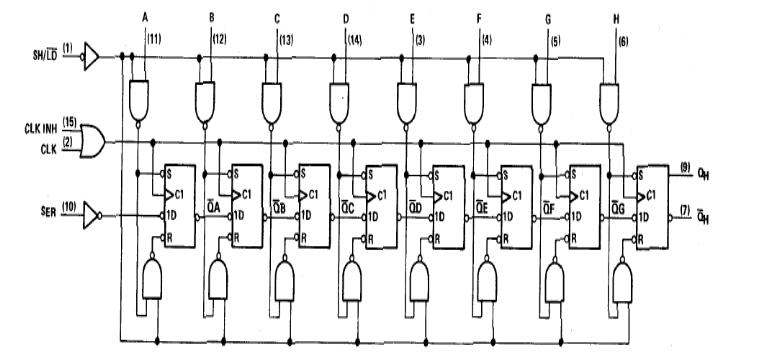

74hc165内部结构图

74hc165使用方法

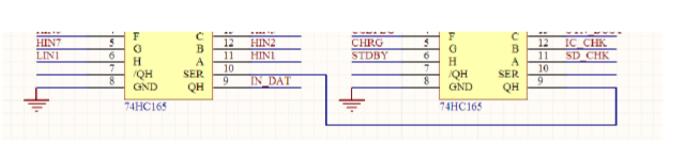

74HC165级联,如下图

SH/LD为低,并口数据存入8个位寄存器中。8个位寄存器分别为Q0、Q1、Q2、Q3、Q4、Q5、Q6、Q7。此时Q7里已经有值,可以直接读取了所以,逻辑可以是这样

读取Q7的数据,然后IN_CLK_LOW;IN_CLK_HIGH;制造一次上升沿,执行移位操作,使Q6的值移位到Q7中。SH/LD为高,允许移位。一个时钟脉冲,QH向外输出一位数据,同时,从SER采集一位数据补充8位寄存器。

如上级联情况,右边74HC165的SER悬空,采集数据为0.

左边74HC165,一个脉冲,QH输出一位数据,同时,从SER采集一位数据补充低位。相当于如下:开始前

H1-G1-F1-E1-D1-C1-B1-A1H2-G2-F2-E2-D2-C2-B2-A2开始传输

1,1G-1F-1E-1D-1C-1B-1A-2H2G-2F-2E-2D-2C-2B-2A-0

2,1F-1E-1D-1C-1B-1A-2H-2G2F-2E-2D-2C-2B-2A-0-0

3,1E-1D-1C-1B-1A-2H-2G-2F2E-2D-2C-2B-2A-0-0-0

。。。

14,B2-A2-0-0-0-0-0-00-0-0-0-0-0-0-0

15,A2-0-0-0-0-0-0-00-0-0-0-0-0-0-0

16,0-0-0-0-0-0-0-00-0-0-0-0-0-0-0

这样,就把2个级联的74HC165的并口数据,全部以串口形式传输给了MCU。

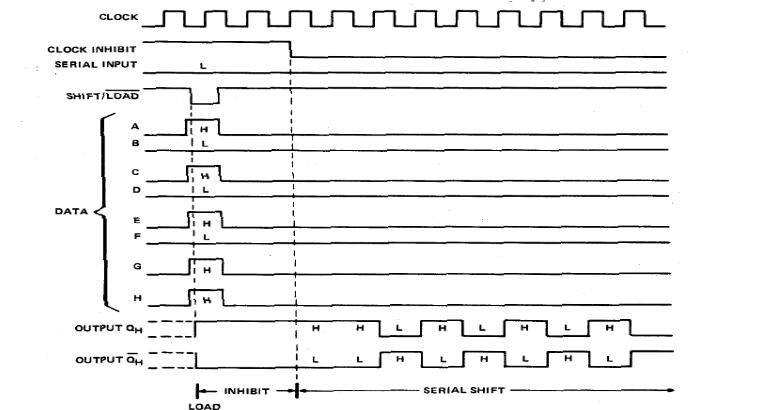

74hc165时序图

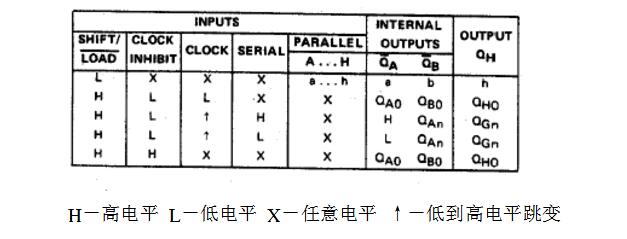

74hc165真值表

- 相关推荐

- 热点推荐

- 74HC165

-

请教一个74HC165问题2022-03-25 6490

-

LPC1114读取74HC165数据的方法2021-12-07 989

-

如何对74HC165的代码Proteus仿真2021-09-29 1873

-

74HC165编程篇2021-07-02 1336

-

用74HC165读8个按键状态2018-02-02 12615

-

74HC165功能说明资料下载2017-12-20 2399

-

74HC165英版数据手册2016-12-09 1336

-

74HC165英文手册2016-11-02 1082

-

74HC165读取按键键值的问题2016-03-15 15985

-

74HC1652015-06-15 6430

-

74hc165求助2014-06-28 3750

-

74hc165应用电路2008-09-22 8797

全部0条评论

快来发表一下你的评论吧 !