解析80C51单片机中的cpu、存储器配置以及并行输入/输出口

电子说

描述

单片机按存储结构可分为二类:一类是哈佛结构,另一类是普林斯顿结构。

①哈佛结构所谓哈佛结构是指程序存储器地址空间与数据存储器地址空间分开的单片机结构,如80C51单片机采用哈佛结构,所以80C51单片机的程序存储器地址空间与数据存储器地址空间是分开的,各有64K存储空间。

②普林斯顿结构所谓普林斯顿结构是指程序存储器地址空间与数据存储器地址空间合并的单片机结构,如MCS-96单片机采用普林斯顿结构,所以MCS-96单片机的程序存储器地址空间与数据存储器地址空间是合并的,共有64K存储空间。

1.单片机的CPU

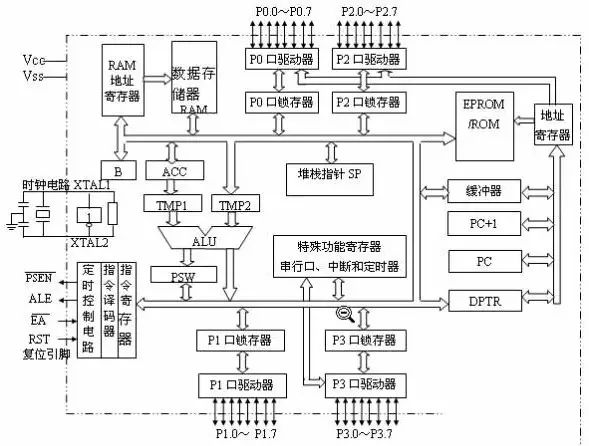

图1是80C51单片机的内部结构框图。若除去图中的存储器电路和I/O部件,剩下的便是CPU。它可以分为运算器和控制器两部分。运算器功能部件包括算术逻辑运算单元ALU、累加器ACC、寄存器B、暂存寄存器TMP1、TMP2、程序状态字寄存器PSW等。控制器功能部件包括程序计数器PC、指令寄存器IR、指令译码器ID、定时控制逻辑电路CU、数据指针寄存器DPTR、堆栈指针SP及时钟电路等。

(1)运算器

①算术逻辑运算单元ALU(Arithmetic Logical Unit)

ALU可以进行算术、逻辑运算。算术运算有:加、减、乘、除,逻辑运算有:与、或、异或等。

②累加器ACC

累加器ACC的主要功能是在运算前存放一个操作数,运算后存放一个操作结果。80C51系列单片机虽然在结构上仍然以累加器A作为重要部件。但由于内部电路采取了措施,使得累加器A在数据传送、逻辑操作等方面的核心作用有所削弱。数据可以在片内直接/间接地址的存储器之间直接传送,而不必经过累加器A。但,加、减、乘、除算术运算指令的运算结果都存放在累加器A或AB寄存器对中。

③暂存器TMP1、TMP2由图1可知,ALU进行算术逻辑运算前的两个操作数来自暂存器TMP1、TMP2,所以暂存器TMP1、TMP2用于存放运算前的两个操作数。

④程序状态字寄存器PSW程序状态字寄存器PSW用来存放运算结果的状态标志。PSW寄存器各位的含义如下,其中PSW.1未定义,其它各位说明如下:

| CY | AC | F0 | RS1 | RS0 | OV | / | P |

CY:进位标志。它是累加器A的进位位,如果操作结果在最高位有进位(加法)或借位(减法)时置1,否则清0。

AC:半进位标志。它是低半字节的进位位(累加器A中A3位向A4位的进位),主要用于BCD码调整。低4位有进位(加法时)或向高4位有借位时(减法时),AC是1,否则,AC清0。

F0:用户定义的状态标志位。可通过软件对它置位、复位或测试,以控制程序的流向。

RS1、RS0:工作寄存器区选择控制位,用于选择4组工作寄存器之一。可以用软件来置位或清零,以确定工作寄存器区。RS1、RS0与寄存器区的对应关系如下:

RS1、RS0=00——0区(地址00H~07H)RS1、RS0=01——1区(地址08H~0FH)RS1、RS0=10——2区(地址10H~17H) RS1、RS0=11——3区(地址18H~1FH)

OV:溢出标志位,用于表示有符号数算术运算的溢出。溢出时OV为1,否则OV为0。

P:奇偶标志位。每个指令周期都由硬件来置位或清零,以表示累加器A中1的个数的奇偶性。若1的个数为奇数,则P置位;若1的个数为偶数,则清零。

⑤寄存器B

在乘除指令中,用到了寄存器B。

(2)控制器

控制器是控制单片机各种操作的部件,用于完成指令规定的操作。它包括程序计数器PC、指令寄存器IR、指令译码器ID、定时控制逻辑、数据指针寄存器DPTR、时钟发生器、复位电路、堆栈指针SP等。

①程序计数器 PC

程序计数器PC为16位寄存器,用于存放下一条要执行指令地址,具有自动加1功能。

②指令寄存器IR、指令译码器ID、定时控制逻辑电路

指令寄存器IR用来暂时存放当前取出的指令,并由指令译码器ID译码,产生相应的译码信号,并传送给定时控制电路,定时控制电路发出各种控制信号控制各器件完成指令规定的操作。

③数据指针DPTR

DPTR为16位寄存器。由于80C51单片机采用哈佛结构,因此,其程序存储器与地址存储器是分开的,程序存储器的地址是由程序计数器PC提供,而数据存储器的地址是由数据指针DPTR提供的,所以DPTR用于存放片外数据存储器及I/O口的地址。

④时钟电路

时钟电路是计算机的心脏,它控制着计算机的工作节奏。

⑤复位和复位电路

计算机在启动运行时都需要复位,复位就是使CPU和系统中的其它部件处于一个确定的初始状态,并从这个状态开始工作。

⑥堆栈指针SP

堆栈指针SP用于存放栈顶单元的地址。

2.单片机的存储器配置

由于80C51单片机采用哈佛结构,所以其程序存储器和数据存储器是分开的,各有自身的寻址系统、控制信号和功能。程序存储器用来存放程序和表格常数;数据存储器通常用来存放程序运行所需要的给定参数和运行结果。

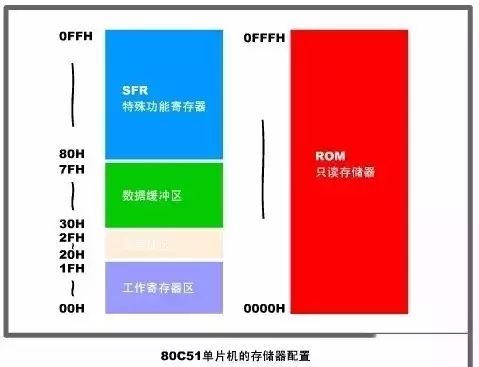

从实际的物理存储介质来看,80C51有4种存储空间,它们是片内程序存储器、片外程序存储器、片内数据存储器(含特殊功能寄存器)和片外数据存储器。80C51的存储器配置情况如图2所示。

逻辑地址空间来看,80C51单片机可分为三部分,即:程序存储器、片外数据存储器、片内数据存储器。这3部分分别使用不同的地址指针,不同的访问指令。因此,下面按逻辑结构介绍80C51的存储器结构。

(1)程序存储器

由图3可知,程序存储器以程序计数器PC作地址指针,通过16位地址总线,可寻址的地址空间为0000H~0FFFFH共64K(216=64K)字节,其访问指令为MOVC。用于存放程序指令码与固定的数据表格等。

80C51单片机中内部和外部共64K字节程序存储器的地址空间是统一的。对于有内部ROM的单片机,在正常运行时,应把引脚接高电平,使程序从内部ROM开始执行。当PC值超出内部ROM的容量时,会自动转向外部程序存储器空间。

(2)片外数据存储器

由图可知,片外数据存储器以DPTR作为地址指针,通过16位地址总线,可寻址的地址空间为0000H~0FFFFH共64K(216=64K)字节,其访问指令为MOVX。用于存放数据与运算结果。

(3)片内据存储器

片内数据存储器的地址空间从00H~FFH共256字节,其访问指令为MOV。其地址可由R0、R1寄存器提供。内部数据存储器是最灵活的地址空间,它分成物理上独立且性质上不同的2个区:00H~7FH单元组成的128字节RAM区,地址为80H~FFH的特殊功能寄存器区(简称SFR区)。

1)RAM区(00H~7FH)

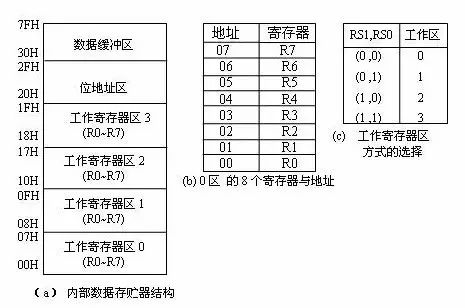

由图2-3可知,RAM区又分为3个区:工作寄存器区、位地址区与数据缓冲区。

①工作寄存器区(00H~1FH)

80C51单片机的内部RAM区结构如图2-3所示。

②位地址区(20H~2FH)

内部RAM的20H~2FH为位寻址区域,见表1所示。这16个单元的每一位都有一个位地址,位地址范围为00H~7FH。通常把各种程序状态标志、位控制变量设在位寻址区内。位寻址区的RAM单元也可以作为一般的数据缓冲区使用。

表1 内部RAM区的位地址映像表

③数据缓冲区

数据缓冲区的地址空间从30H~7FH共80个字节单元,用于存放数据与运算结果,如加法运算时,存放加数、被加数及运算和。通常堆栈区也设置在该区内。有些单片机将显示缓冲区设置在该区内。

2)特殊功能寄存器SFR(80H~FFH)

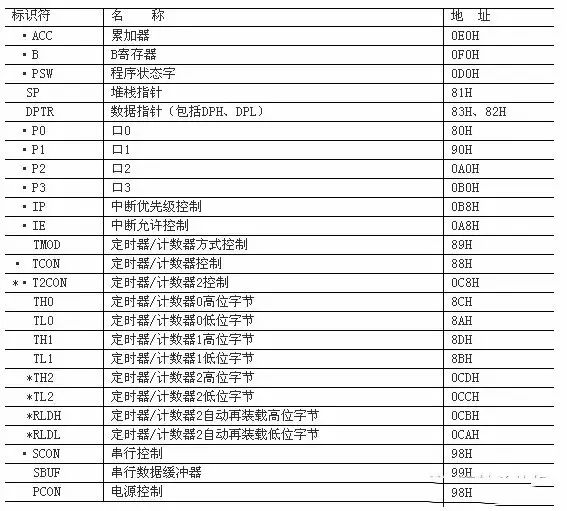

80C51单片机内的I/O口锁存器、状态标志寄存器、定时器、串行口、数据缓冲器以及各种控制寄存器统称为特殊功能寄存器,它们离散地分布在内部RAM地址空间(80H~0FFH)内,表2列出了这些特殊功能寄存器的标识符、名称及地址。由表2-2可知累加器ACC、寄存器B、程序状态字PSW、I/O口P0~P3等均为特殊功能寄存器。

表2 特殊功能寄存器SFR

注:带“·”号的寄存器可按字节和按位寻址,其特征是直接地址能被8整除。带“*”号的寄存器是与定时器/计数器2有关的寄存器,仅在80C52系列中存在。下面以一个实例说明单片机的内部存储器。

3.80C51单片机并行输入/输出口

80C51单片机含有4 个8位并行I/O口P0、P1、P2和P3。每个口有8个引脚,如图2-1所示,共有32个I/O引脚,每一个并行I/O口都能用作输入或输出。各口的第一、第二功能如下:

I/O口 引脚 第一功能 第二功能P0口 P0.0~P0.7 输入与输出 分时的传送地址低8位与数据线P1口 P1.0~P0.7 输入与输出 无第二功能P2口 P2.0~P2.7 输入与输出 传送地址的高8位P3口 P3.0~P3.7 输入与输出 P3.0——RXD:串行口输入端

P3.1——TXD:串行口输出端P3.2——INT0:外部中断0中断请求输入端P3.3——INT1:外部中断1中断请求输入端P3.4——T0:定时器/计数器0外部输入端P3.5——T1:定时器/计数器1外部输入端P3.6——WR:外部数据存储器写选通信号

P3.7——RD:外部数据存储器读选通信号

四个通道口都有一种特殊的线路结构,每个口都包含一个锁存器,即特殊功能寄存器P0~P3,一个输出驱动器和两个(P3口有三个)三态缓冲器。这种结构在数据输出时,可以锁存,即在重新输出新的数据之前,口上的数据一直保持不变。但对于输入信号是不锁存的,所以外设欲输入的数据必须保持到取数指令执行(把数据读取后)为止。

下面分别叙述各个端口的结构、功能和使用方法。

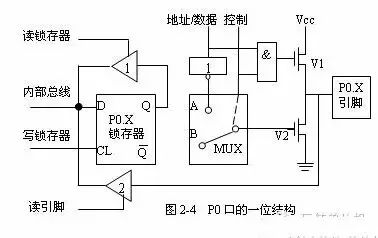

(1)P0口的组成与功能 1)位结构

在访问外部存储器时,P0口是一个真正的双向数据总线口,并分时送出地址的低8位。图2-4所示的是P0口的一位结构图。它包含两个输入缓冲器、一个输出锁存器以及输出驱动电路、输出控制电路。输出驱动电路由两只场效应管V1和V2组成,其工作状态受输出控制电路的控制。输出控制电路包括与门、反相器和多路模拟开关MUX。P0口既能用作通用I/O口,又能用作地址/数据总线。

2)作为通用I/O口P0口作为通用I/O口使用时,CPU令控制信号为低电平。这时多路开关MUX接通B端即输出锁存器的 端,同时使与门输出低电平,场效应管V1截止,因而输出级为开漏输出电路。

①作为输出口当用P0口输出数据时,写信号加在锁存器的时钟端CL上,此时与内部总线相连的D端其数据经反相后出现的 端上,再经V2管反相,于是在P0口引脚上出现的数据正好是内部总线上的数据。由于输出级为开漏电路,所以用作输出口时应外接上拉电阻。

②作为输入口当P0口用于输入数据时,要使用端口中的两个三态输入缓冲器之一。这时有两种工作方式:读引脚和读锁存器。

当CPU执行一般的端口输入指令时,“读引脚”信号使图2-4中下面一个缓冲器开通,于是端口引脚上的数据经过缓冲器输入到内部总线上。

当CPU执行“读一修改一写”一类指令时,“读锁存器”信号使图2-4上面一个缓冲器开通,锁存器Q端的数据经缓冲器输入内部数据总线。

在P0口作为输入口使用时,必须首先向端口锁存器写入“1”。这是因为当进行读引脚操作时,如果V2是导通的,那么不论引脚上的输入状态如何,都会变为低电平。为了正确读入引脚上的逻辑电平,先要向锁存器写1,使其 端为0,V2截止。该引脚成为高阻抗的输入端。

3)作为地址/数据总线P0口还能作为地址总线低8位或数据总线,供系统扩展时使用。这时控制信号为高电平,多路开关MUX接通A端。有两种工作情况:一种是总线输出,另一种是外部数据输入。作为总线输出时,从“地址/数据”端输入的地址或数据信号通过与门驱动V2,同时通过非门驱动V2,结果在引脚上得到地址或数据输出信号。

作为数据总线输入数据时,从引脚上输入的外部数据经过读引脚缓冲器进入内部数据总线。对于80C51、87C51单片机,P0口能作为I/O口或地址/数据总线使用。对于80C31单片机,P0口只能用作地址/数据总线。

综上所述,P0口既可以作为地址/数据总线口,这时它是真正的双向口,也可作通用的I/O口,但只是一个准双向口。准双向口的特点是:复位时,口锁存器均置“1”,8根引脚可当一般输入线使用,而在某引脚由原输出状态变成输入状态时,则应先写入“1”,以免错读引脚上的信息。一般情况下,P0口已当作地址/数据总线口使用时,就不能再作通用I/O口使用。

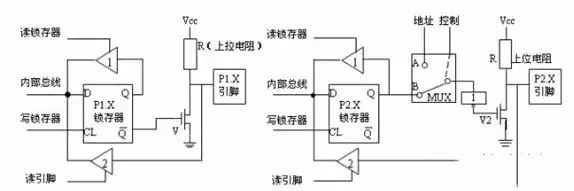

(2)P1口组成与功能

P1口只用作通用I/O口,其一位结构图如图所示。与P0口相比,P1口的位结构图中少了地址/数据的传送电路和多路开关,上面一只MOS管改为上拉电阻。

P1口作为一般I/O的功能和使用方法与P0口相似。当输入数据时,应先向端口写“1”。它也有读引脚和读锁存器两种方式。所不同的是当输出数据时,由于内部有了上拉电阻,所以不需要再外接上拉电阻。

(3)P2口的组成与功能

当系统中接有外部存储器时,P2口可用于输出高8位地址,若当作通用I/O口用,P2口则是一个准双向口。因此说P2口能用作通用I/O口或地址总线,其一位的结构如图所示。

①作为通用I/O口

当控制信号为低电平时,多路开关接到B端,P2口作为通用I/O口使用,其功能和使用方法与P1口相同。

②作为地址总线当控制端输出高电平时,多路开关接到A端,地址信号经反相器、V从引脚输出。这时P2口输出地址总线高8位,供系统扩展使用。

对80C51、87C51单片机,P2口能作为I/O口或地址总线作用。对于80C31单片机,P2口只能用作地址总线。

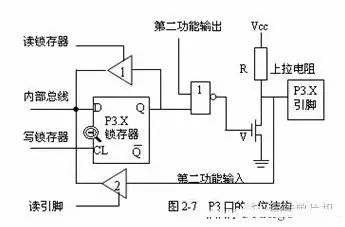

(4)P3口组成与功能

P3口能作通用I/O口,同时每一引脚还有第二功能。P3口的一位结构如图2-7所示。

作为通用I/O口:当“第二功能输出”端为高电平时,P3口用作通用I/O口。这时与非门对于输入端Q来说相当于非门,位结构与P2口完全相同,因此P3口用作通用I/O口时的功能和使用方法与P2口、P1口相同。

用作第二功能: 当P3口的某一位作为第二功能输出使用时,应将该位的锁存器置“1”,使与非门的输出状态只受“第二功能输出”端的控制。“第二功能输出”端的状态经与非门和驱动管V输出到该位引脚上。

当P3口的某一位作为第二功能输入使用时,该位的锁存器和“第二功能输出”端都应为“1”,这样,该位引脚上的输入信号经缓冲器送入“第二功能输入”端。

至此,可以对组成一般单片机应用系统时各个并行口的分工小结如下:P0口:分时的用作地址低8位与数据线,低8位地址由PC低8位或DPL提供。P1口:按位可编址的输入输出口。P2口:地址线的高8位,高8位地址由PC高8位或DPH提供。P3口:双功能口,若不用第二功能,可作为一般的I/O口。

-

#硬声创作季 单片机原理及应用:80C51的存储器组织Mr_haohao 2022-10-31

-

单片机原理及应用:80C51的存储器组织#单片机学习硬声知识 2022-11-07

-

80C51单片机的内部结构2017-03-25 0

-

基于80c51单片机2017-05-11 0

-

单片机原理及应用2017-08-26 0

-

80c51单片机最小系统原理图2021-07-19 0

-

80c51内核在单片机中的应用2021-07-29 0

-

80C51单片机的硬件结构知识点汇总2021-11-19 0

-

80C51存储器数据传输实验2021-12-01 0

-

80C51系列单片机硬件基础相关资料推荐2021-12-01 0

-

掌握80C51单片机矩阵键盘的构成原理和软件编程2021-12-06 0

-

80C51单片机中存储器是RAM和ROM分开编址的吗?2023-05-09 0

-

80C51单片机的硬件结构是怎么样的?2018-09-20 1156

-

80C51单片机复习资料(一)2021-11-22 452

-

80C51单片机片内与片外程序存储器的选择2022-10-18 4009

全部0条评论

快来发表一下你的评论吧 !