嵌入式SoC芯片S698-T的飞参采集器设计

嵌入式操作系统

描述

随着我国航空业的发展,我国自主设计的飞机越来越多的飞行在天空中,为了记录监控飞机飞行过程中,飞机各种设备的参数,就需要飞行参数记录仪器进行实时记录。而飞机上设备种类、接口类型、信号种类都比较多,而为了满足多种飞机型号的需求,就需要将飞行参数采集器设备的尺寸做的比较小,使得大飞机和小飞机都能够使用。

为了满足上述要求,最好的使用方式,就是采用一款具有多种功能模块的芯片来进行开发设计,这样可以避免采用多款单独的功能芯片设计造成设备尺寸过大,系统协调性较差的情况。S698-T芯片是珠海欧比特控制工程股份有限公司自主研发设计的以SPARC V8(IEEE-1754)架构为标准的32位RISC整数单元IΜ为主控内核,配以IEEE-754标准的64位双精度浮点处理单元FPΜ。采用130 nmCMOS工艺制造及使用BGA352封装形式的高性能、高可靠性、高集成度的嵌入式SoC芯片。S698-T内部还集成了1553B总线控制器、ARINC429总线控制器、CAN总线控制器、多功能IO接口、ΜART接口、在线硬件调试支持单位DSΜ、DAC模块、ADC模块等多种功能模块。

1 飞参采集器硬件设计

飞参采集器的主要功能:完成输入通道参数的高精度采集工作,并按一定的格式输出到记录器;通过以太网接口连接上位机可完成参数配置、履历设置、数据校准、数据卸载等功能;采集器内部带有实时时钟,采集结果数据带有时钟信息;具有8路高速采样通道,这8个通道在调试模式下,可作为虚拟示波器使用,在采集模式下,可对信号正常采集;通过CAN总线可级联设备扩展采集通道;产品支持上电自检、周期自检和维护自检,并能够记录并报告自检测信息,方便定位故障;产品考虑EMI、EMC设计,提高产品的抗电磁干扰能力。

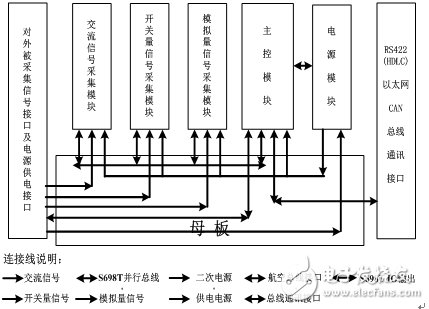

采集器采用模块化设计,其总体框图如图1所示。采集器由六部分组成:电源模块、主控模块、开关量信号采集模块、模拟量信号采集模块、交流信号采集模块、母板。

图1 产品整机组成框图

其中电源模块主要实现DC-DC电源转换,为产品中其他功能模块提供稳定的电源。

主控模块集成了系统控制器、航空总线接口(包括1553B总线接口、ARINC429总线接口、CAN总线接口、RS422接口、RS232总线接口、以太网总线接口)以及板载缓存等模块。

开关量信号采集模块主要完成90路开关信号的采集。

模拟量信号采集模块主要完成5路耗油信号、5路0~100 mV模拟信号、5路-10~10V直流差分信号、30路±35 V直流信号、10路±200 V直流信号、8路高速采样功能、8路频率信号和10路电流比计信号的采集。

交流信号采集模块主要是完成6路36~380 V交流模拟信号以及6路三相交流同步器信号的采集。

采集器采用模块化设计,除电源模块之外,主控模块直接通过并行总线控制其他三个功能模块,所有参数配置,采集结果数据帧组合都是在主控板完成,主控板提供以太网接口用于与上位机通讯,进行参数配置、分析检查采集时的数据导出以及高速采集通道的数据上传,同时提供RS422接口,用于将采集结果数据传送到记录器。

母板主要用于实现对外接口和各个功能模块之间的连接以及功能模块之间的互连。

2 FPGA设计实现

采集器中有4个功能模块涉及到FPGA设计。

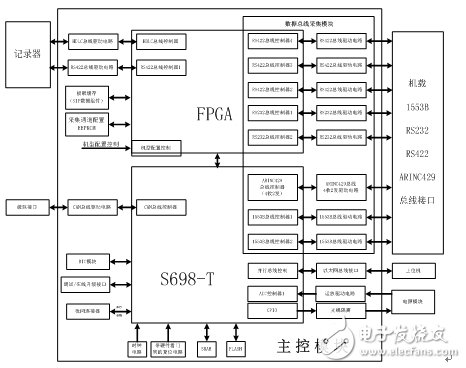

主控模块功能框图如图2所示:

图2 主控模块功能框图

主控模块的FPGA主要实现以下功能模块:

² 1路HDLC总线接口控制器,要求发送FIFO为1024 Byte,接收FIFO为64 Byte;

² 2路RS232总线控制器,要求发送FIFO为64 Byte,接收FIFO为1024 Byte;

² 4路RS422总线控制器,要求发送FIFO为64 Byte,接收FIFO为1024 Byte。

FPGA与S698T之间通过并行总线(地址、数据以及控制信号)进行通讯,FPGA内部需要具备并行总线控制接口;

² 16路GPIO接口;

² 板载缓存FLASH JKFC2G08VS48MM控制接口;

² 通道配置信息存储器EEPROM AT24C16A控制接口;

² RTC时钟芯片接口;

² 1路FPGA自身心跳脉冲输出。

该FPGA上电工作流程为:上电-》读取通道配置信息存储器EEPROM-》根据配置信息(各总线接口的参数包括波特率、奇偶校验等)设置各个总线接口的参数,并使能总线接口处于接收状态-》等待S698T把接收在缓存的数据读走;

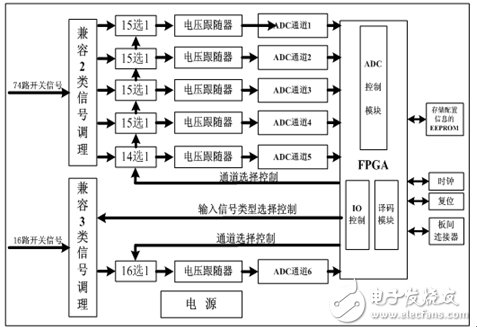

开关量信号采集模块功能框图如图3所示。

图3 开关量信号采集模块功能框图

开关量信号采集模块的FPGA主要实现以下功能模块:

² ADC芯片ADS8555SPM 接口,该接口需要缓存空间,用于缓存ADC的采集结果;

² 通道选择开关MAX354接口;

² 16路GPIO(用于控制采集通道输入范围的电阻选择);

² 通道配置信息存储器EEPROM AT24C16A控制接口;

² 1路FPGA自身心跳脉冲输出;

² 开关量信号采集的各种滤波算法;

该FPGA上电工作流程为:上电-》读取通道配置信息存储器EEPROM-》根据配置信息(通道是否使能、通道输入范围(根据范围决定该通道是否加上拉电阻))设置通道的硬件-》开始每0.1 μs轮询一个通道的采集结果并缓存起来-》等待S698T把缓存的数据读走;

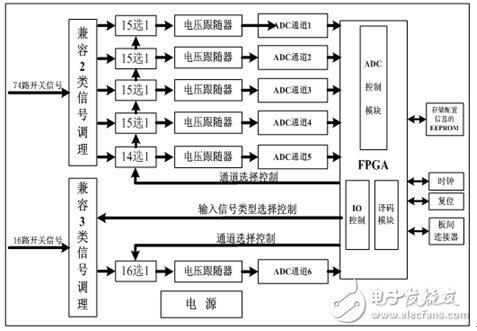

模拟信号采集模块功能框图如图4所示。

图4 模拟信号采集模块功能框图

模拟信号采集模块的FPGA主要实现以下功能模块:

² ADC芯片ADS8555SPM 接口,该接口需要缓存空间,用于缓存ADC的采集结果;

² 通道选择开关MAX354接口;

² 电流比测试量程控制开关MAX335MRG接口;

² 测频控制模块,支持8通道输入(8选1输入);

² 通道配置信息存储器EEPROM AT24C16A控制接口;

² 1路FPGA自身心跳脉冲输出;

² 模拟量采集的滤波算法;

由于采集通道的数据采集完全由FPGA控制完成(包括采集流程),所以该FPGA上电工作流程为:上电-》读取通道配置信息存储器EEPROM-》根据配置信息(通道是否使能、通道输入范围)设置通道的硬件-》开始每0.1 μs轮询一个通道的采集结果并缓存起来-》等待S698T把缓存的数据读走;

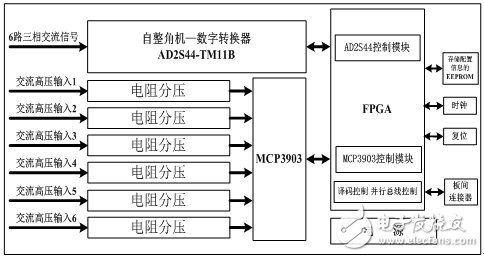

交流信号采集模块结构框图如图5所示,主要完成以下功能:

图5 交流信号采集模块功能框图

² 自整角机—数据转换器芯片AD2S44接口,该接口需要缓存空间,用于缓存ADC的采集结果;

² 交流信号采集芯片MCP3903接口;

² 通道配置信息存储器EEPROM AT24C16A控制接口;

² 1路FPGA自身心跳脉冲输出;

² 交流信号采集的滤波算法;

该FPGA上电工作流程初定为:上电-》读取通道配置信息存储器EEPROM-》根据配置信息(通道是否使能等)设置通道的硬件-》开始每0.1 μs轮询一个通道的采集结果并缓存起来-》等待S698T把缓存的数据读走;

3 结论

通过板级调试及实验表明:基于S698-T的飞参采集器设计完全满足实际应用需求,目前该型飞参采集器已大量使用在实际产品中。

-

SOC嵌入式相关资料推荐2021-11-01 0

-

S698存贮器接口电路及其应用2009-08-20 0

-

飞思卡尔开发工具,嵌入式学习2013-04-01 0

-

【Banana Pi M1+申请】嵌入式多通道数据采集器2016-06-20 0

-

如何实现嵌入式ASIC和SoC的存储器设计?2019-08-02 0

-

嵌入式电能计量及查询系统有什么功能?2019-09-26 0

-

嵌入式系统的硬件平台组成2020-06-20 0

-

嵌入式设备的性能soc2021-12-20 0

-

SoC芯片-S698-MIL™-专门用于恶劣环境2008-05-19 1159

-

高性能的32位RISC嵌入式并行微处理器-S698P-SOC2008-05-19 1162

-

基于嵌入式处理器S698-T芯片实现机器人移动平台电控系统的设计2021-04-13 3295

-

S698-T芯片开发系统S698T-Dkit使用说明书2022-05-10 318

-

S698-T立体封装计算机模块用户手册2022-06-08 245

-

OBT-BSP-VxWorks6.7 S698-T平台应用开发手册v22022-06-09 242

-

S698-T芯片开发系统S698T-Dkit使用说明书下载2022-06-09 253

全部0条评论

快来发表一下你的评论吧 !