jk触发器功能特点介绍

电子常识

描述

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。

jk触发器功能描述

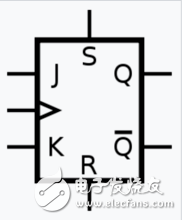

JK触发器逻辑简图如下图所示

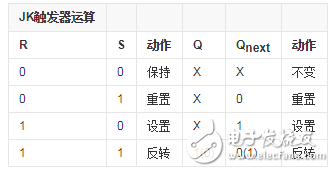

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。也就是说,原来是0的话,变成1;原来是1的话,变成0。对应表如下:

主从JK触发器工作特性

建立时间:是指输入信号应先于CP信号到达的时间,用tset表示。J、K信号只要不迟于CP信号到达即可,因此有tset=0。

保持时间:为保证触发器可靠翻转,输入信号需要保持一定的时间。保持时间用tH表示。如果要求CP=1期间J、K的状态保持不变,而CP=1的时间为tWH,则应满足:tH≥tWH。

传输延迟时间:若将从CP下降沿开始到输出端新状态稳定地建立起来的这段时间定义为传输时间,则有:tPLH=3tpdtPHL=4tpd最高时钟频率:因为主从触发器都是由两个同步RS触发器组成的,所以由同步RS触发器的动态特性可知,为保证主触发器的可靠翻转,CP高电平的持续时间tWH应大于3tpd。同理,为保证从触发器能可靠地翻转,CP低电平的持续时间tWL也应大于3tpd。因此,时钟信号的最小周期为:Tc(min)≥6tpd最高时钟频率fc(max)≤1/6tpd。

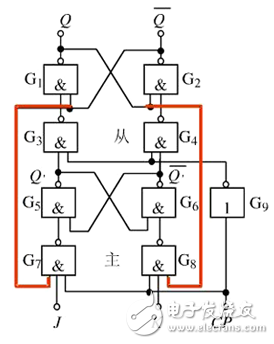

主从JK触发器电路图

主从JK触发器特点

1.主从JK触发器具有置位、复位、保持(记忆)和计数功能;

2.主从JK触发器属于脉冲触发方式,触发翻转只在时钟脉冲的负跳变沿发生;

3.不存在约束条件,但存在一次变化现象。

4.产生一次变化的原因是因为在CP=1期间,主触发器一直在接收数据,但主触发器在某些条件下(Q=0,CP=1期间J端出现正跳沿干扰或Q=1,CP=1期间K端出现正跳沿干扰),不能完全随输入信号的变化而发生相应的变化,以至影响从触发器 状态与输入信号的不对应。

-

JK触发器基本教程,讲的超详细!!2021-02-01 0

-

jk触发器是什么原理2021-02-26 0

-

JK触发器,JK触发器是什么意思2010-03-08 6194

-

JK触发器原理是什么?2010-03-08 23511

-

JK触发器工作原理详细介绍2010-03-08 50815

-

jk触发器实现74ls194功能2017-12-22 22282

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 179091

-

jk边沿触发器工作原理2018-01-30 35701

-

jk触发器逻辑表达式是什么?2018-02-08 50551

-

JK触发器的特性表及状态转换图介绍2018-02-08 66153

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 85321

-

JK触发器与RS触发器是如何构成的有什么区别2020-05-09 7388

-

t触发器和jk触发器的区别和联系2024-02-06 984

-

如何用jk触发器构成t触发器?t触发器逻辑功能有哪些2024-02-06 1151

-

Jk触发器的故事2024-02-23 256

全部0条评论

快来发表一下你的评论吧 !