SDSoC就绪,它如何在实际的设计开发工作中支持你的“表演”

可编程逻辑

描述

想必大家通过之前的SDSoC系列文章,已经了解到如何构建一个SDSoC开发平台,并熟悉了SDSoC便捷的开发流程,可以说舞台已经搭好,现在就该你去完成自己的设计开发大“秀”了!

我们还是通过一个应用范例,来看看SDSoC在实际的设计开发工作中是如何支持你的“表演”的。

由于SDSoC设计实施上的灵活性,它被作为视频处理的理想平台,通过它可以创建一个优化的视频处理系统,在处理性能、成本、功耗和开发时间等要素之间实现平衡。

具体地讲,你可以在设计中将那些像素级的、性能要求较高的处理工作可以放在PL(可编程逻辑)中完成,同时由PS(处理器系统)去担负那些非关键的、系统级的处理工作,比如文件处理和帧级的视频处理。

同时,SDSoC丰富的设计资源这时也会帮到你。OpenCV已经与SDSoC紧密地集成在一起,它可以提供丰富、强大的视频处理函数。

赛灵思提供了50+高度优化的OpenCV函数(被称为xfopencv库),帮助用户加速其视频处理应用开发进程。其他通过SDSoC由HLS高级综合引擎生成的函数,也可以放在FPGA可编程逻辑中进行加速。

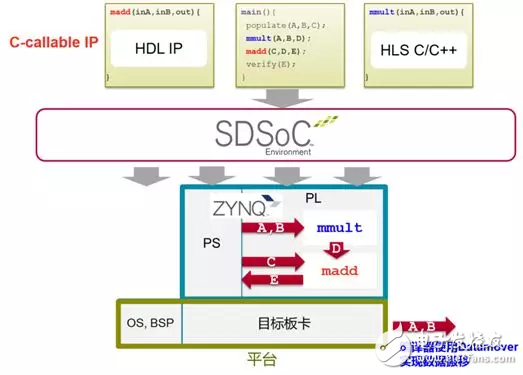

图1,SDSoC应用开发示意(图片来源:赛灵思)

我们再来将SDSoC应用开发的整个过程做个梳理。

首先,开发者可以将需要在PL中加速的功能由C/C++写成算法,或是通过Vivado HLS生成IP,也可以是由HDL硬件描述语言写成的C语言可调用的IP,并将这些设计源代码导入SDSoC。

然后,我们对需要实现的功能进行软、硬件分区,这个过程用户只需在SDSoC中选择并指定那些需要硬件加速的功能函数即可,十分方便。

接下来,SDSoC会根据用户的软硬件分区来生成PS和PL之间的DataMover、配置硬件接口和软件驱动,输出成Vivado IPI工程,同时提供全系统性能分析和估算,全部工作都由系统自动完成。然后,用户可以根据需要对系统实现方式进行干预和改动,以达到满意的效果。

最后,SDSoC可以输出整个设计的FPGA比特流文件和可以用来启动操作系统的软件引导映像。

最后总结一下:SDSoC并非要取代以前那些大家已经熟知的Zynq SoC独立开发工具,而是将它们集成在了一个统一的开发环境中,并提供一个真正端到端的优化设计流程,让以前需要不同开发团队花费大量时间协作完成的复杂工作,得以简化,也让更多没有FPGA设计经验的系统架构和软件工程师,能够轻松驾驭Zynq SoC这个全可编程设计平台,在这个创新的平台架构上,开始他们的表演!

-

CC2540工程如何在C的工程中支持C++?2016-03-21 0

-

下载SDSoC,获得SDx2018-12-27 0

-

SDSoC试用许可证弹出一条错误消息2019-01-02 0

-

启动SDSoC 2016.1时,SDSoC无法找到清单文件错误2019-04-26 0

-

如何在SDSOC功能内手动从PL产生中断?2020-05-08 0

-

请问如何在Zynq Z-7020上使用opencl?2020-05-15 0

-

如何在贴片工作中选择锡膏?2021-04-23 0

-

NOW!Xilinx SDSoC开发环境支持16nm Zynq UltraScale+ MPSoC器件2017-02-08 214

-

什么是SDSoC平台?SDSoC的开发工作2018-06-04 7796

-

SDSoC开发:面临的挑战及解决方案2018-11-20 2020

-

SDSoC开发环境:功能优化和问题解决2018-11-22 2315

-

赛灵思SDSoC 开发教程2019-08-01 1653

-

Git在实际工作中的基本使用方法2020-09-14 2297

-

Git在实际工作中的使用方法2020-09-21 2907

-

开发工作中必不可少的5个工具2020-11-07 2161

全部0条评论

快来发表一下你的评论吧 !