Xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

FPGA/ASIC技术

描述

之前用serdes一直都是跑的比较低速的应用,3.125Gbps,按照官方文档一步一步来都没出过什么问题,这次想验证一下K7系列GTX最高线速8Gbps,看看xilinx的FPGA是不是如官方文档所说。

GTX速度到底可以跑到多少

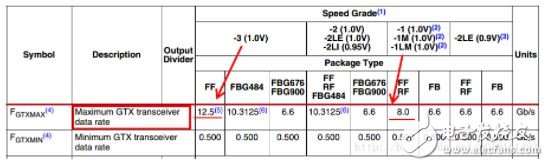

关于器件速度的问题首先找到 ds182->Kintex-7 FPGAs Data Sheet:DC and AC Switching Characteristics,可以自己对应的器件去找,不过这个在设计电路板器件选型的时候就应该考虑到,除非是买的开发部学习用。这里面包括所有的FPGA各个器件能跑到的最高频率和器件延时,建立时间,保持时间等,对高速设计有很大的参考价值。

找到GTX Transceiver Switching Characteristics

可以看到,虽然K7系列GTX最高可以跑到12.5Gbps,但这跟速度等级和封装都有关系,是在-3的速度等级,FF封装下才有的最高速度12.5Gbps。而现在手头的芯片型号是K7480TFFG901-1,所以最高支持8.0Gbps。其实这在配置IP核的时候就会发现了,线速范围是(0.5-8.0)。所以IP核都是严格和工程的器件相关联的,这点Vivado越做越好了。

一步一步配置IP核

下面一步步配置IP核,可以作为初学者参考。(第一次用的话,会被生成的一大堆文件和巨多的IO口吓到的。)包括怎么查找手册和原理图,走一遍流程,发现其实xilinx的IP核都是一个套路。

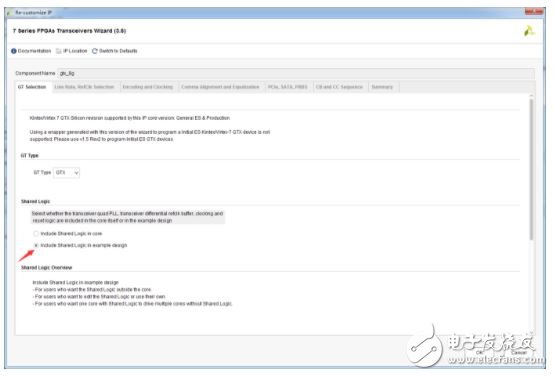

1. 首先在IP核搜索GT,选择7 Series FPGAs TransceiversWizard,

没得选的,取个名字。顺便提一下,下面的shared logic选项,最好选include shared logic in example design。在有些特殊资源需要共享时,曾经遇到过这里的问题。当然不是GTX模块,是以太网的RGMII的模块,其中的IDELAY要用到IODELAY_CTRL,一个IOB就一个,同一个IOB其它地方要用到的时候必须选下面一个选项。所以最好都选下面一个,没毛病。

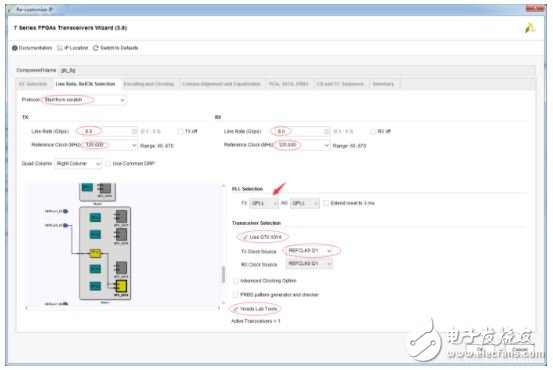

2. 接下来就比较重要了

首先是协议,最简单的strat from cratch,就是没有协议。然后是线速,可以看到范围是(0.5-8.0)。参考时钟,这个可以根据需要选个合适的。软件都根据你的线速把参考时钟的可选项计算好了。接收端同样设置,当然可以不一样的。这是全双工,收发链路没有什么关系,也可以关掉其中一个Tx off 或Rx off。然后是PLL选择,到底选哪个呢?我们回到刚开始提到的ds182,同样一个表格下部分

其实线速决定了没得选,已经变成灰色了。

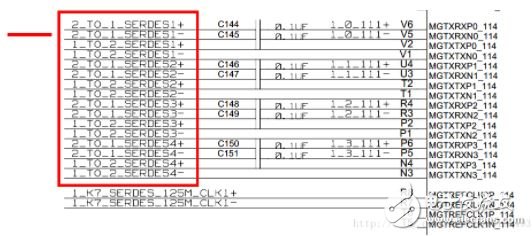

然后是比较重要的,选择用哪个收发器,这当然不是拍脑袋决定的,跟设计有关,可以查找原理图。

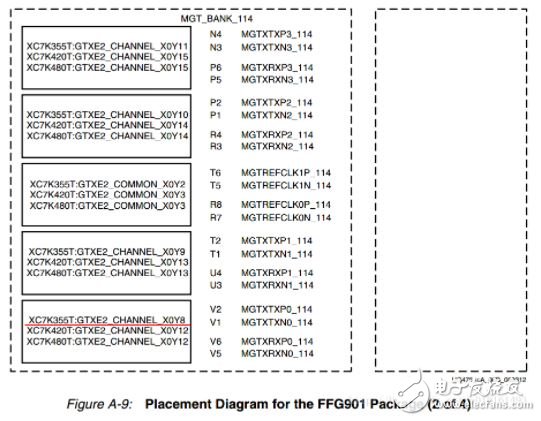

比如说这样的,然后去查手册UG476-> 7 Series FPGAsGTX/GTH Transceivers 找到 Placement Information by Package如下

这样就知道用的是X0Y8,输入时钟在上面的原理图可以找到,是同一组的clk0。

最后,把vivado lab tools勾上,这样才可以生产example工程可以参考。

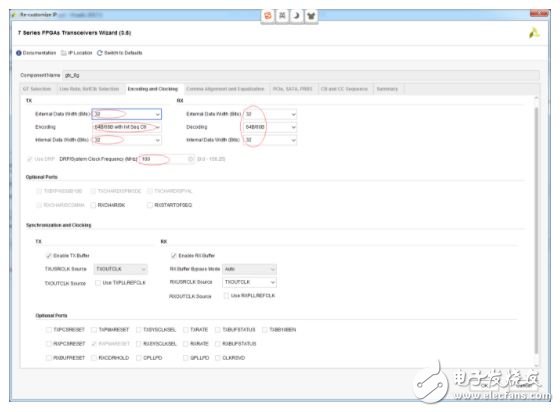

3. 继续

之前一直用的是8b10b,这次尝试一下64b66b,后者本来就是高带宽下的一个编码协议,效率更高。为什么要用8b10b,64b66b包括后面的扰码一句话概括就是增加频率分量有利于CDR(时钟数据恢复)和减少直流,两个是不同的原因。具体的可以百度。最下面的可选端口为了简单,全部去掉。

4.

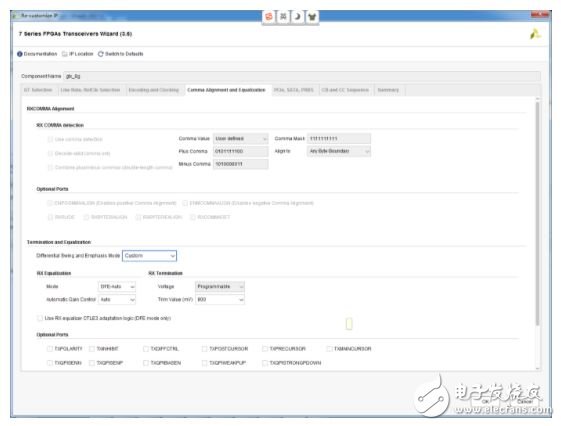

由于没有选择8b10b,这一页也没什么可选的,依然把下面的可选端口全部去掉。

5.

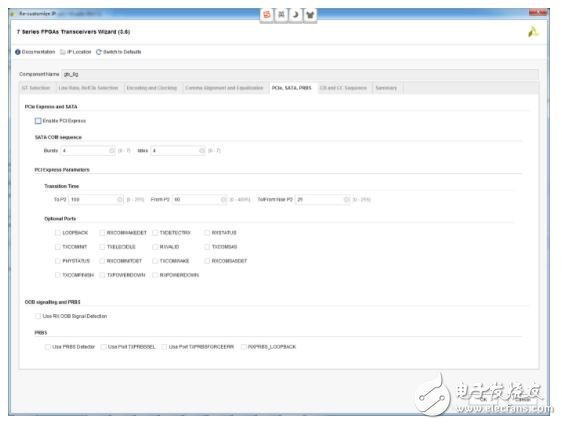

好了,pcie留着下次研究,太复杂了。可选端口其实有的挺有用的,增加了可控性,比如说环回控制,LOOPBACK。顺便说一下内部环回有四种,

1.“000”:正常模式不环回

2.“001”:近端PCS环回

3.“010”:近端PMA环回

4.“100”:远端PMA环回

5.“110”:远端PCS环回)

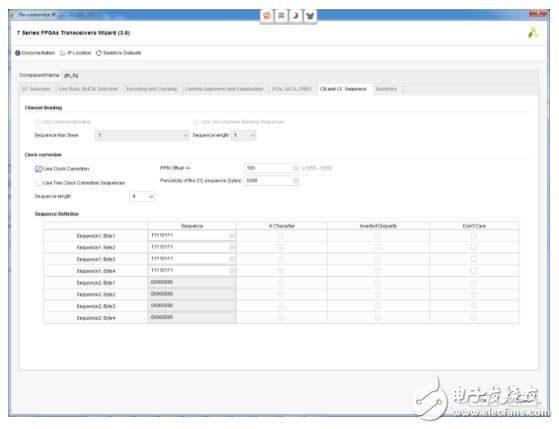

6.接下来是通道绑定和时钟校正

通道绑定的作用是把多个物理通道对齐,绑定成一个的逻辑通道。其实就是用FIFO消除通道间的延时不确定性。由于只有一个通道,没有绑定可言。

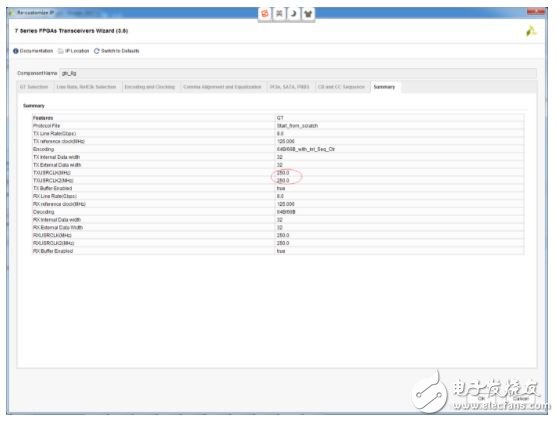

7. 最后看一下确定对不对,注意收发时钟是250M。可以算一下,8000M/32=250M。

到这里完成一大半了。

利用IP核生成example工程

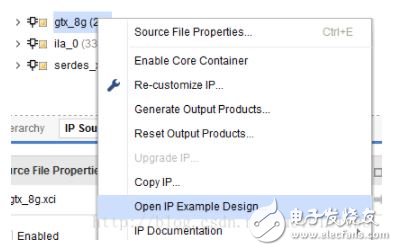

接下来生成example工程

把刚刚配置的IP右键,如图选择。

生成好后稍微改一下约束文件XDC,把DRC时钟的输入时钟约束一下。其他的不用管。

## LOC constrain for DRP_CLK_P/N

set_property LOC G27 [get_ports DRP_CLK_IN_P]

set_property LOC F27 [get_ports DRP_CLK_IN_N]

set_property IOSTANDARD LVDS_25 [get_ports DRP_CLK_IN_P]

set_property IOSTANDARD LVDS_25 [get_ports DRP_CLK_IN_N]

可以发现直接在这儿可以改具体使用的哪个收发器。注意:在这里改的效果和上面第2步里面设置的效果一样。

set_property LOC GTXE2_CHANNEL_X0Y4 [get_cells gtx_8g_support_i/gtx_8g_init_i/inst/gtx_8g_i/gt0_gtx_8g_i/gtxe2_i]

要改的话,当然同时GTX的时钟也得改

set_property LOC AD5 [get_ports Q1_CLK0_GTREFCLK_PAD_N_IN ]

set_property LOC AD6 [get_ports Q1_CLK0_GTREFCLK_PAD_P_IN ]

再修改一个地方,原来的ILA核抓的是解扰码前的数据,替换成解扰码后的数据可以更清楚的看到接收到的数据。

上板调试验证

好了,生成bit下进去,可以用连接线接上连个serdes的一收一发换回,或者设置内部环回,或者在两片FPGA上做实验。

可以看到error_count一直是0,说明收发正确,很稳定。

收到的数据依次是00000fb,3020100,7060504…依次递增,打开发送文件如下,和发送的一样。

00000000000000fb0100

00000000030201000000

00000000070605040000

000000000b0a09080000

实验成功证明了GTX可以跑到最高8.0Gbps。

生成的example工程可以好好研究学习一下,里面有加扰码和解扰码的过程,自己修改一下把解扰码后的数据抓出来对比一下,可以很清楚的看到收到了什么数据。包括校验模块是怎么校验的,还是值得一学的。

-

【图文教程】菜鸟教你如何一步一步免费建一个网站!2011-11-15 0

-

转载:一步一步教你使用uCOS-II 资料整理2012-08-04 0

-

一步一步教你开发嵌入式linux应用程序2012-08-13 0

-

Xilinx-ISE-DS-14.3安装的最后一步licenses怎么安装2012-11-02 0

-

Xilinx-ISE 最后一步licenses怎么安装2012-11-02 0

-

一步一步教你使用uCOS-II组合2013-08-27 0

-

Allegro PCB SI一步一步学会前仿真2014-05-16 0

-

怎么让直流电源执行时 一步一步执行2018-03-08 0

-

一步一步教你远程控制2018-05-26 0

-

详解一步一步设计开关电源2019-06-20 0

-

为什么我按照视频一步一步的做还是有这么多错误?2019-09-17 0

-

反激38个步骤,教你一步一步设计开关电源2020-03-20 0

-

教你怎样一步一步去建立STM32工程呢2021-10-28 0

-

手把手教你如何一步一步实现人脸识别的门禁系统2021-12-14 0

-

stm32是如何将配置从库函数调用一步一步到寄存器的2022-02-15 0

全部0条评论

快来发表一下你的评论吧 !