MCU健壮性设计之CAN时钟

电子说

1.2w人已加入

描述

在一个CAN网络中,如果希望有良好的读位,那么采样点的时间位置相对来说是非常重要的。因此,所有的网络节点都有质量时钟。然而,石英和谐振器有公差,会随着温度和时间漂移。只要变量保持在一个公差范围内,协议管理器就可以补偿错误。

CAN协议的建议要求对时钟频率最大限度的最大限度地容忍1.58%。

在这种情况下,建议直接使用石英或谐振器的时钟,而不是由PLL产生的系统时钟。实际上,PLL(抖动)的频率变化是无法满足要求的精度的。

根据µC的类型,它可能会导致改变石英频率以获得网络排放的愿望。让我们以一个可以使用500 kbit/s波特率的网络为例,在这种情况下,CAN总线的频率必须在8MHz上配置。

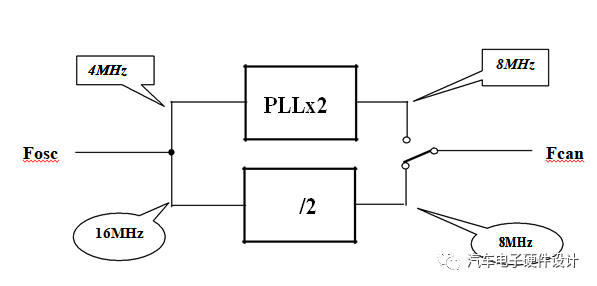

在图30的结构中,4MHz的quartz足以满足选择的PLL(x2)。另一方面,通过避免PLL,16MHz的石英是必要的

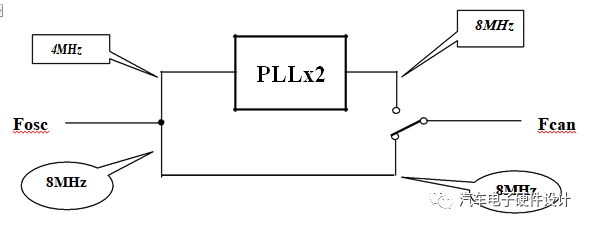

在图31的结构中,没有PLL的连接是直接的。在这种情况下,可以保留8MHz的石英。

PLL稳定性(jitter)的总线通信(特别是高速CAN、FlexRay.)应用中被考虑到。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

双MCU的CAN总线中继器设计2012-01-12 0

-

LabVIEW程序评估_健壮性和简单性2019-08-24 0

-

I2C串行EEPROM应用系统的健壮性设计2020-06-30 0

-

CAN标准中的时钟容差修正建议2010-01-08 3137

-

基于负载率基尼系数的含风电电网健壮性分析_王辉2016-12-29 508

-

提高多边形布尔运算健壮性的顶点融合技术_白萌2017-03-15 725

-

MCU健壮性设计之如何配置数字输入/输出2018-03-09 5763

-

MCU健壮性设计之模拟输入的特殊特性2019-05-05 3408

-

如何在IAR Embedded Workbench中填充提高系统的健壮性2022-11-03 967

-

CAN与CAN FD的区别是什么?2023-05-22 16991

-

菱沃铂MCU的时钟配置2023-07-18 405

-

RA2L1:使用CLKOUT给MCU CAN模块提供时钟2023-11-02 338

全部0条评论

快来发表一下你的评论吧 !