CMOS运算放大器摆动,为何可小于1到2毫伏

描述

轨至轨放大器可产生极为接近接地的输出电压……但到底接近到什么程度呢?我们谈的是CMOS运算放大器。当你正努力最大化输出电压摆动时,它常用于低压设计。这些器件的规格通常如下:

这让它看起来,输出绝不会比15mV更接近接地,而最后一个15mV对于准确的零式测量至关重要。但请等一下……你的确需要仔细理解这种规格的所有状态。假设负载在两个电源端之间“半”连接。我们通常可在规格表的顶部看到这些状态,你会看一条如下声明…….

RL 连接至 VS/2.

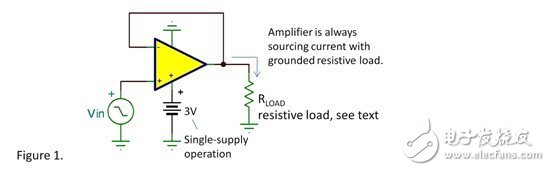

在这种规格状态下,在输出靠近接地时,放大器必须通过负载电阻器吸取电流。它反映了放大器测试的方法,其确保它能够正确地输出和吸取电流。这是测试和规定放大器的一种明智、保守的方法,但它却不是连接你的负载的方法。假设你的负载如图1所示连接接地。负载电阻器实际帮助下拉输出至接地,而吸取电流也无需放大器。

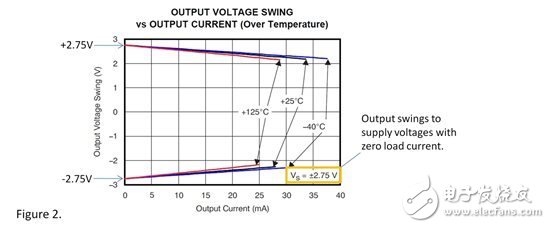

在这种状态下,大多数CMOS运算放大器的摆动均可非常接近接地—小于1到2毫伏。规格可能并没有重点说明这种能力,但其已显示在图中。图2表明,输出电压摆动与输出电流相关。该图可能受益于高精度,但你会看到在进行这种测试时输出电压与具体的电压轨相交,即±2.75V。单电源工作时,V-电源等于0V。

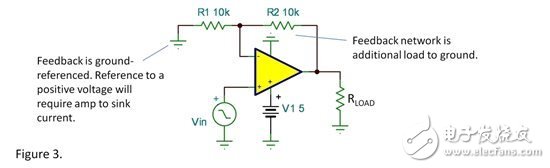

现在,我需要增加一些附加条件。注意,在图3中,反馈网络参考接地。你需要考虑放大器负载的所有源,不仅仅只是RL。在这种情况下,R1 + R2为同RL并联的有效附加接地参考负载。但是,如果R1参考正电压,则输出接近0V时需要放大器来吸取来自反馈网络的电流,并且输出摆动无法非常接近接地。

另一个附加条件。在同一块电路中,如果增益增高,则输入偏置电压可能会使你的输出摆动变小。例如,G=20时,如果输入为+1mV运算放大器的偏置电压,零输入将产生20mV输出。这不是由于输出摆动限制,而是偏置电压问题。当然,小负输入电压可带来极为接近0V的输出,但你的电路绝不会有负输入电压。

再次—反应式负载AC信号或许是一个例外。负载电流和电压与反应式负载不同相,因此输出电压接近接地时可能要求放大器来吸取电流。

最后—我们谈的是CMOS运算放大器。双极(BJT)运算放大器摆动无法如此接近接地。

低压、电池供电型电路具有挑战性,因为我们好像始终都在努力最大化电压摆动。较好地理解运算放大器的性能以后,你才能挤出更多的输出摆动,以接近接地。

-

基于低功耗 RRO 全差动运算放大器的轨到轨输出范围以实现真正零伏包括原理图,物料清单及光绘文件2018-08-02 0

-

靠近接地摆动:单电源工作2018-09-21 0

-

转向特定应用的运算放大器2018-10-22 0

-

运算放大器问题2019-05-31 0

-

运算放大器电路出现误差?你需要了解失调电压与开环增益的关系2019-09-24 0

-

运算放大器:详解电路中的失调电压与开环增益2019-09-27 0

-

LMC662 CMOS双运算放大器的中文资料2020-07-10 0

-

LMC6032 CMOS双运算放大器的中文资料2020-07-10 0

-

轨到轨运算放大器2020-07-23 0

-

LPC660 CMOS四路运算放大器解析2020-09-11 0

-

OPA2348单电源低功耗CMOS运算放大器解析2020-09-25 0

-

单电源操作的LMC662 CMOS双运算放大器2020-09-25 0

-

OPA336系列微功耗CMOS运算放大器介绍2020-09-27 0

-

恒跨导轨对轨CMOS运算放大器的设计2017-01-07 681

-

CMOS运算放大器的设计和优化2021-04-13 1196

全部0条评论

快来发表一下你的评论吧 !