以计数器为32位为例:FPGA中计数器设计探索

电子说

1.2w人已加入

描述

我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。

FPGA中计数器设计探索,以计数器为32位为例:

第一种方式,直接定义32位计数器。

reg [31:0]count;

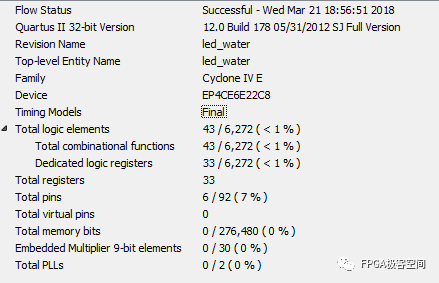

quartus ii 下的编译,资源消耗情况。

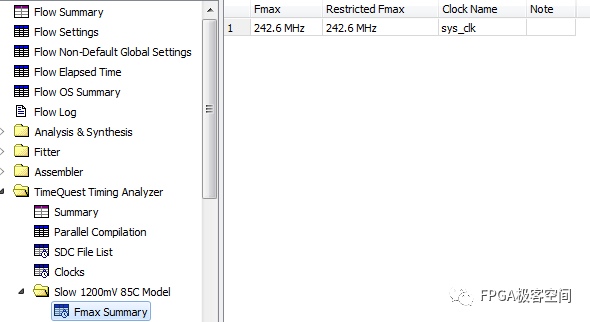

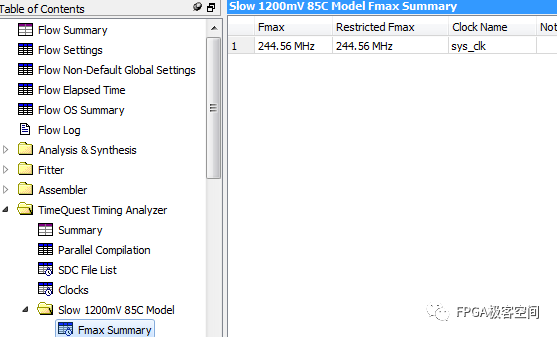

85C模型下的时钟频率。

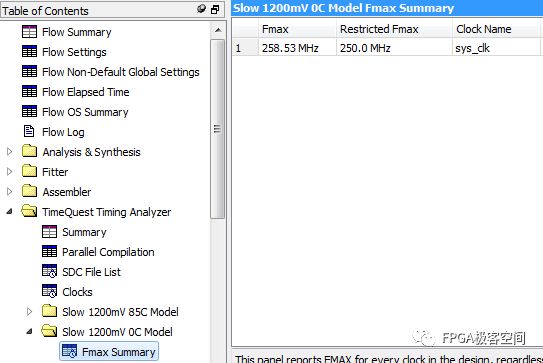

0C模型下的时钟频率。

chip planner下资源分布情况。

第二种方式,定义2个16位计数器。

reg [15:0]count1,count2;

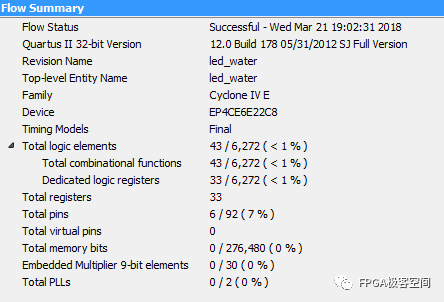

quartus ii 下的编译,资源消耗情况。

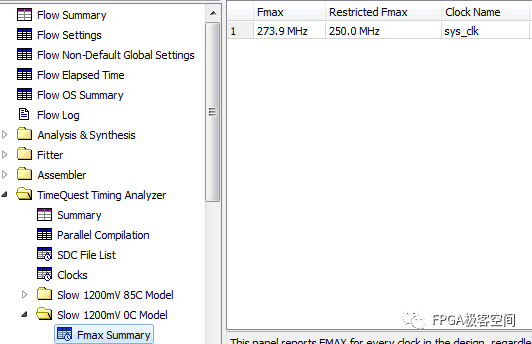

85C模型下的时钟频率。

0C模型下的时钟频率。

chip planner下资源分布情况

从上述两种情况来看,结合C4内部LAB的结构,两种方式消耗资源一样多,两种模型下的时钟频率比较接近。

值得注意的是,以上测试是在资源足够频率不高的条件下测试的。根据经验,当资源使用较多,时钟频频较高时,建议使用方式二。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

以计数器IP核为例了解IP使用流程2019-03-04 0

-

定时计数器有什么功能?2020-03-23 0

-

定时/计数器的原理是什么2021-07-19 0

-

定时器/计数器8253内部有多少个16位的计数器2021-10-20 0

-

计数器是什么?如何使用计数器2022-02-28 0

-

计数器的级连使用2007-11-22 3409

-

计数器2009-09-30 1440

-

环形计数器和扭环形计数器2010-01-12 9230

-

计数器,计数器的工作原理是什么?2010-03-08 60063

-

基于FPGA的PWM计数器改进设计2012-04-06 1867

-

FPGA之计数器的使用2019-09-03 5400

-

PLC编程中计数器的存储区介绍2021-12-21 2643

-

基于FPGA的十进制计数器2022-12-20 546

-

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?2023-03-25 19436

-

计数器怎么用 计数器的作用有哪些2024-02-03 1199

全部0条评论

快来发表一下你的评论吧 !