技术控:FPGA中RAM使用技巧探索

电子说

1.2w人已加入

描述

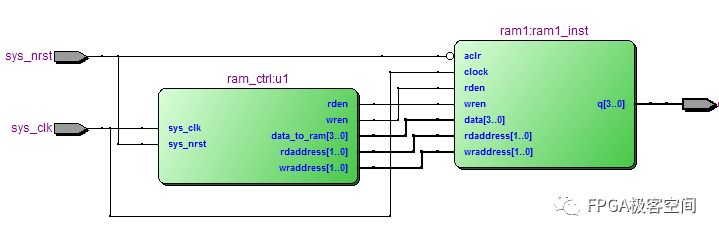

FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

第一种方式,直接调用4bitX4的RAM。编写控制逻辑对齐进行读写。

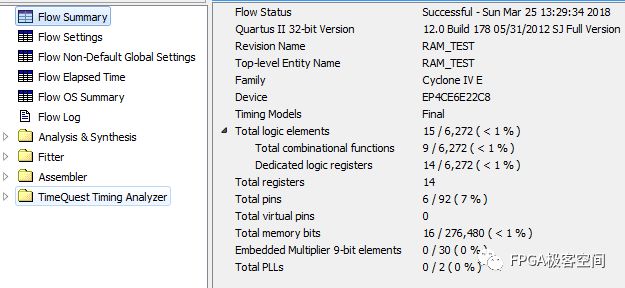

quartus ii 下的编译,资源消耗情况。

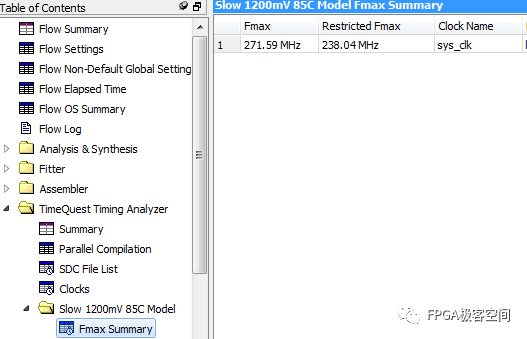

85C模型下的时钟频率。

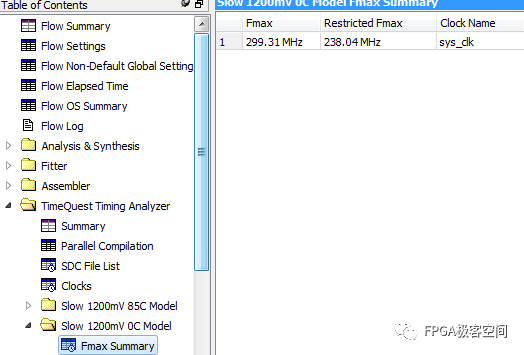

0C模型下的时钟频率。

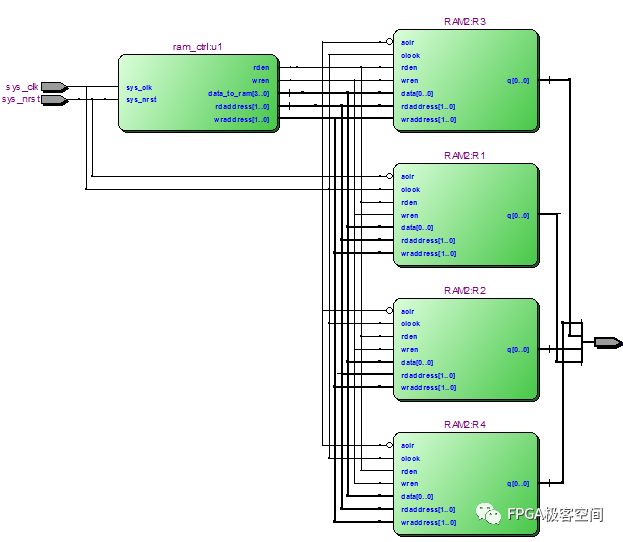

第二种方式,调用1bitX4的RAM,例化4次。编写控制逻辑对齐进行读写。

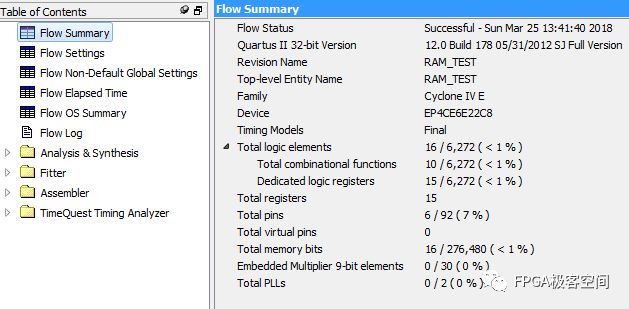

quartus ii 下的编译,资源消耗情况。

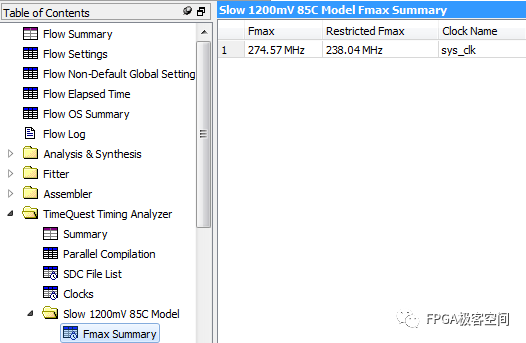

85C模型下的时钟频率。

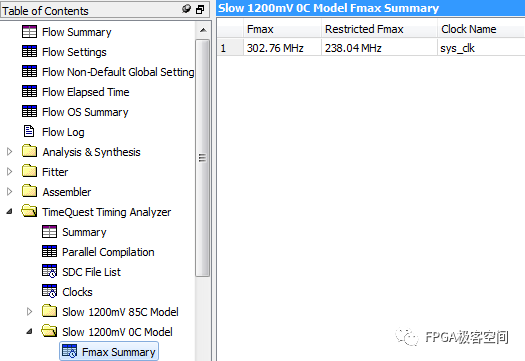

0C模型下的时钟频率。

从上述两种情况来看,两种RAM的使用方式,最终使用资源比较接近,方案二稍多,而从时序模型综合结果看,方案二的时钟频率明显比方案一高。在高速情况下,建议使用方案二。同样在位宽较宽情况下,可使用生成块语句进行例化,减少顶层对同一模块的例化数,是比较方便的。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

在FPGA中的RAM有与其他产品有什么不同?2018-08-23 0

-

如何实现ASIC RAM替换为FPGA RAM?2020-04-24 0

-

如何读出LUT中RAM的上电值?2020-06-18 0

-

基于FPGA的双口RAM实现及应用2010-02-11 486

-

基于Actel FPGA的双端口RAM设计2010-11-15 686

-

利用FPGA实现双口RAM的设计及应用2010-04-16 11366

-

_FPGA内部的RAM M9K2017-04-07 2134

-

Spartan-6 FPGA块RAM的技术参考资料免费下载2019-02-15 1134

-

FPGA硬件基础之FPGA的RAM存储课件和工程文件2020-12-10 616

-

使用FPGA调用RAM资源的详细说明2020-12-30 1189

-

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作2022-02-08 12346

-

FPGA在一个时钟周期可以读取多个RAM数据吗?2023-10-18 684

-

FPGA中块RAM的分布和特性2023-11-21 637

-

fpga双口ram的使用2024-03-15 174

全部0条评论

快来发表一下你的评论吧 !