cd4046中文资料汇总(cd4046引脚图及功能_用途及应用电路)

芯片引脚图

描述

cd4046简介

cD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

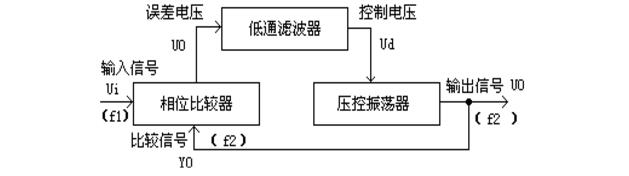

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如下所示。

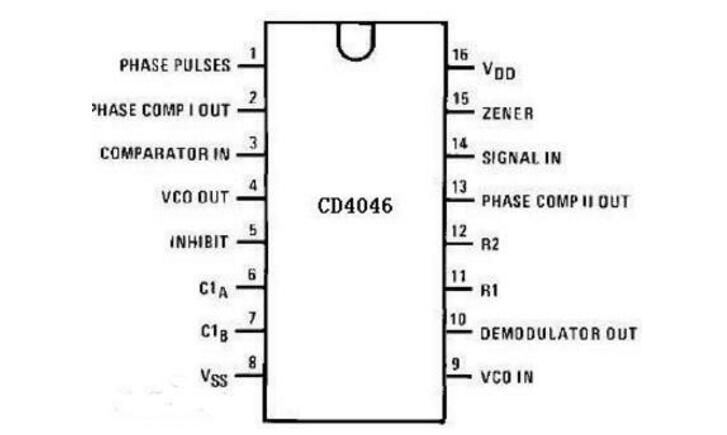

cd4046引脚图及功能

CD4046的引脚排列,采用16脚双列直插式,各管脚功能:

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

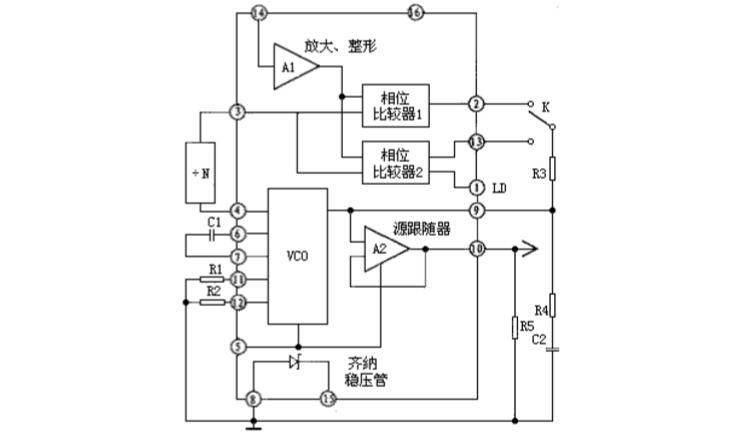

CD4046内部电原理框图

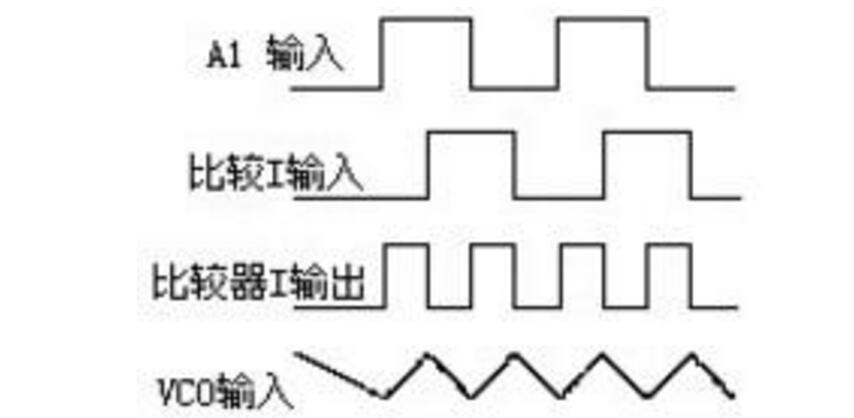

上图是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。比较器Ⅰ采用异或门结构,当两个输入端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。从图中还可知,fout不一定是对称波形。对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

图四

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

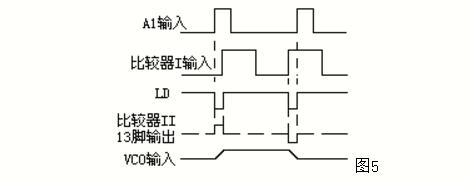

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。如果两信号的频率相同而相位不同,当输入信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。上述波形如图5所示。由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

CD4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。由于VCO是一个电压控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。VCO振荡频率的范围由R1、R2和C1决定。由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。一般规定CD4046的最高频率为1.2MHz(VDD=15V),若VDD《15V,则fmax要降低一些。

CD4046工作原理

输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同。

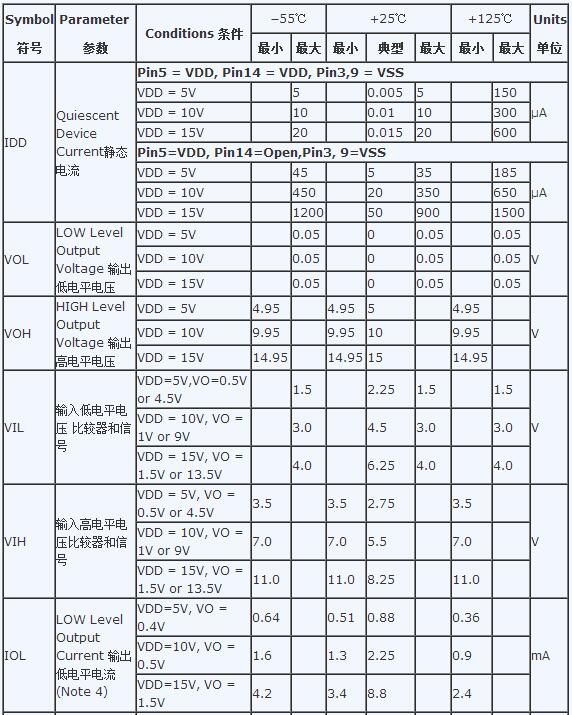

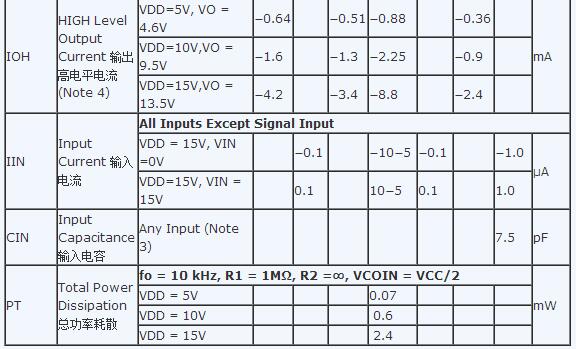

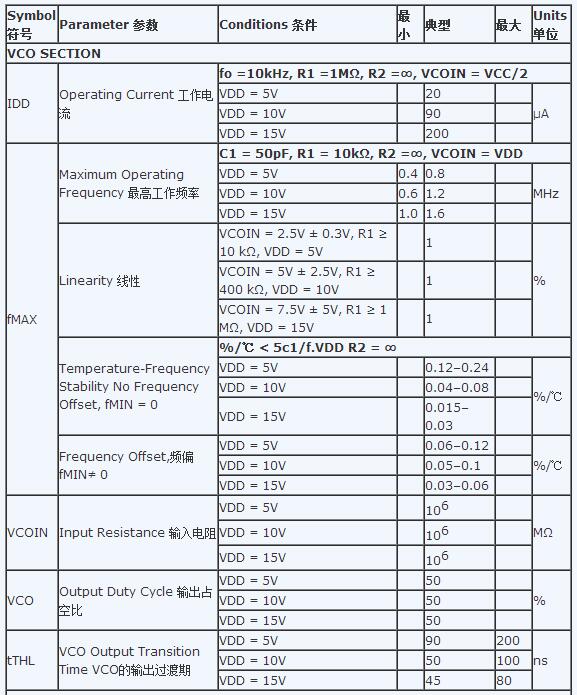

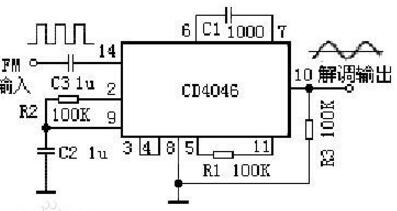

cd4046电气特性

直流电气特性:

交流电气特性:

CD4046典型应用电路

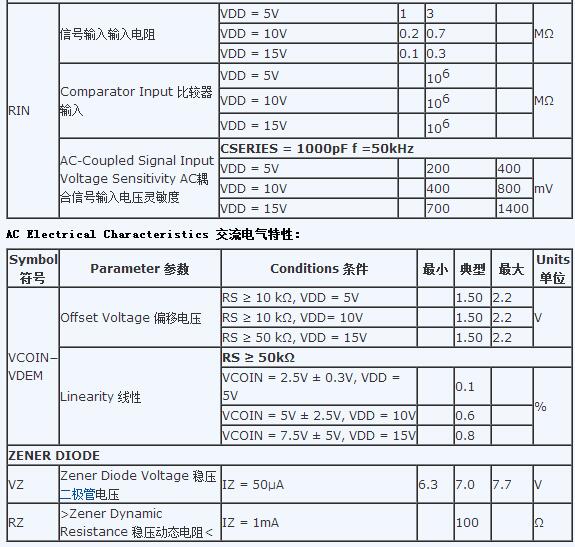

应用电路一:

图中是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。振荡器的充、放电电容C1接在6脚与7脚之间,调节电阻R1阻值即可调整振荡器振荡频率,振荡方波信号从4脚输出。按图示数值,振荡频率变化范围在20Hz至2kHz。

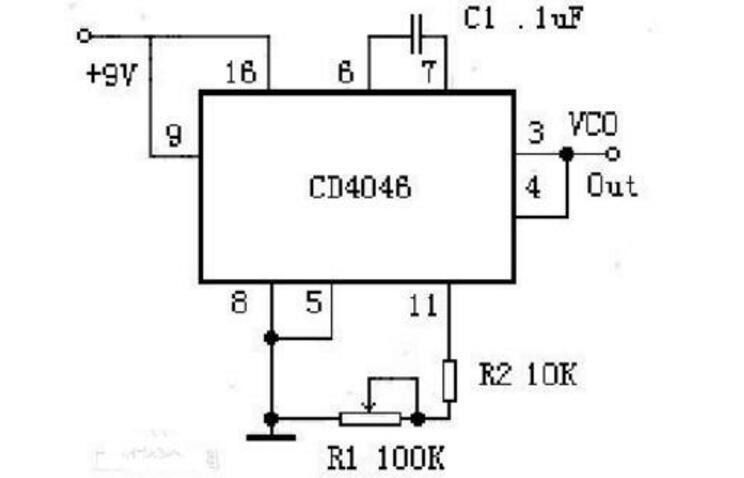

应用电路二:

图是CD4046锁相环用于调频信号的解调电路。如果由载频为10kHz组成的调频信号,用400Hz音频信号调制,假如调频信号的总振幅小于400mV时,用CD4046时则应经放大器放大后用交流耦合到锁相环的14脚输入端环路的相位比较器采用比较器Ⅰ,因为需要锁相环系统中的中心频率f0等于调频信号的载频,这样会引起压控振荡器输出与输入信号输入间产生不同的相位差,从而在压控振荡器输入端产生与输入信号频率变化相应的电压变化,这个电压变化经源跟随器隔离后在压控振荡器的解调输出端10脚输出解调信号。当VDD为10V,R1为10kΩ,C1为100pF时,锁相环路的捕捉范围为±0.4kHz。解调器输出幅度取决于源跟随器外接电阻R3值的大小。

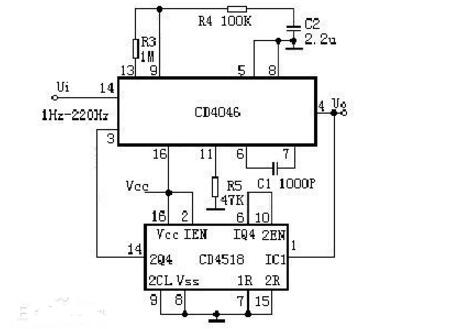

应用电路三:

图中用CD4046与BCD加法计数器CD4518构成的100倍频电路。刚开机时,f2可能不等于f1,假定f2《f1,此时相位比较器Ⅱ输UΨ为高电平,经滤波后Ud逐渐升高使VCO输出频率f2迅速上升,f2增大值至f2=f1,如果此时Ui滞后U0,则相位比较器Ⅱ输出UΨ为低电平。UΨ经滤波后得到的Ud信号开始下降,这就迫使VCO对f2进行微调,最后达到f2/N=f1,并且f2与f1的相位差Δφ=0°。,进入锁定状态。如果此后f1又发生变化,锁相环能再次捕获f1,使f2与f1相位锁定。

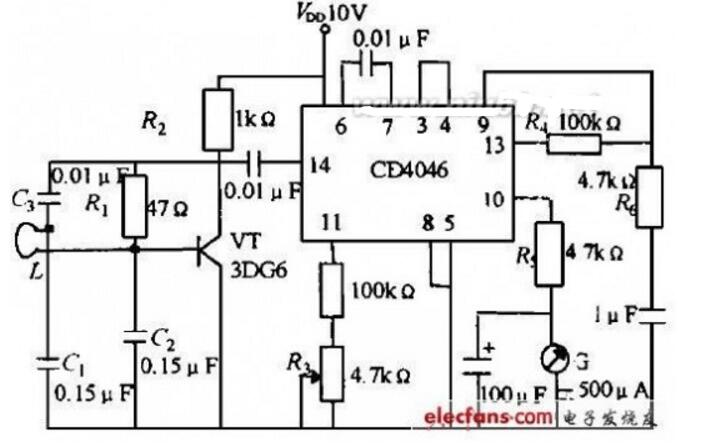

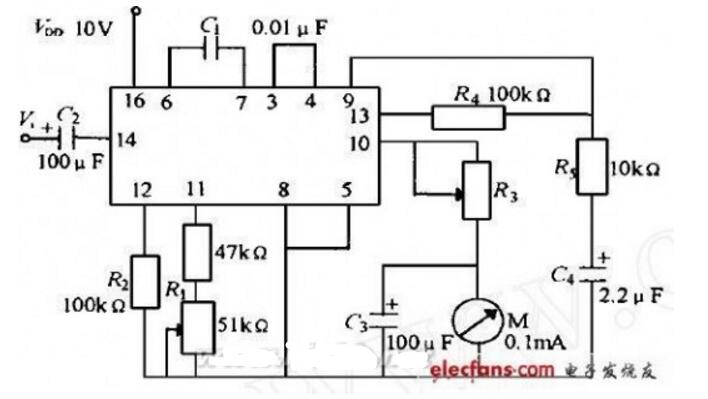

应用电路四:

频率计用表针指示被测频率的高低。R1由47k 固定电阻与51k 的电位器串联而成, R4、R5和C4构成低通滤波器, R3与表头M 串联后作为源跟随器的负载, R3还用于调节表的满刻度电流。表头上并有100LF 的大电容, 用于消除低频时表针的抖动现象, 该频率计的测量范围是20Hz~ 1kHz。在用标准信号发生器和标准频率计进行校准时, 需调整51k 电位器, 该频率计具有良好的线性。

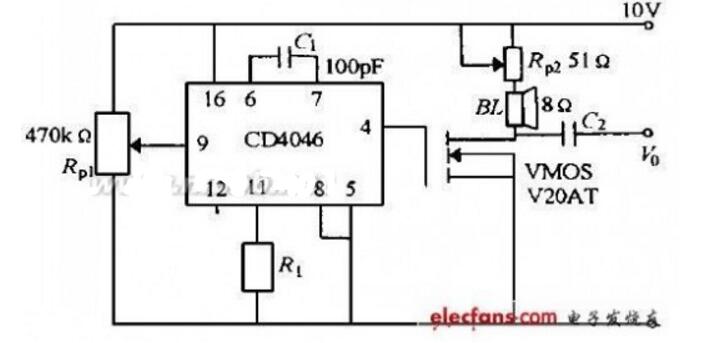

应用电路五:

只使用锁相环中的压控振荡器就可构成电压频率转换器。电路的特点是将12脚悬空,使R2趋向无穷大,则输出的最小频率为0Hz,取R1=100k,C1=100pF,VDD=10V时,输出的最高频率为20kHz。改变电位器RP1的位置,使VCO的控制电压从0V连续升到VDD,从第4脚就可以得到0Hz~20kHz的输出信号。VMOS管V20AT作功率输出级,监听扬声器BL与RP2组成漏极负载,RP2兼作音量控制。将RP1的频率刻度盘用标准频率计校准后,即可作为音频信号发生器使用。该电路如果去掉RP1,改用敏感元件和电压比较电路构成输入级,即为多用途越限报警器。

应用电路六:

VT与C1、C2、探头L一起组成振荡器,其频率约为300kHz。探头采用直径为440毫米的线圈。当探头接近埋在地下的金属时,金属物体相当于短路环,使L的电感量减小,振荡频率随之升高,表针偏转角度改变。表头易采用零位指示器,零点位于刻度盘中央,此电路仍属于频率电压转换电路。

- 相关推荐

- CD4046

-

CD4046解调 求解。。。2012-11-04 0

-

求助关于CD4046鉴相器的问题2012-11-15 0

-

请教各位关于CD4046的问题2012-11-15 0

-

multisim中的CD4046仿真模型2014-12-19 0

-

proteus中CD4046为什么没有8和16引脚啊。。。。。。2016-04-08 0

-

CD4046的上限下限频率的取值问题2016-06-21 0

-

CD4046锁相环有什么应用?2021-05-27 0

-

求助CD4046调制解调电路2022-05-12 0

-

CD4046锁相环的应用电路2006-04-16 13449

-

cd4046内部框图2007-12-19 2291

-

CD4046中文资料2015-10-28 1769

-

cd4046引脚图及功能介绍2017-10-23 16871

-

基于CD4046构成的PLL及应用2017-12-22 9973

-

cd4046引脚图及功能_cd4046倍频电路设计详解2018-04-18 31871

-

锁相环CD4046的原理_CD4046的引脚图及功能_CD4046典型应用电路2018-04-18 20200

全部0条评论

快来发表一下你的评论吧 !