useful skew的作用及使用方法

电子说

描述

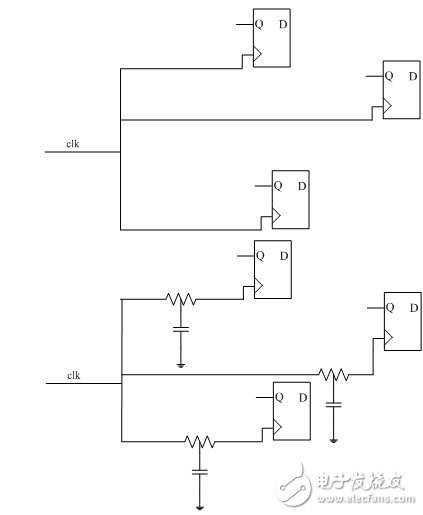

Dc综合是基于路径,每个路径上都有Cell和net,所以基于路径的综合就是计算路径上的delay和rc(dc是使用互连线模型进行估算)。

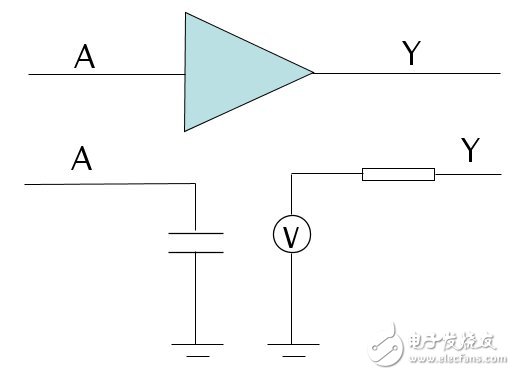

在了解delay和rc的计算时,我们要先了解一下一个cell对于drive(前级)和driven(后级)所用到的模型是什么。如下图,一个buffer,从前级看过来是一个load(capacitance,想获得这个load,可以通过load_of buffer/a获得),从后级看来是一个drive(resistance)。电路的的驱动能力是上一级的1/R,即电阻的倒数,驱动能力大,说明看过去的电阻小,也说明这个器件比较大(大器件有较大的驱动能力)。电路的负载能力是下一级的load(即电容)总和,负载能力大,说明能驱动下级的期间就很多。

大器件是大电容,小电阻,而小器件是小电容,大电阻。理解这些,对于dc综合以及后端apr版图都有很好的操作。

对于cell的延迟,dc是根据input_transition和out_load对应的查找表来计算的。

对于net的延迟,dc是根据wire_load_model中的fanout_length和resistance,capacitance,area的查找表计算的。

例如:

Wire_load(small){

Resistance : 0.2;

Capacitance : 1.0;

Area :0;

Slop :1.0;

Fanout_length(1,0.022);

Fanout_length(2,0.046);

Fanout_length(3,0.070);

Fanout_length(4,0.095);

}

比如现在扇出是2,

根据fanout_length(2,0.046)可以知道这个互连线的长度是0.046,然后再根据capacitance,resistence可以得出这个互连线的电容为:0.046x1.0,互连线电阻为:0.046x0.02。

如果扇出是5,在查找表中没有找到fanout_length为5的项,互连线长度将会是=fanout_length(4,0.095)+(5-4)*slop=0.095+1*1.0=1.095

得出了rc就可以计算出信号的transition时间=2.2RC。

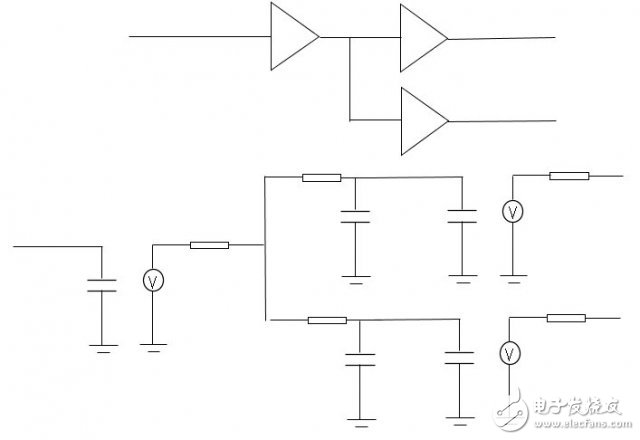

实际的互联线如下:

扇出线上的转换时间根据在版图之后提取的rc参数信息求得:

2.2RC=(Rnet+Rout)×(Cnet+Cin)

无论如何,要记住的就是dc是基于路径分析的(怎么划分路径请参考另一篇:),每个路径上有cell延迟和net延迟,而cell延迟是根据input_transition和out_lod得出的,net延迟是根据fanout_length,resistance,capacitanc得出的。驱动和电阻成反比,负载和电容成正比。

由上面可以知道fanout影响到load(capacitance),transition,delay。了解了上面,我们来理解下dc中对design建模,所用到的一些跟fanout有关的参数。

Dc中的约束,其实就是给chip设计一个环境,比如驱动这个chip输入端口的cell,或者这个chip输出端口驱动了那些单元或者端口接入了哪些负载,以及这个芯片的工艺,电压,温度,等等。。。

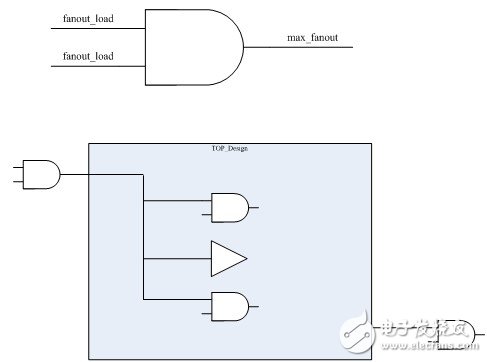

对于一个cell来说,输出端口具有max_fanout属性,输入端口有fanout_load属性。

例如将一个AND2作为design的驱动cell(set_driving_cell),这样就把AND2的max_fanout属性加在了输入端口上。如果一个AND2的输出端口max_fanout是5,输入端口fanout_load是2。一个buffer输入端口的fanout_load是3。那么这个AND2的输出端可以接2个AND2,或者可以接一个buffer,或者可以接一个buffer和一个AND2。如上图所示,则会引起DC产生DRC错误。因为输入端口的fanout_load=2XAND2+buffer=7,超过了AND2的max_fanout2.如果使用了系统提供的set_max_fanout 5 [all_inputs],将会忽略set_driving_cell中cell的max_fanout属性,而使用set_max_fanout属性

如果将一个AND2作为design的负载,那么这个输出端口上的fanout_load属性将会为2.dc中一般的做法是set_fanout_load [expr [get_attribute slow/and2/a fanout_load] *xxx] [all_outputs],来设置输出端口的fanout_load属性。

这样dc就可以根据这些设置,选择优化端口处的器件,以及时序。

说道fanout,所以顺带说明一下容易混淆的max_fanout,max_capacitance。如上图所示,

输入端口的fanout_load=2个与门的fanout_load和一个buffer的fanout_load。

输入端口的load(capacitance)=2个与门的load_of和一个buffer的load_of。(如果通过set_load设置了输入端口,另外还要加上set_load的值)。

Max_fanout检查的是输入端口的fanout_load最大值,

Max_capacitance检查的是输入端口load值。

两者概念不同。

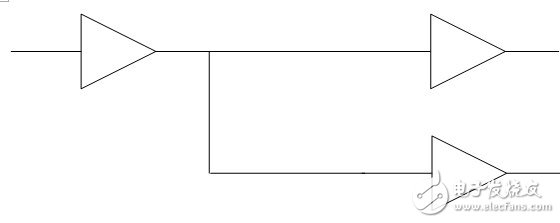

下面讲下fanout与delay,看如下一个例子:

到buffer的net延迟是2,buffer延迟是1,fanout为1时net延迟为3,每增加一个扇出,net延迟增加2.如果一个信号经过这个扇出网络后,那么延迟为:2+1+(3+(8-1)×2)=20;

如果把扇出结构优化成如下形式:

那么信号经过这个网络后,延迟为:2+1+2+1+(3+(4-1)×2)=15.

那么延迟减少了5。

接下来讲一下skew,既然知道了fanout对于delay的影响,下面看一个例子:

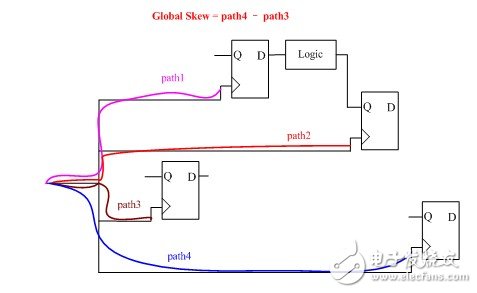

由于时钟到每个触发器的互连线长短不一样,造成信号到达clock pin的时间也不一样,触发器也不会同时翻转。Skew的定义就是最长路径减去最短路径的值。

根据时钟域以及路径关系,skew可以分为global skew,local skew,interclock skew。

Global skew是指,同一时钟域,任意路径的最大skew。

Local skew是指,同一时钟域,任意2个有逻辑关联关系的路径最大skew。

interClock skew是指,不同时钟域之间路径的最大skew

另外还有一个useful skew。本来打算在setup time和hold time中讲解。这里先大概说下

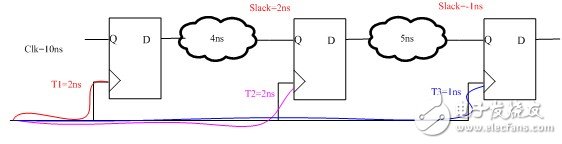

如下图:时钟周期为10ns,各时钟路径延迟如下:可以看到有一条路径的slack为-1,说明这条路径违规。可以看到与这条路径相关的skew是T3-T2=-1ns。

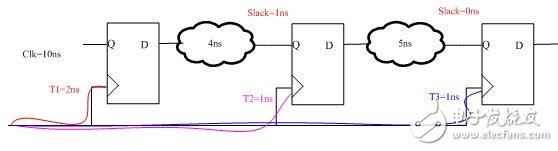

下面我们利用useful skew向前面一个slack比较充裕的路径(slack=2ns)借点time,来修正现在这条路径。如下图:

经过useful skew,修正了原来的violation。

这就是useful skew的作用,可以向前,或者向后接time来修正violation

-

中断的作用及使用方法2021-08-13 0

-

元器件在电路中的作用以及使用方法2022-01-21 0

-

示波器的使用方法2008-12-03 7409

-

万用表的使用方法2010-03-03 1491

-

电感在电路中的作用与使用方法2016-10-10 593

-

助焊膏怎么用_助焊膏的使用方法2018-02-27 54219

-

什么是参比电极_参比电极使用方法_参比电极的作用是什么2018-03-19 83603

-

光固化阻焊绿油怎么用_阻焊绿油使用方法2018-04-09 44114

-

时序分析之useful skew的作用分析2018-07-23 15987

-

示波器的使用方法(三):示波器的使用方法详解2020-12-24 2469

-

光纤收发器的作用和使用方法2021-07-27 24621

-

磁环的概念、作用及使用方法2022-04-12 34196

-

如何查看工具通过Useful skew借了多少margin呢2022-09-30 2127

-

筋膜枪的作用和使用方法2024-01-11 363

全部0条评论

快来发表一下你的评论吧 !