累加器是什么_累加器的作用及原理介绍

电子常识

描述

累加器的概念

在中央处理器中,累加器(accumulator)是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算(加法,乘法,移位等等)后就必须要把结果写回到内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

相位累加器原理

一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

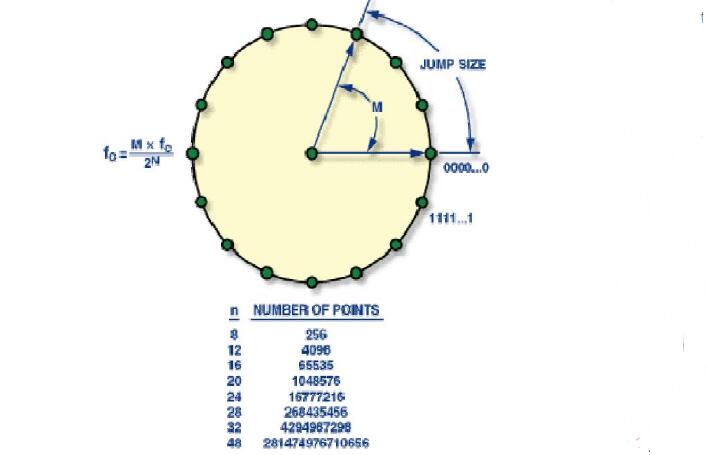

DDS正是利用了这一特点来产生正弦信号。如图2,根据DDS的频率控制字的位数N,把360°平均分成了2的N次等份。

图2.相位累加器原理

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得Fout/Fc=M/2N,就可以得到所需要的输出频率Fout,

Fout=Fc*M/2N,相位幅度转换通过相位累加器,我们已经得到了合成Fout频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。比如当DDS选择为2Vp-p的输出时,45°对应的幅度值为0.707V,这个数值以二进制的形式被送入DAC。这个相位到幅度的转换是通过查表完成的。

DAC输出代表幅度的二进制数字信号被送入DAC中,并转换成为模拟信号输出。注意DAC的位数并不影响输出频率的分辨率。输出频率的分辨率是由频率控制字的位数决定的。

累加器的作用

1、在运算器中,累加器是专门存放算术或逻辑运算的一个操作数和运算结果的寄存器。能进行加、减、读出、移位、循环移位和求补等操作。是运算器的主要部分。

2、在中央处理器CPU中,累加器(accumulator)是一种暂存器,它用来储存计算所产生的中间结果。如果没有像累加器这样的暂存器,那么在每次计算(加法,乘法,移位等等)后就必须要把结果写回到内存,然后再读回来。然而存取主内存的速度是比从数学逻辑单元(ALU)到有直接路径的累加器存取更慢。

3、在汇编语言程序中,累加器——AX是一个非常重要的寄存器,但在程序中用它来保存临时数据时,最后将其转存到其它寄存器或内存单元中,以防止在其它指令的执行过程中使其中的数据被修改,从而得到不正确的结果,为程序的调试带来不必要的麻烦。

流水线相位累加器的设计

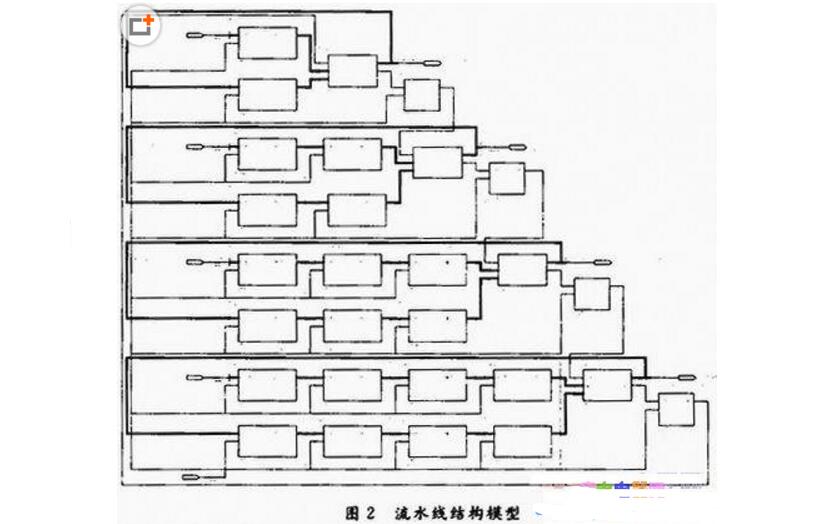

相位累加器是DDS的重要组成部分,在基准时钟控制下,它用来实现线性数字信号的逐级累加,信号范围从0加到累加器的满偏值,由此得到相应的相位数据,而相位累加器的频率就是DDS输出信号的频率。在通常的电路优化设计中,累加器模块采用超前进位加法器,这种结构克服了串行进位引起的时间滞后,很大程度上提高了加法器的运算速度,但仍有不足。为了提高DDS频率转换速度和实时性,本文提出了一种流水线结构来优化DDS的相位累加器。

FPGA的结构特点很适合采用流水线设计,以ALTEra低成本系列CycloneⅡ为例,不仅有最多达68416个逻辑单元(LE),每个LE均含有1个四输入查找表LUT、1个可编程触发器等。设计中可将1个算术操作分解成一些小规模的基本操作配置到LUT中,将进位和中间值存储在寄存器中,在下一个时钟内继续运算,整个系统只需要极少或不需要额外的资源成本。

流水线结构的基本原理是将整个电路划分为若干个流水线级,每级之间设置寄存器锁存上一级输出的数据;每一级只完成数据处理的一部分,一个时钟周期完成一级数据处理,然后在下一个时钟到来时将处理后的数据传递给下一级。第一组数据进入流水线后,经过1个时钟周期传到第二级,同时第二组数据进入第一级,数据队列依次前进。每组数据都要经过所有的流水线级后才能得到最后的计算结果,但对整个流水线而言,每个时钟都能计算出一组结果,所以平均计算一组数据只需要一个时钟周期的时间,这样就大大提高了数据处理速度。图2为在QuartusⅡ开发环境下用原理图输入法搭建的流水线相位累加器结构图。该结构由四级流水线构成,每一级流水线的输入字节为8位,分别由8位数据锁存器,8位数据全加器,1位数据锁存器构成,整个系统可实现32位输入控制字的相位累加功能。根据流水线相位累加器的工作原理,首先将32位输入控制字a由低位到高位平均分为4段,每一段为8位,分别以a[0..7]到a[24..32]来命名。将a[0..7]作为第一级的输入控制字输入到8位数据锁存器reg8中,在时钟信号clk上升沿到来之时,reg8暂存的控制字会送入到8位数据全加器adder8中与另一个加法数和进位信号进行全加运算。另一个加法数是来自本级运算结果的反馈,为保持时钟节拍的一致性,该反馈先输入到另一个reg8中暂存,然后在时钟上升沿到来之时输入到全加器进行运算;进位信号来自第四级,该信号也是先暂存在一个1位数据锁存器reg1中再输入到全加器中进行运算。

累加定时器在PLC控制程序中的应用

1、累加定时器

在系统采用的欧姆龙PLC中,TTIM(087)定时器以0.1s为单位作增量计时,其功能趋势如图2所示。

当定时器输入为ON时,TTIM(087)使PV递增;当定时器输入变OFF时,定时器停止使PV递增,但PV的值将保持;当定时器输入再次变ON时,PV将重续计时;当PV到达SV时,定时器完成标志将变ON。定时器的PV和完成标志的状态在定时器计时完成后将保持。重启定时器的方法有3种:将定时器的PV改为非零值(如通过MOV(021)指令)、使复位输入变ON、执行CNR(545)/CNRX(547)指令。定时器的精度为0~0.01s。

TIM之类的典型定时器使计数器减量计数,其PV表示到定时器计时结束前剩余的时间。而TTIM(087)的PV则表示已经过的时间,可在许多计算和显示输出中使用。

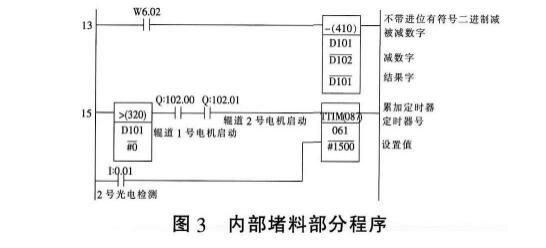

2、TTIM在内部堵料判断程序中的应用

内部堵料部分程序如图3所示,D101的数据为记录进入清洗机内的轮毂数量,累加定时器(TTIM)只有在D101大于0和1号、2号辊道电机运行情况下才开始计时。该计时值不会因为前序条件断开而复位,而是通过2号光电检测(I:0.01)检测到有轮毂来复位T61的计时值,此作用可以避免中断电流而复位计时值,起到了等同于电机光电编码器实时采集累加数值的效果。另外,通过变频器设定的辊道电机运行频率,计算出轮毂从进入到清洗完成需要的时间,赋给TTIM设置值,以此判断进入清洗机内部的轮毂在规定的时间内,有无卡在集中喷淋室内部。

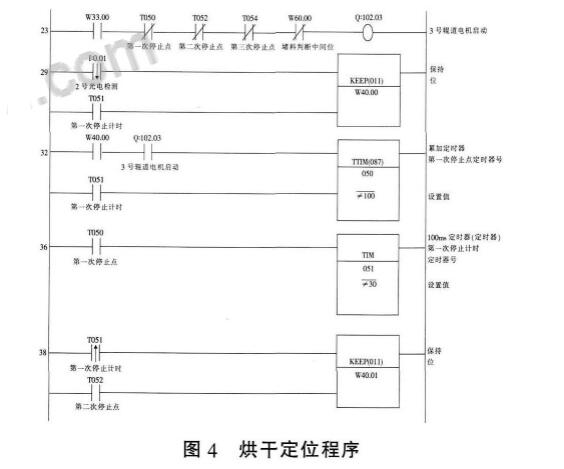

3、TTIM在烘干定位程序中的应用

烘干定位程序如图4所示,中间软继电器W33.0为自动运行中3号辊道电机的启动保持位,在没有堵料的情况下,取2号光电检测的下降沿信号置位W40.00,接通累加定时器T50,T50的设置值为3号辊道电机按照变频器设置的频率输送到第一次吹风烘干点所用的时间。T50计时完成,则判断轮毂到达第一个烘干点,停止3号辊道电机,同时接通延时导通计时器T51;T51为轮毂在第一个烘干点的停止时间,当T51计时完成复位掉T50的值及W40.00,接通第二次运行启动保持位W40.01;依次循环,完成轮毂在3个固定位置的定位烘干。在此定位过程中,累加定时器的计时值不会因后续堵料或者急停事件的发生而复位,这样可以精确地计算出轮毂在辊道上到达的位置,再次接通后继续执行剩余运行时间,把轮毂准确地送到定位烘干点。

-

累加器的简单使用和自定义累加器2020-04-02 0

-

单片机 累加器A与ACC区别2012-10-16 0

-

累加器verilog语言编程问题2015-05-23 0

-

求问大佬LabVIEW做条件累加器2017-03-03 0

-

控制累加器2019-06-04 0

-

计算机累加器有加法器功能吗,累加器是什么_累加器的作用及原理介绍 精选资料推荐2021-08-30 0

-

相位累加器原理2009-09-03 7800

-

单片机累加器作用_单片机复位电路的作用2018-04-11 11445

-

累加器是寄存器吗_寄存器、累加器、暂存器有什么区别2018-04-11 9161

-

累加器A的主要作用是什么_一文解析累加器a和acc的区别2018-04-11 21643

-

基于相位累加器的任意分频原理解析2020-11-29 4263

-

32位数字相位累加器的程序和工程文件免费下载2020-10-14 592

-

Arduino的累加器实验程序和工程文件免费下载2021-01-13 720

-

51单片机中累加器A与ACC的区别2021-11-23 3012

-

数字设计笔试Verilog手撕代码—累加器2023-06-02 1785

全部0条评论

快来发表一下你的评论吧 !