开发一款用于某单板上的特定功能模块芯片

电子说

描述

国内IC界正经历着一系列重大动作,围观者都在拭目以待着最终结果。虽是微电子专业可惜一直都在岸边等待着国内IC大潮,只是闻到潮水的咸味,还没见真正到来,出于专业的原因对于业界的这类大事总是特别留意,如果“趋势”不出意外,未来的5-10年国内自主设计的大规模IC相信会迎来大发展。

设计的IC规模越大,早期的评估就越显重要性,国内目前绝大多数IC设计都属规模较小,有能力做大规模的企业还是少得可怜,出于大环境的因素及这类小项目本身情况,对CO-DESIGN的需求还不明显。当年做ASIC封装时,由于芯片规模都较大、对上下游的相互影响也很大,因而CO-DESIGN的流程是必须且重要的,这个流程也是在自己悟出一部份再加自己写的一些小脚本补充就这样应付过来了。虽流程自己用起来觉得还算通顺,但毕竟没在统一的环境下完成,总觉得有稍稍不够完美。

前段与CADENCE技术人员交流时发现,原来已有一个成熟好用的评估工具---OrbitIO!于是自已研究了好几天还让他过来现场答疑了3次,自己再写个新的小脚本终于把这个流程完美打通。

随着国内以后IC设计规模的增大,这个CO-DESIGN方法的提前准备会给从业者带来实质的便利,相信用到这个流程而有共鸣者也许是后面几年后的事情,这与我们4年前出版的《IC封装基础与工程设计实例》书一样超前了些,没给我带来实质性的好处!

对于没有PCB及封装背景的“专家”要在早期全面评估好一个大规模的芯片:使用何种封装,如何分配管脚等等,需要与相关领域“专家”反复沟通。为了解放“专家”,这个“神器”就应运而生了,只要你会使用EXCEL就基本可以进行较为精确的评估。

1)下面以一个CASE为思路展开!

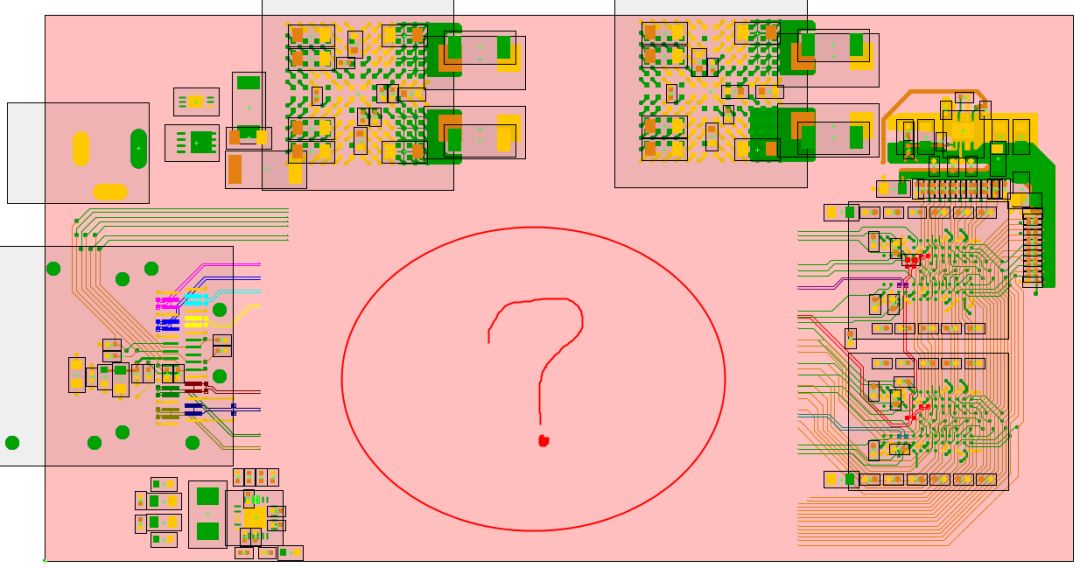

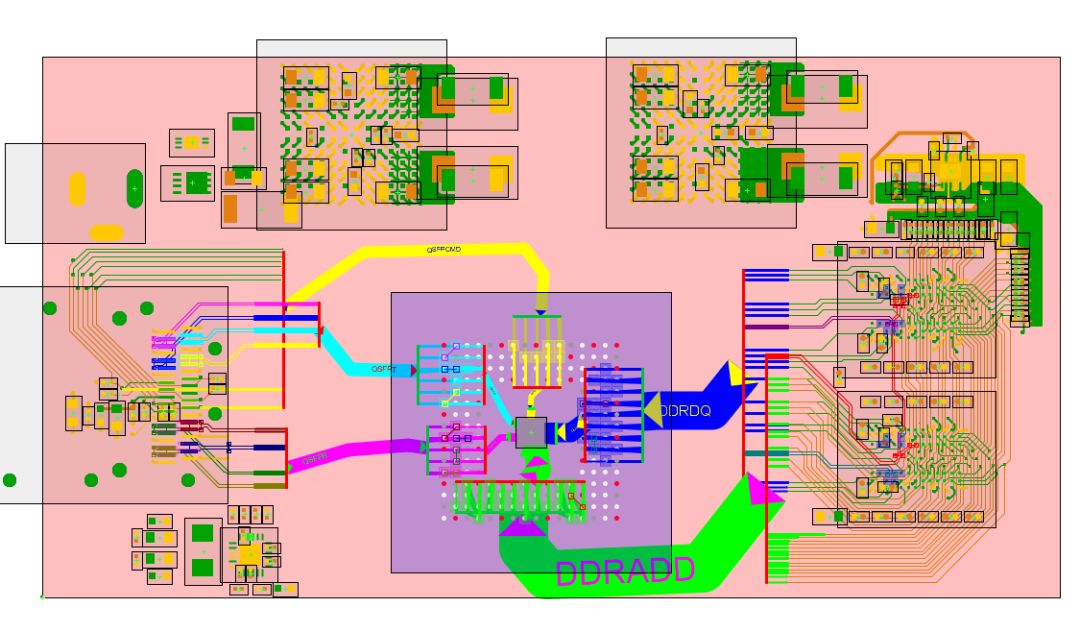

需求:开发一款用于某单板上的特定功能模块芯片,如何评估新的芯片封装用多少管脚、封装需要多大、DIESIZE需要多大及需要多少PAD呢?如下图提供了新开发的芯片与周边器件的相对位置的粗略情况。

图---(1)要开发的芯片在单板中的摆放位置

如你是一个“资深”系统架构师或是“资深”的硬件专家,接下来就有得忙了,因为评估需要输入数据,你后面的事情基本是围绕:先找后端的“专家”们商量后,再找封装的“专家”及PCB的“专家”们商量,要各领域的评估数据,这么一整2天过去了,也许结果还得再等等,急也没用,因为“部门墻”是实实在在的存在,不同部门都在“忙”着,你还真没办法!

是否想过这个评估工作在初期“专家自己”也可以独立完成呢?不用求其它的“专家”们呢?而且还可以得到一个很靠谱的评估结果。

答案是肯定的,看看下面的做法!

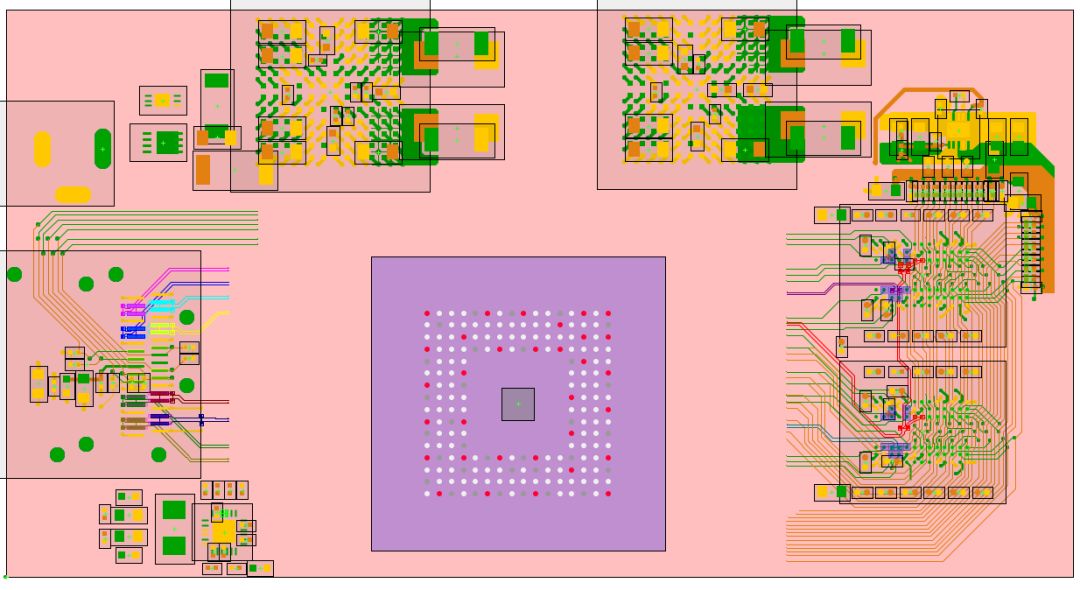

第一步就是估算接口的数量及电源、地的比例,找一个PIN数差不多的BGA封装及把一个相应数量PAD的DIE一起放在同一个界面中(这个界面就是提到的OrbitIO,一种把IC-PAKCAGE-PCB都导入到同一个平台下处理的软件)如下图。

图(2)---放入空白的BGA及DIE

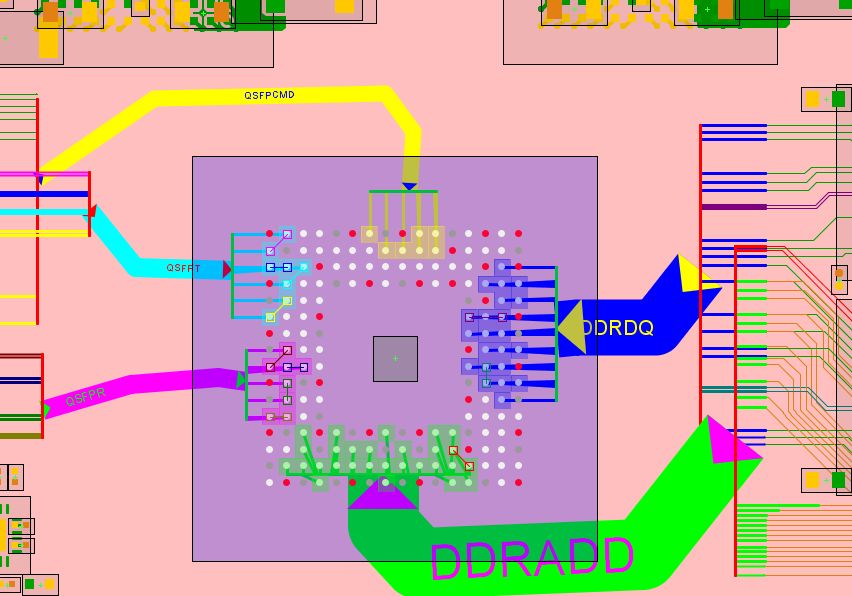

接下来“专家自己”就可以在OrbitIO平台下进行布线规划评估了,这个过程只需几分钟,从下图可见,从PCB引线到BGA封装且自动分配好管脚,很直观且高效。

图(3)---PCB周边器件往BGA空管脚上分配网络

忙完了从PCB到BGA的管脚引线,接下来就是从BGA中往DIE上的PAD分配网络,这个过程也是几分钟!效果同样是很直观、高效。

图(4)---BGA往DIE空管脚上分配网络

最后的BGA及DIE网络分配完成效果如下图,结果令人很兴奋,效果直观、结果靠谱!

图(5)---从PCB往BGA再往IC上的管脚分配网络整体效果

整个过程的评估操作只需要4分多钟,芯片越复杂越能体现这个方法与流程的优越性,平时只做PIN数较少的芯片难有机会真正体会到其中的奥秒之处了。

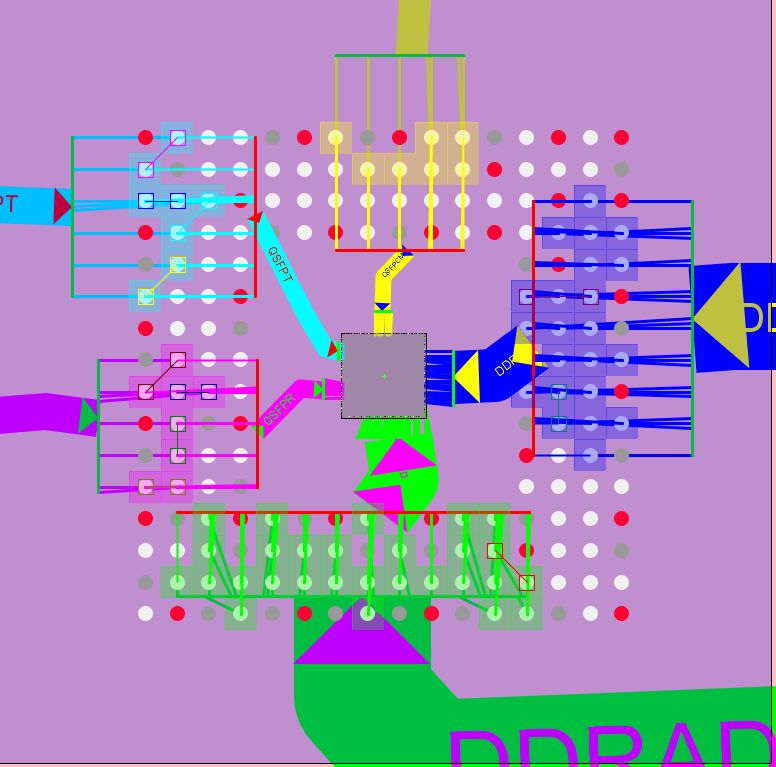

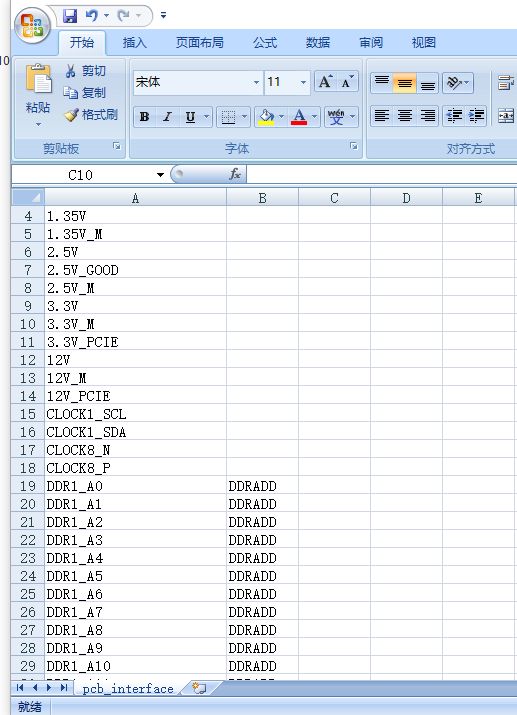

作为一个“专家”在评估复杂封装及芯片时最害怕的一件事是:需求经常在变、接口经常在变,因为这又得找其它领域的“专家”重新评估,这时使用新工具平台就很有必要了,因为OrbitIO提供的平台与使用方法太简单且直观,不需要太多的IC、封装及PCB等背景知识,只需要在EXCEL中处理下,如下图在EXCEL进行接口的分组。

图(6)---在EXCEL中对芯片的接口分组

原来几个部门不同人协调2天的活,现在只要很短时间就可以由一个人完全搞定。当然在后面的APD与PCB间的相互导入更细致的话就更完美了,有兴趣也可以与作者进一步深入交流。

-

刚学51,求推荐一款。。。2012-10-21 0

-

一款WELLS的芯片料号是2750520402015-07-01 0

-

求一款用于通信硬件的开发工具2019-10-22 0

-

几款用于白家电各功能模块的高能效方案设计2021-05-10 0

-

怎样去理解和掌握一款MCU呢2021-11-01 0

-

开发一款射频SOC蓝牙芯片2021-11-10 0

-

如何快速上手一款新的嵌入式CPU芯片2021-12-23 0

-

快速掌握一款新MCU的方法2022-02-08 0

-

NK-980IoT评测EMAC功能模块(一)2022-04-08 0

-

剪板机多轴控制系统的功能模块开发2009-10-13 704

-

SIMULINK功能模块的处理2008-06-19 2239

-

MAX+PLUSⅡ的参数化兆功能模块库的使用2009-03-13 1461

-

QuartusⅡ中宏功能模块的使用2018-04-03 634

-

开发板功能模块的简要资料总结2019-11-28 764

全部0条评论

快来发表一下你的评论吧 !