PIC32MZ EF系列处理器主要特性及开发板框图

汽车电子

描述

Microchip公司的PIC32MZ EF系列是高达250MHz的集成浮点单元(FPU),具有广泛的外设和包括局域网(CAN)的极好的连接选择,工作电压2.1V到 3.6V,DSP增强核具有四个64位累加器,单周期MAC,和IEEE 754兼容,主要用在案环境苛刻的汽车和工业应用如高分辨率音频.本文介绍了PIC32MZ EF系列主要特性,框图,处理器核MIPS32® M-Class主要特性以及PIC32MZ EF Curiosity开发板主要特性和电路图与材料清单.

The PIC32MZ EF family features high core performance up to 250 MHz, an integrated Floating-Point Unit (FPU), a wide selection of peripherals and excellent connectivity options including Controller Area Network (CAN). The Extended temp portfolio is ideal for several critical automotive and industrial applications that require reliable performance and robustness at higher temperatures.

In addition, the industrial temperature portfolio (-40°to 85℃) has been selectively expanded to offer a higher-speed variant (250 MHz/795 CoreMark®). The high-speed variant is ideal for applications like high-resolution audio that require slightly higher core performance to provide faster audio processing and streaming.

PIC32MZ EF系列主要特性:

Operating Conditions

•2.1V to 3.6V, -40℃ to +85℃, DC to 252 MHz

•2.1V to 3.6V, -40℃ to +125℃, DC to 180 MHz

Core: 252 MHz (up to 415 DMIPS) M-Class

•16 KB I-Cache, 4 KB D-Cache

•FPU for 32-bit and 64-bit floating point math

•MMU for optimum embedded OS execution

•microMIPS™ mode for up to 35% smaller code size

•DSP-enhanced core:

-Four 64-bit accumulators

-Single-cycle MAC, saturating, and fractional math

-IEEE 754-compliant

•Code-efficient (C and Assembly) architecture

Clock Management

•Programmable PLLs and oscillator clock sources

•Fail-Safe Clock Monitor (FSCM)

•Independent Watchdog Timers (WDT) and Deadman Timer (DMT)

•Fast wake-up and start-up

Power Management

•Low-power modes (Sleep and Idle)

•Integrated Power-on Reset (POR) and Brown-out Reset (BOR)

Memory Interfaces

•50 MHz External Bus Interface (EBI)

•50 MHz Serial Quad Interface (SQI)

Audio and Graphics Interfaces

•Graphics interfaces: EBI or PMP

•Audio data communication: I2S, LJ, and RJ

•Audio control interfaces: SPI and I2C

•Audio master clock: Fractional clock frequencies with USB synchronization

High-Speed (HS) Communication Interfaces (with Dedicated DMA)

•USB 2.0-compliant Hi-Speed On-The-Go (OTG) controller

•10/100 Mbps Ethernet MAC with MII and RMII interface

Security Features

•Crypto Engine with RNG for data encryption/decryption and authentication (AES, 3DES, SHA, MD5, and HMAC)

•Advanced memory protection:

-Peripheral and memory region access control

Direct Memory Access (DMA)

•Eight channels with automatic data size detection

•Programmable Cyclic Redundancy Check (CRC)

Advanced Analog Features

•12-bit ADC module:

-18 Msps with up to six Sample and Hold (S&H) circuits (five dedicated and one shared)

-Up to 48 analog inputs

-Can operate during Sleep and Idle modes

-Multiple trigger sources

-Six Digital Comparators and six Digital Filters

•Two comparators with 32 programmable voltage references

•Temperature sensor with ±2ºC accuracy

Communication Interfaces

•Two CAN modules (with dedicated DMA channels):

-2.0B Active with DeviceNet™ addressing support

•Six UART modules (25 Mbps):

-Supports up to LIN 2.1 and IrDA® protocols

•Six 4-wire SPI modules (up to 50 MHz)

•SQI configurable as an additional SPI module (50 MHz)

•Five I2C modules (up to 1 Mbaud) with SMBus support

•Parallel Master Port (PMP)

•Peripheral Pin Select (PPS) to enable function remap

Timers/Output Compare/Input Capture

•Nine 16-bit or up to four 32-bit timers/counters

•Nine Output Compare (OC) modules

•Nine Input Capture (IC) modules

•Real-Time Clock and Calendar (RTCC) module

Input/Output

•5V-tolerant pins with up to 32 mA source/sink

•Selectable open drain, pull-ups, pull-downs, and slew rate controls

•External interrupts on all I/O pins

•PPS to enable function remap

Qualification and Class B Support

•AEC-Q100 REVH (Grade 1 -40ºC to +125ºC)

•Class B Safety Library, IEC 60730 (planned)

•Back-up internal oscillator

Debugger Development Support

•In-circuit and in-application programming

•4-wire MIPS® Enhanced JTAG interface

•Unlimited software and 12 complex breakpoints

•IEEE 1149.2-compatible (JTAG) boundary scan

•Non-intrusive hardware-based instruction trace

Software and Tools Support

•C/C++ compiler with native DSP/fractional and FPU support

•MPLAB® Harmony Integrated Software Framework

•TCP/IP, USB, Graphics, and mTouch™ middleware

•MFi, Android™, and Bluetooth® audio frameworks

•RTOS Kernels: Express Logic ThreadX, FreeRTOS™, OPENRTOS®, Micriμm® μC/OS™, and SEGGER embOS®

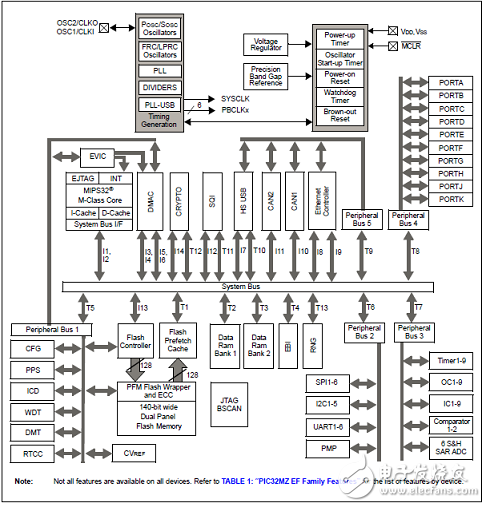

图1.PIC32MZ EF系列框图

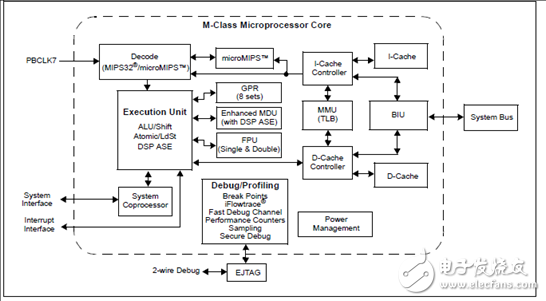

PIC32MZ EF系列处理器核MIPS32® M-Class

The MIPS32® M-Class Core is the heart of the PIC32MZ EF family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

处理器核MIPS32® M-Class主要特性:

•5-stage pipeline

•32-bit address and data paths

•MIPS32 Enhanced Architecture (Release 5):

-Multiply-accumulate and multiply-subtract instructions

-Targeted multiply instruction

-Zero/One detect instructions

-WAIT instruction

-Conditional move instructions (MOVN, MOVZ)

-Vectored interrupts

-Programmable exception vector base

-Atomic interrupt enable/disable

-GPR shadow registers to minimize latency for interrupt handlers

-Bit field manipulation instructions

-Virtual memory support

•microMIPS™ compatible instruction set:

-Improves code size density over MIPS32, while maintaining MIPS32 performance.

-Supports all MIPS32 instructions (except branch-likely instructions)

-Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

-Stack pointer implicit in instruction

-MIPS32 assembly and ABI compatible

•MMU with Translation Lookaside Buffer (TLB) mechanism:

-16 dual-entry fully associative Joint TLB

-4-entry fully associative Instruction and Data TLB

-4 KB pages

•Separate L1 data and instruction caches:

-16 KB 4-way Instruction Cache (I-Cache)

-4 KB 4-way Data Cache (D-Cache)

•Autonomous Multiply/Divide Unit (MDU):

-Maximum issue rate of one 32x32 multiply per clock

-Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (rs) sign extension-dependent)

•Power Control:

-Minimum frequency: 0 MHz

-Low-Power mode (triggered by WAIT instruction)

-Extensive use of local gated clocks

•EJTAG Debug and Instruction Trace:

-Support for single stepping

-Virtual instruction and data address/value breakpoints

-Hardware breakpoint supports both address match and address range triggering.

-Eight instruction and four data complex breakpoints

•iFlowtrace® version 2.0 support:

-Real-time instruction program counter

-Special events trace capability

-Two performance counters with 34 user-selectable countable events

-Disabled if the processor enters Debug mode

-Program Counter sampling

•Four Watch registers:

-Instruction, Data Read, Data Write options

-Address match masking options

•DSP ASE Extension:

-Native fractional format data type operations

-Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

-GPR-based shift

-Bit manipulation

-Compare-Pick

-DSP Control Access

-Indexed-Load

-Branch

-Multiplication of complex operands

-Variable bit insertion and extraction

-Virtual circular buffers

-Arithmetic saturation and overflow handling

-Zero-cycle overhead saturation and rounding operations

•Floating Point Unit (FPU):

-1985 IEEE-754 compliant Floating Point Unit

-Supports single and double precision datatypes

-2008 IEEE-754 compatibility control of NaN handling and Abs/Neg instructions

-Runs at 1:1 core/FPU clock ratio

图2.处理器核MIPS32® M-Class框图

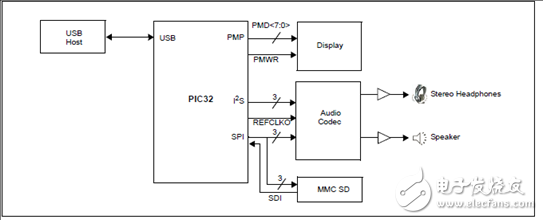

图3.PIC32MZ EF音频播放器应用框图

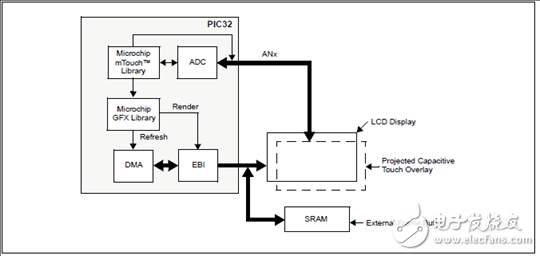

图4.投映容性触摸的PIC32MZ EF低成本无控制器(LCC)图像应用框图

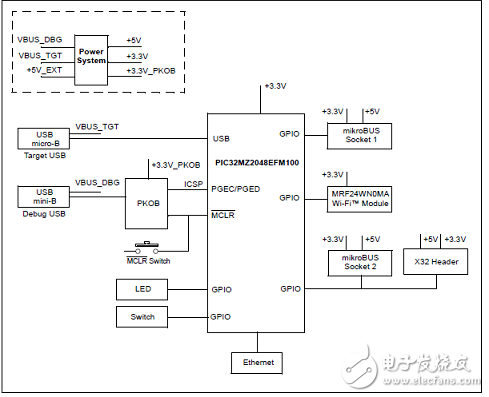

PIC32MZ EF Curiosity开发板

The PIC32MZ EF Curiosity Development Board includes an integratedprogrammer/debugger and requires no additional hardware to get started. Userscan expand functionality through MikroElectronikamikroBUS™ Click™ adapterboards, add Ethernet connectivity with the Microchip LAN8720A PHY DaughterBoard, add Wi-Fi™ connectivity using the Microchip MRF24WN0MA on-board Wi-Fimodule, and add audio input/output capability with Microchip audio daughterboards.

With or without expansion boards, the PIC32MZ EF Curiosity Development Boardprovides the freedom to develop for a variety of applications, including Internet ofThings (IoT), robotics development, and proof-of-concept designs.

The PIC32MZ EF Family Starter Kit contains the following items:

• One PIC32MZ EF Curiosity Development Board

• One on-board PIC32MZ2048EFM100 microcontroller

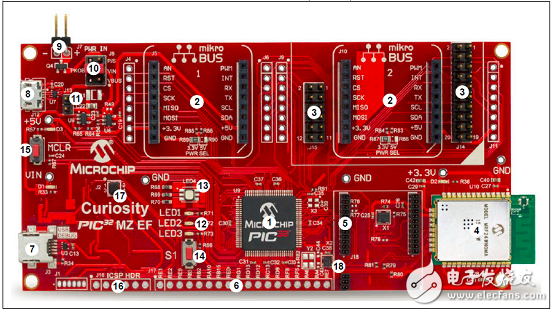

图5.PIC32MZ EF Curiosity开发板外形图

图5 PIC32MZ EF Curiosity开发板中数字对应元件:

1. PIC32MZ2048EFM100 32-bit microcontroller (U9).

2. Two mikroBUS sockets to expand functionality using MikroElectronika Clickadapter boards (J5, J10).

3. X32 header for audio I/O using Microchip audio daughter boards (J14, J15).

4. MRF24WN0MA, 2.4 GHz IEEE 802.11n compliant wireless module (U10).

5. Header for flexible Ethernet PHY options using Microchip PHY daughter boards(J18).

6. GPIO expansion header (J17).

7. Debug USB connector for programming/debugging (J3).

8. Target USB connector for PIC32 USB connectivity (Device/Host mode) (J12).

9. Header for external 5V input (J7).

10. Jumper to select power source: Debug USB connector, target USB connector and external +5V input (J8).

11. Jumper to drive VBUS in Host mode (J13).

12. Three user LEDs (LED1, LED2, and LED3).

13. RGB LED (LED4).

14. User button (S1).

15. Reset Button (MCLR).

16. ICSP header for external debugger, such as MPLAB® REAL ICE™ or MPLABICD 3 (J16).

17. Jumper to select on-board debugger or external debugger (J2).

18. 24 MHz crystal oscillator (X2).

图6.PIC32MZ EF Curiosity开发板框图

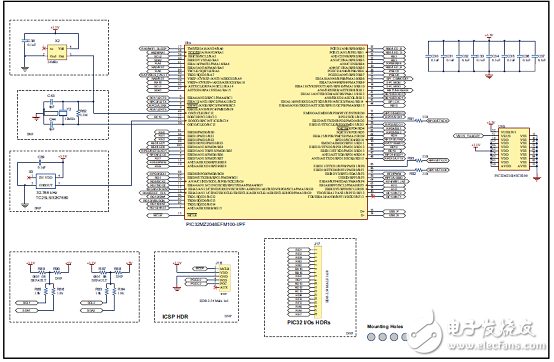

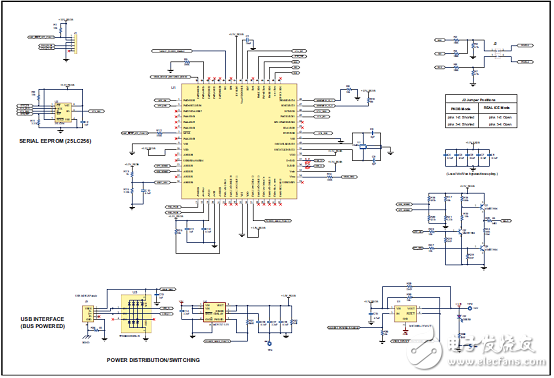

图7.PIC32MZ EF Curiosity开发板电路图(1)

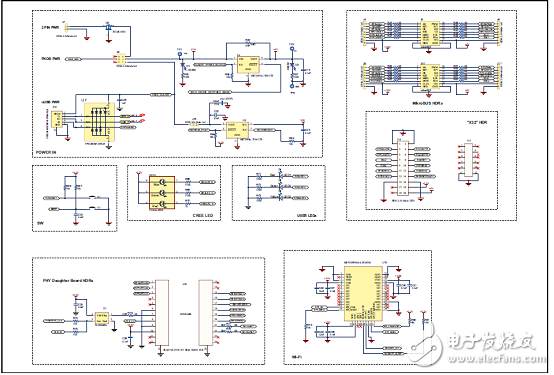

图8.PIC32MZ EF Curiosity开发板电路图(2)

图9.PIC32MZ EF Curiosity开发板电路图(3)

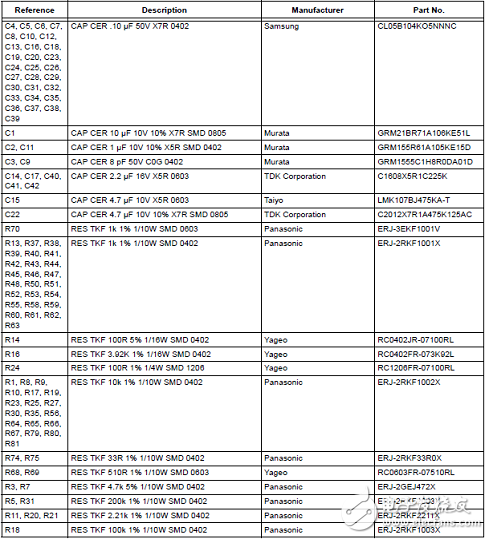

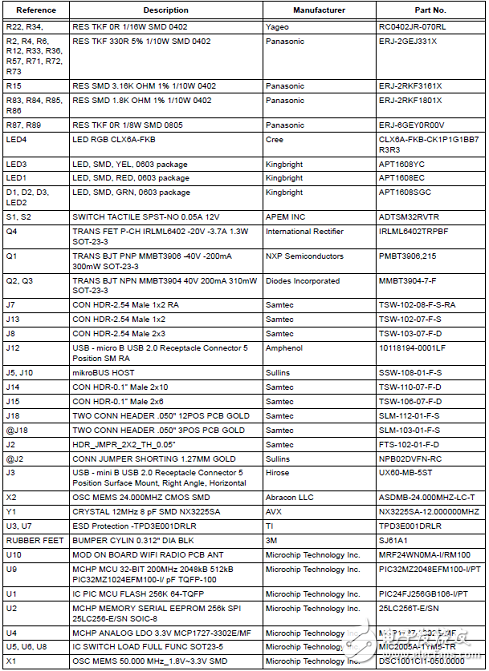

PIC32MZ EF Curiosity开发板材料清单:

-

hyt2019

2022-08-22

0 回复 举报http://house.china.com.cn/sousou/%25BF%25CD%25B7%25FE%25CE%25A2%25D0%25C5%252C%2B%25C3%25E5%25B5%25E9%25BD%25F0%25B6%25A6%25BC%25AF%25CD%25C5B2024.cN_1s.htm http://house.china.com.cn/sousou/%25D4%25DA%25CF%25DF%25BF%25CD%25B7%25FE%252C%2B%25C3%25E5%25B5%25E9%25D3%25F1%25CF%25E9B2024.cN_1s.htm http://house.china.com.cn/sousou/%25C1%25AA%25CF%25B5%25B7%25BD%25CA%25BD%252C%2B%25C3%25E5%25B5%25E9%25B9%25FB%25B2%25A9%25B6%25AB%25B7%25BD%25B6%25B7%25C5%25A3B2024.cN%252C%25C0%25F6%25BD%25AD%25B5%25E7%25CA%25D3%25CC%25A8_2s.htm http://house.china.com.cn/sousou/%25C6%25F3%25D2%25B5%252C%2B%25C5%25B7%25D1%25C7%25D3%25E9%25C0%25D6%25B3%25C7B2024.cN_90s.htm http://house.china.com.cn/sousou/%25B9%25FB%25B8%25D2%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FD%25B9%25FA%25BC%25CA%25B6%25B7%25C5%25A3B2024.cN%252C%25D5%25BF%25BD%25AD%25CE%25C0%25BC%25C6%25CE%25AF_2s.htm 收起回复

hyt2019

2022-08-22

0 回复 举报http://house.china.com.cn/sousou/%25BF%25CD%25B7%25FE%25CE%25A2%25D0%25C5%252C%2B%25C3%25E5%25B5%25E9%25BD%25F0%25B6%25A6%25BC%25AF%25CD%25C5B2024.cN_1s.htm http://house.china.com.cn/sousou/%25D4%25DA%25CF%25DF%25BF%25CD%25B7%25FE%252C%2B%25C3%25E5%25B5%25E9%25D3%25F1%25CF%25E9B2024.cN_1s.htm http://house.china.com.cn/sousou/%25C1%25AA%25CF%25B5%25B7%25BD%25CA%25BD%252C%2B%25C3%25E5%25B5%25E9%25B9%25FB%25B2%25A9%25B6%25AB%25B7%25BD%25B6%25B7%25C5%25A3B2024.cN%252C%25C0%25F6%25BD%25AD%25B5%25E7%25CA%25D3%25CC%25A8_2s.htm http://house.china.com.cn/sousou/%25C6%25F3%25D2%25B5%252C%2B%25C5%25B7%25D1%25C7%25D3%25E9%25C0%25D6%25B3%25C7B2024.cN_90s.htm http://house.china.com.cn/sousou/%25B9%25FB%25B8%25D2%252C%2B%25C3%25E5%25B5%25E9%25D3%25C0%25B2%25FD%25B9%25FA%25BC%25CA%25B6%25B7%25C5%25A3B2024.cN%252C%25D5%25BF%25BD%25AD%25CE%25C0%25BC%25C6%25CE%25AF_2s.htm 收起回复

-

使用PIC32MZ EF开发板的WiFi项目问题2018-12-12 0

-

PIC32MZ EF系列的外部存储器如何使用2018-10-26 0

-

PIC32mz ef入门套件和sd/mmc pictail是兼容的吗?2019-01-28 0

-

在PIC32MZ处理器上执行32位FFT的最佳解决方案是什么?2019-08-08 0

-

如何获得和谐v.2.03b版PIC32MZ EF启动套件S1D13517板的aria_scrolling?2019-11-07 0

-

集成的编程器/调试器PIC32 MZ EF开发板2020-04-28 0

-

闪存页擦除是否会暂停PIC32MZ EF上的CPU?2020-05-01 0

-

Microchip 32位PIC32MZ EF单片机系列喜添新成员 部分器件可支持扩展级温度范围2016-11-24 1093

-

Microchip 32位PIC32MZ EF单片机系列喜添新成员, 部分器件可支持扩展级温度范围2017-02-10 250

-

PIC32MZ嵌入连接MCU主要特性和框图分析2018-05-03 5872

-

PIC32MZ EF——带FPU的嵌入式连接系列2018-06-07 3451

-

关于PIC32MZ EF 32位—带FPU的嵌入式连接系列的特点性能及应用介绍2018-07-08 5022

-

PIC32MZ器件系列中的 1 级(L1)CPU 缓存实现2021-06-18 1951

-

基于PIC32MZ EF MCU的驱动视频监控系统2022-08-30 832

-

Curiosity PIC32MZ EF 2.0开发板用户指南2023-09-21 112

全部0条评论

快来发表一下你的评论吧 !