基于汽车市场的IC测试解决方案

电子说

描述

乘用车中的电子部分持续快速增长,驱动这一现象的主要因素是乘用车中集成了各种高级安全功能。整 个行业向全自动驾驶汽车的转变有望进一步增加此类安全功能的数量,进而增加电子部分的比重。最近 有报告表明,高端汽车中目前集成了成百上千的半导体器件。另外,这些元器件的复杂性也是与日俱 增。事实上,引领先进半导体前沿市场的正是执行人工智能算法所需的芯片,而且这些算法可以管理新 兴的自动驾驶功能。这类安全相关的器件必须尽可能满足最高的质量和可靠性要求,这一点至关重要。 这些要求已在 ISO 26262 标准中正式提出,世界各地的汽车制造商和供应商也已纷纷采用这一标准。这是 一项综合标准,涵盖软件和硬件的完整生命周期,从设计一直到测试和实际运行。为帮助企业满足 ISO 26262 标准强制要求的质量和可靠性指标,Mentor Tessent 产品系列提供了一套全面的测试解决方案。

通过在线自测试确保系统可靠性

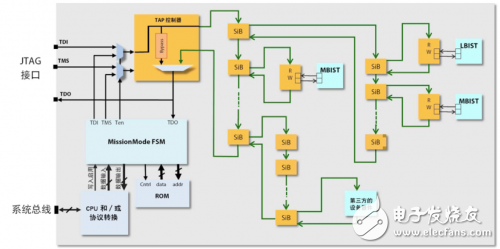

要确保汽车电子的可靠性,其中一种方法便是在功能运转期间执行定期测试。借助 Tessent MissionMode 架 构,可以实现对所有片上测试资源的低延迟系统级访问,以便进行在线测试和诊断。图 1 显示的即为该架 构。使用基于 IEEE 1687 (IJTAG) [1,2] 的网络可以访问在整个设计流程中分发的所有测试 IP。测试 IP 可能包 括任意 Tessent DFT BIST 功能,或任何符合 IJTAG 标准的第三方 IP。利用 SIB(扫描插入位)交换机的层次 化网络,即可与测试 IP 进行多面而又高效的通信。IEEE 1149.1 TAP(测试点端口)可提供对 IJTAG 网络的 外部访问,主要在制造测试环境中使用。居于此架构中心的是 Tessent MissionMode 控制器,它能接管 TAP 信号,并将任何测试或诊断命令驱动至 IJTAG 网络中的任意和所有测试 IP。

图 1:基于 IJTAG 的 Tessent MissionMode 架构。

MissionMode 控制器可配置为在两种不同模式下工作。在 CPU 访问模式下,该控制器支持与 CPU 总线之间 的双向并行读写操作。该控制器可根据需要执行并行到串行和串行到并行数据转换,以便在 CPU 总线与 IJTAG 网络之间传输信息。此模式支持图 所示的模块级或系统级通信架构。服务处理器可通过任意汽车 总线,例如 CAN(控制器局域网)或 I2C(内置集成芯片),访问各个 MissionMode 控制器,进而访问任 意片上测试 IP。在直接存储器访问 (DMA) 模式下,MissionMode 控制器可读取在非易失性存储器中预载的 命令数据。在系统操作期间,根据需要,可以存储多种测试序列,而且可以以任何顺序不限次数的重新 获得这些测试序列。

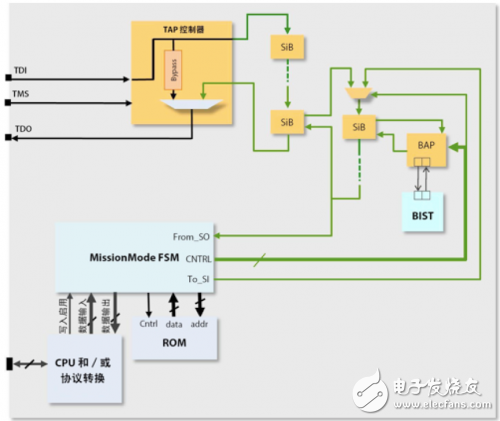

除了通过 TAP 访问整个芯片 IJTAG 网络 之外,还可配置一个或多个 MissionMode 控制器直接与单个或一小组测试 IP 通 信(参见图 3)。这样做的好处是可以 缩短通信延迟,而这对某些测试而 言至关重要。非破坏性存储器 BIST 便 是一个重要示例 [3]。在这种形式的测 试中,存储器 BIST 控制器会使用一 系列的短事务序列对存储器进行测 试,我们通常将此成为猝发。猝发 通常仅持续若干时钟周期(可能 20 到30 个),并且每次针对不同的存储 器位置。因此可通过大量较短的存储 器 BIST 会话对整个存储器进行测试。 这一方法是非破坏性的,因为在每个 猝发期间,猝发所修改的存储器位置 均会由 MBIST 控制器进行保存和恢复。 由于猝发仅在仲裁逻辑确定存储器

图 3:Tessent MissionMode 直接本地访问。

可用时才会启动,功能性能并不会受到严重影响。如果存储器仅在上电时进行测试,则可使用更传统的 破坏性存储器 BIST 测试。这种情况下,通常就不会存在延迟问题,单个与 TAP 接口的 MissionMode 控制 器便足够了。

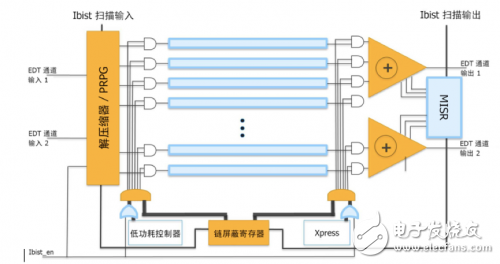

逻辑 BIST 是另一种常见的系统内测试形式,通过 MissionMode 控制器可以访问该测试。该测试解决方案 涉及在片上生成随机测试向量,然后将其应用于扫描链。最近,我们对此方法进行了改进,提供了一种 可集成 ATPG 压缩和逻辑 BIST 的混合测试解决方案(参见图 4)。汽车设备内通常同时需要这两种解决方 案;ATPG 压缩用于高质量的制造测试,逻辑 BIST 则用于上电测试和系统内测试。

图 4:混合 ATPG 压缩和逻辑 BIST 架构。

结合使用这两种解决方案将可获得明显的优势。特别是,由于这两种解决方案使用几乎相同的片上 DFT 资 源,因此可以减少面积开销。例如,二者都使用扫描链和相关的测试时钟。两种解决方案的主要区别在 于将测试数据馈送到扫描链以及处理来自扫描链的测试响应数据的片上逻辑。然而,逻辑间也存在相似 性,所以两种解决方案的逻辑可以高效地合并以同时支持这两种方法。

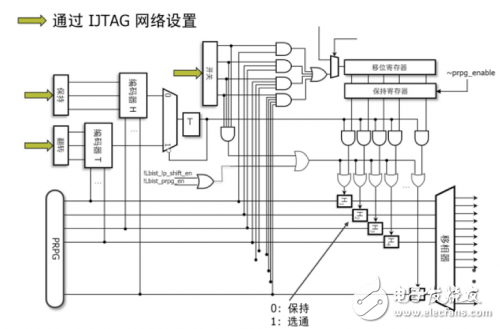

在功能运转期间定期应用逻辑 BIST 的一个重要方面是限制功耗,以便最大限度地降低对被测系统其他部 分造成的影响。在逻辑 BIST 操作期间,通过最大限度减少随机测试向量和响应的扫描加载和卸载期间的 翻转活动,可以实现功耗的降低。图 5 所示的架构通过定期将随机数据位替换为常量值而减少了扫描翻转 活动 [4]。该结构支持可编程电路的翻转率色设定,在小幅增加测试向量和保持相同测试覆盖率的同时,可 以降低电路的翻转率。

图 5:低功耗逻辑 BIST 架构。

-

中国无人驾驶汽车市场将具有更大优势2016-06-13 0

-

我看2017新能源乘用车市场2017-02-08 0

-

【技术干货】氮化镓IC如何改变电动汽车市场2018-07-19 0

-

如何选用FPGA和完整的IP解决方案优化其电气架构?2019-08-27 0

-

如何用FPGA和完整的IP解决方案优化汽车电气架构?2019-09-03 0

-

Actel FPGA为汽车市场带来的优势有哪些?2021-05-19 0

-

大致了解NXP汽车电机控制的解决方案2021-09-08 0

-

我爱方案网:小米汽车又获充电新专利,未来万亿电动汽车市场无悬念2022-06-27 0

-

DLP技术在汽车市场的解决方案与应用介绍2018-08-22 3382

-

汽车市场是蓝牙技术的绝佳舞台2019-08-04 3613

-

2021年3月我国汽车市场产销数据2021-04-20 3277

-

智能汽车市场对DRAM和NAND的解决方案2022-10-18 844

-

适用于汽车市场的IC测试解决方案2023-03-30 512

-

2024年新能源汽车市场的十大预测2024-01-03 936

全部0条评论

快来发表一下你的评论吧 !