FPGA设计之时序逻辑的模板

可编程逻辑

1339人已加入

描述

FPGA工程师都知道,Verilog代码绝大部分都是always语句,结构基本上都是一致的,为了减少重复性的工作,让工程师专注于设计实现,明德扬精心制作了常用模板,只要你安装好明德扬提供的GVIM,就能使用这些模板了。

1.时序逻辑的模板

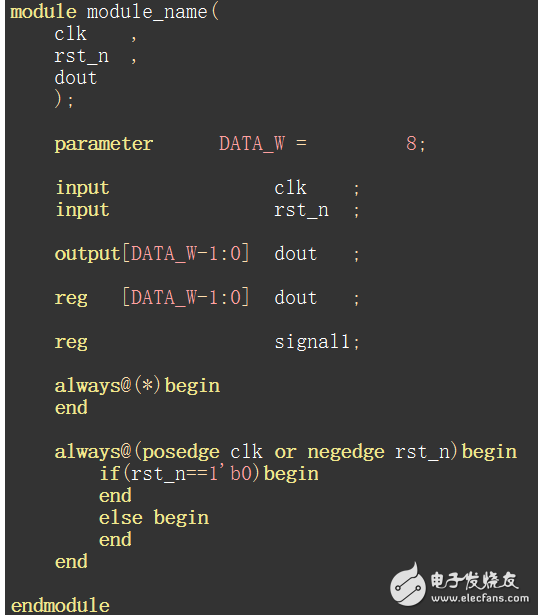

在GVIM输入“Module”并回车,如下图所示

就能得到下面的时序逻辑的模板。

模块的模板包括了输入输出信号列表、信号定义,组合逻辑和时序逻辑等,这是一个模块常用的组件。学员只需要理解各个部分的意义,按要求来填空就可以,完全没有必要去记住。我看很多学员刚开始学习时,花费大量的时间去记住、背熟模块,这是没有意义的。

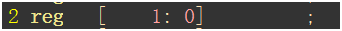

2.输入“Reg”并回车。

就能得到单比特的reg信号定义

3.输入“Reg2”并回车

就能得到2比特的reg信号定义

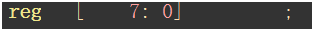

4.输入“Reg8”并回车

就能得到8比特的reg信号定义

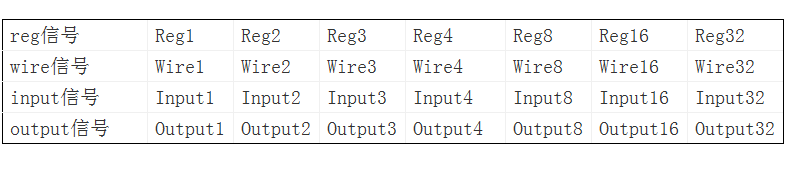

类似的快捷命令有:

要使用上面快捷命令,需要明德扬的配置文件,欢迎关注明德扬公众号“fpga520”,或群97925396索取。口号:多用模板,减少记忆,专注设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

fpga时序逻辑电路的分析和设计2012-06-20 0

-

FPGA重要设计思想及工程应用之时序及同步设计2016-04-24 0

-

明德扬FPGA设计模板分享(1)2017-04-26 0

-

FPGA重要设计思想及工程应用之时序及同2010-02-09 652

-

时序逻辑电路的分析与设计2016-09-02 971

-

数字电路基础教程之时序逻辑电路的详细资料概述2018-10-17 1108

-

FPGA之时序电路的理解2018-11-24 3214

-

数字电路教程之时序逻辑电路课件的详细资料免费下载2018-12-28 976

-

数字设计FPGA应用:时序逻辑电路FPGA的实现2019-12-05 2575

-

模拟电路教程之时序逻辑电路的课件资料免费下载2020-06-22 736

-

FPGA案例之时序路径与时序模型解析2020-11-17 2805

-

FPGA设计之时序约束四大步骤2022-03-16 3280

-

FPGA设计之时序约束2022-03-18 1350

-

FPGA中何时用组合逻辑或时序逻辑2023-03-21 513

全部0条评论

快来发表一下你的评论吧 !