PCB 设计之Expedition 等长设置

EDA/IC设计

描述

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB 的自动调线功能,将有利于提高设计效率,特别是对于具有较多走线长度要求的设计。

在Expedition pcb 中设置等长的方法有:

Matched Group Length

Considered “Electrical Nets”

— Nets with Series Resistor

Matched Length Rules by Pin to Pin

Matched Length Rules by Considered Wire-Bond Length in Package

Multiple Matched Length Rules within Bus

一、Matched Length Rules by Considered Wire-Bond Length in Package

在当前PCB 设计中,对于许多高速芯片之间的互连必须将芯片的IO PAD 到封装Pin 之间的长度(封装级互连长度)也考虑在内,从而在一些设计当中要进行IO PAD 到IO PAD 总互连长度的匹配。通常芯片厂家会提供封装级互连长度的参数,由于许多PCB 设计工具不支持将封装长度直接加入到设计中,因此PCB设计者不得不参照IC 厂家提供的布线长度数据表进行总互连长度的计算。这样的调线过程比较费时。Mentor 的Expedition Pcb 支持将封装级互连长度直接输入到设计中,从而设计者在调线中不再需要根据封装级互连长度数据表进行相关互连的长度调整计算,通过CES 的等长约束,可以让Expedition 进行自动调线。下面通过一个简单的例子来说明在 ExpeditionPcb 中设置Package Pin 长度进行调线的过程。

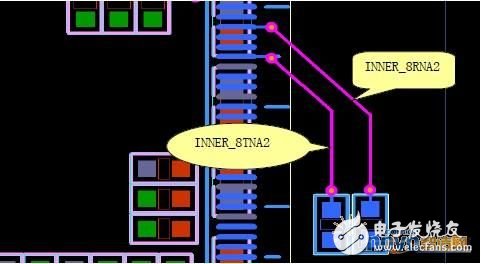

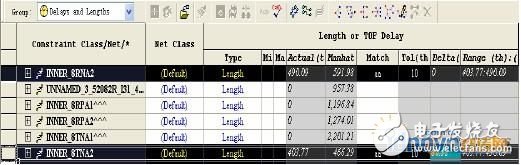

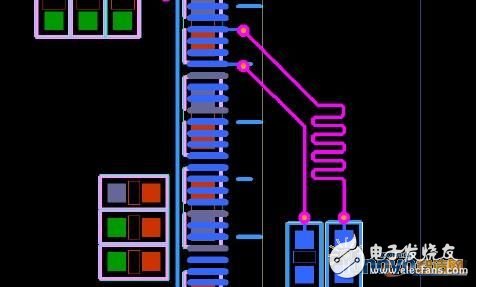

对于图1A 的PCB,具有两个网络INNER_8RNA2 和INNER_8TNA2。我们在CES 中设置INNER_8RNA2 和INNER_8TNA2 等长,公差为10mil,见图1B。

图1A 具有两个网络的PCB

图1B CES 中等长设置

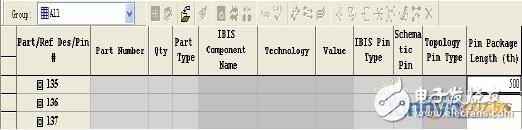

假定INNER_8TNA2 网络所连接的芯片LXT358 其封装级互连长度为500mil。通常在Allegro 中,设计者不得不将INNER_8TNA2 在PCB 走线长度调整为INNER_8RNA2 在PCB 上走线长度减500mil。而在Expedition 中,不需要如此麻烦,设计者在CES 中找到Parts 表,在LXT358 器件的Pin Package Length 下将INNER_8TNA2 网络所对应的Pin 脚的Pin Package Length 设置500mil,ExpeditionPCB 在布线和调线中会自动地将该长度计入IO PAD 到IO PAD 总互连长度中。如图2A。

INNER_8RNA2

INNER_8TNA2

图2A Pin Pacakge Length 在CES 中的添加

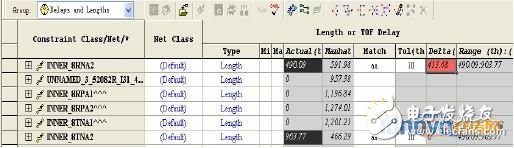

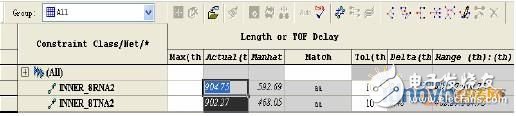

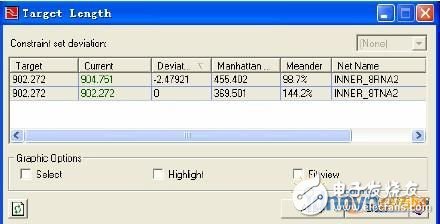

添加 Pin Package Length 后,更新数据,Pin Package Length 值在CES 的等长约束中就有体现。如图2B。与图1B 对比更清晰。

图2B Pin Package Lenth 在约束中体现

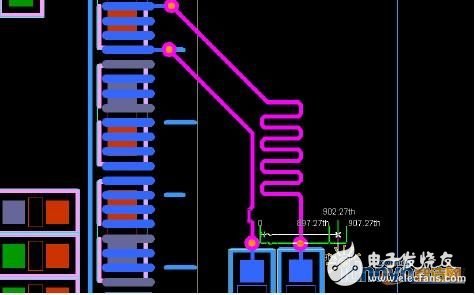

图2C 考虑封装级互连长度的调线结果

以上就是考虑封装级互连长度的具体设置过程。在这里要注意一点就是自动绕线后手工检查的时候在CES 和Target Length 报告中以及标尺中显示的是计入封装级互连长度后的总互连长度(见图3A、图3B 和图3C)。

图3A CES

图3B Target Length 报告

图3C 标尺中的显示

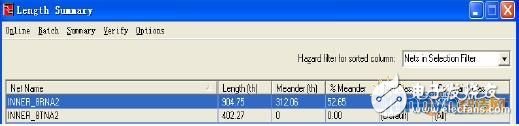

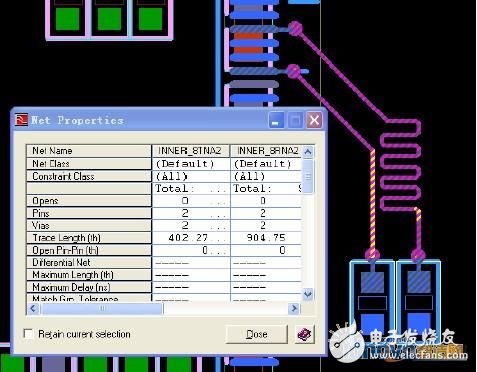

但是从图3D 和图3E 可知,在属性和Length Summery 报告中,显示的长度只限于PCB 上走线的长度,并没有计入封装级互连长度。

图3D 属性

图3E Length Summery 报告

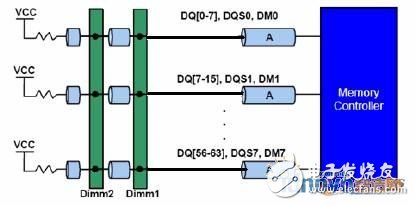

二、Multiple Matched Length Rules within Bus

当今要求满足不同时序要求的PCB 日益增多。要实现一些要求复杂的等长必须采用延迟公式来表示。延迟公式用来设定不同的pin pairs 或网络满足比较复杂的布线要求,它可以使用变量和常量来定义。并且一个网络或者pin pairs 允许有多个公式,公式之间可以用#、:、《、》号分开。这样设置起来就比较方便。下面通过一个比较常见的例子(如图4A)来详细介绍使用延迟公式来设置等长的具体设置过程。

图4A 使用延迟公式来设置等长例子

具体要求:

(1)每8 位一组,长度要求匹配在+/-10th

(2)在不同的组之间,长度要求匹配在+/-100th

要满足第一个要求只要将8 个网络设置成一个Match 组即可,但是要同时满足两个要求使用Match 组不可能达到目的。这种情况下只能通过Formula 来实现。

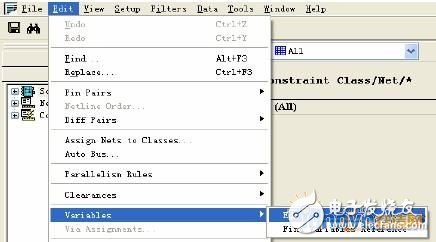

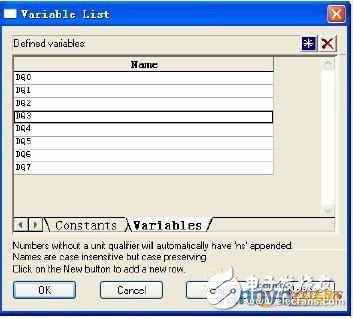

首先给每一组创建一个变数:DQ0-DQ7.如图4B 和图4C

图4B 每一组创建一个变数1

图4C 每一组创建一个变数2

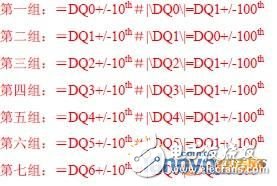

其次要满足第一个要求只要在每一组的网络后面输入公式:“=DQ*+/-10th ”(*=0~7)即可。要同时满足第二个要求只要在公式后面输入#(#表示的是同时满足的意思,一个网络或PIN PAIRS 要同时满足很多等长要求的话用#,#后面必须要有它自己的网络或者pin pairs 名),然后输入“=DQ*+/-100th ”(*=0~7,但不能与前一个公式中的*的内容相同)。

最后的公式如下:

三、结束语

MENTOR 公司的Expedition PCB 布线工具为PCB 设计工程师提供了一个功能强大的PCB 设计手段,通过各种等长设置,可以设计出符合各种要求的信号时序和信号完整性,从而提高单板和系统的工作稳定性,降低开发风险和开发成本,而当今要求满足不同时序要求的PCB 日益增多,靠手工绕线完全满足不了实际的要求且耗时较长,通过软件的自动绕线在就大大缩短了设计周期。本文简单介绍了两中有特殊时序要求的等长设置方法,由于理解和掌握程度不深,错误之处在所难免。

- 相关推荐

- PCB设计

- EXPEDITION

-

mentor expedition PCB 文件谁有呢?还有安装与破解,求分享2013-03-02 0

-

Mentor Expedition PCB 2004/2005 设计复用2014-10-28 0

-

Mentor Expedition PCB中文版教程2019-04-17 0

-

Mentor Expedition PCB Job Flow2008-05-11 1082

-

EXPEDITION PCB使用体会2010-06-07 795

-

EXPEDITION在复杂PCB项目设计中的应用2010-06-07 635

-

Expedition PCB 设置等长的方法2010-07-04 910

-

mentor expedition的功能说明2008-03-22 6634

-

PowerPCB转Mentor Expedition教程2009-04-15 1639

-

教您在Allegro中设置走线等长进阶2010-06-28 27680

-

Mentor Expedition PCB中文教程2011-05-10 1833

-

allegro_差分线等长设置2016-02-22 2034

-

Allegro PCB设计时等长设置的一些方法与技巧解析2018-11-27 1905

-

Mentor Expedition PCB指导手册下载2021-05-08 1425

-

PCB设计中常见的走线等长要求2023-11-24 963

全部0条评论

快来发表一下你的评论吧 !