资料下载

×

TMS320C6678存储器访问性能详细中文资料

消耗积分:0 |

格式:rar |

大小:1.11 MB |

2018-04-26

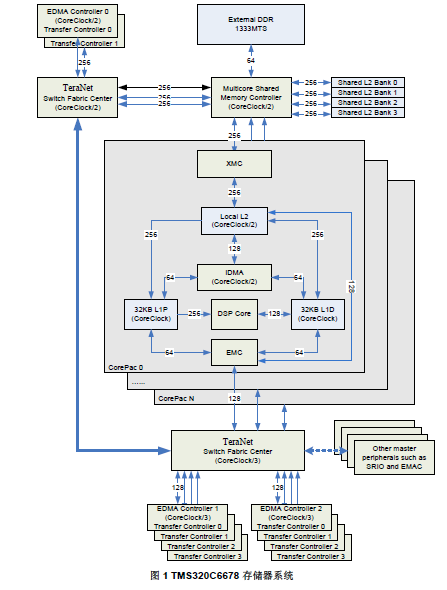

TMS320C6678 有8 个C66x 核,典型速度是1GHz,每个核有 32KB L1D SRAM,32KBL1P SRAM 和512KB LL2 SRAM;所有DSP 核共享4MB SL2 SRAM。一个64-bit1333MTS DDR3 SDRAM接口可以支持8GB 外部扩展存储器。

存储器访问性能对DSP 上运行的软件是非常关键的。在C6678 DSP 上,所有的主模块,包括多个DSP 核和多个DMA 都可以访问所有的存储器。

每个DSP 核每个时钟周期都可以执行最多128 bits 的load 或store 操作。在1GHz 的时钟频率下,DSP 核访问L1D SRAM的带宽可以达到16GB/S。

DSP 的内部总线交换网络,TeraNet,提供了C66x 核(包括其本地存储器),外部存储器,EDMA 控制器,和片上外设之间的互连总共有10 个EDMA 传输控制器可以被配置起来同时执行任意存储器之间的数据传输。

本文为设计人员提供存储器访问性能评估的基本信息;提供各种操作条件下的性能测试数据;还探讨了影响存储器访问性能的一些因素。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章