以i.MX6UL为例为大家介绍上电时序的设计

电子说

描述

为确保芯片能可靠的工作,硬件电源设计要满足芯片手册的上电时序、掉电时序,否则在产品使用时可能会出现电流过大,启动异常,甚至损坏处理器。本文以i.MX6UL为例为大家介绍上电时序的设计。

一、i.MX6UL上下电时序要求

上电时序:

1、VDD_SNVS_IN 必须单独或与VDD_HIGH_IN 一起(短接)上电,在这之后其他电源才能上电。

2、如果使用纽扣电池为VDD_SNVS_IN 供电,请确保在开启任何其他电源之前将其连接。

3、应在VDD_SOC_IN 之前开启VDD_HIGH_IN。

掉电时序:

1、VDD_SNVS_IN 必须单独或与VDD_HIGH_IN 一起(短接)下电,在这之前其他电源必须全部完成下电。

2、如果使用纽扣电池为VDD_SNVS_IN 供电,请确保在关闭任何其他电源之后将其移除。

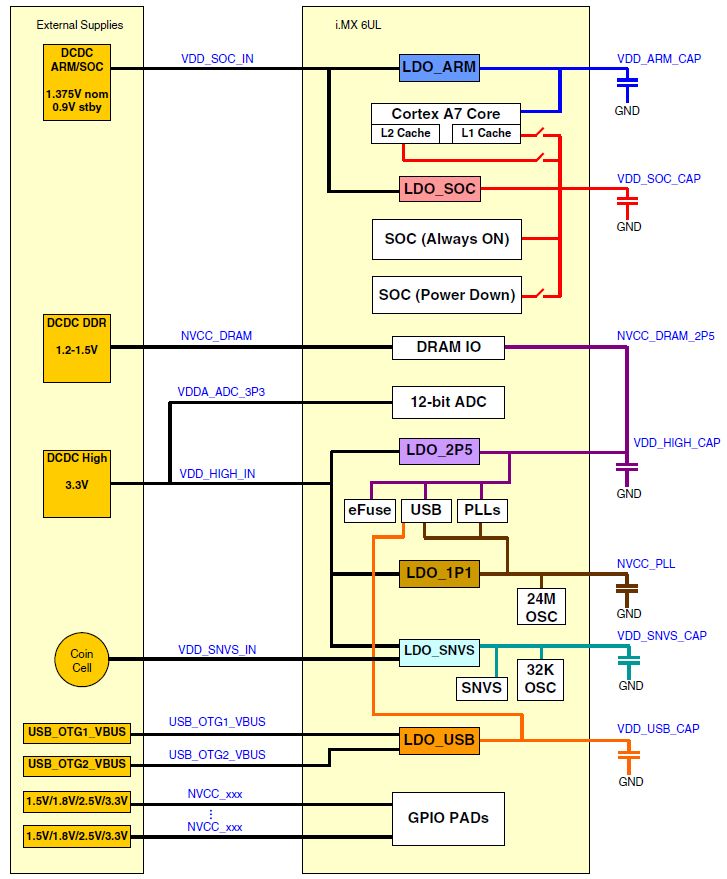

二、i.MX6UL电源管理单元-PMU

三、要点分析

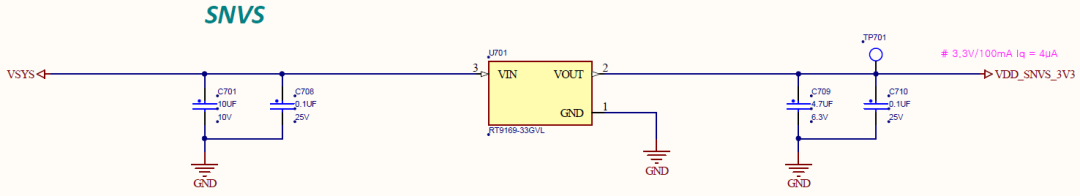

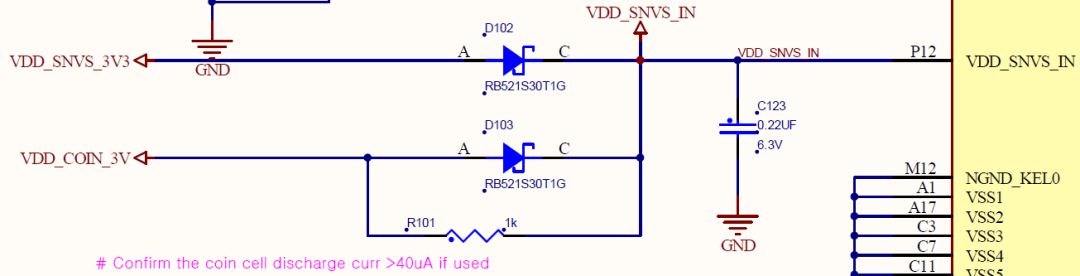

从i.MX6UL电源管理单元图可知,最先供电的VDD_SNVS_IN管脚是作为内部LDO_SNVS的输入,其输出电压VDD_SNVS_CAP是向SNVS模块及实时时钟模块OSC32K供电。 如需在掉电情况下保持RTC,则VDD_SNVS_IN需单独进行供电,否则可以与VDD_HIGH_IN接一起。VDD_SNVS_IN设计中可预留纽扣电池方案,以满足掉电保持实时时钟的应用需求,但如果使用纽扣电池为VDD_SNVS_IN 供电,请确保在开启任何其他电源之前将其连接。

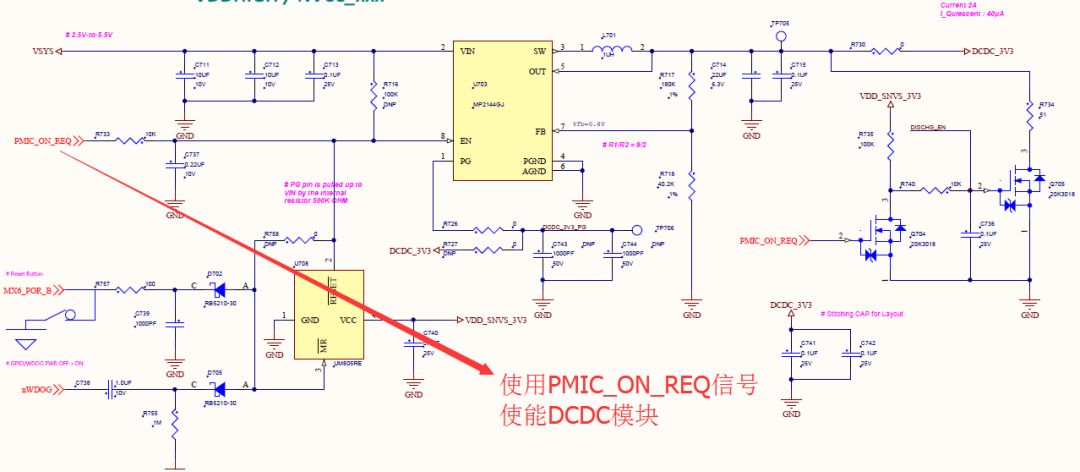

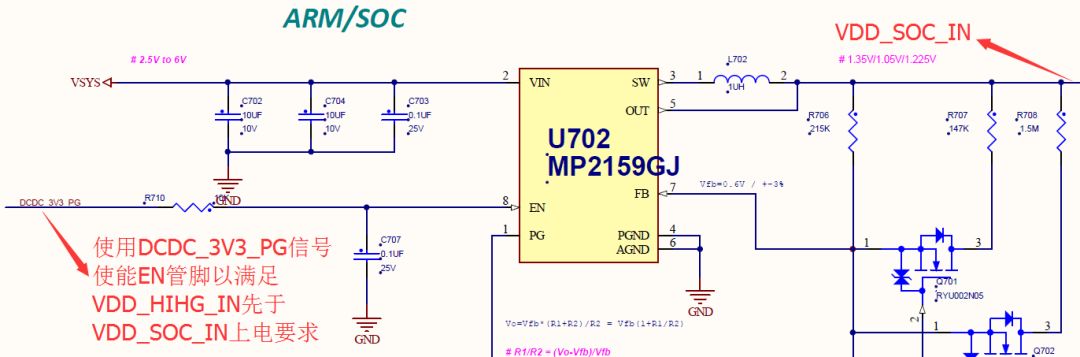

由前面上电时序可知,VDD_HIGH_IN可与VDD_SNVS_IN电源一起最先上电。在系统需要掉电保持实时时钟的情况下,由于VDD_HIGH_IN功耗较高,因此在保持实时时钟的情况下,需要将该两路电源需要分开处理。可利用SNVS电源域下的控制信号PMIC_ON_REQ使能后上电的电源模块,以达到上电的时序要求,如下图所示。

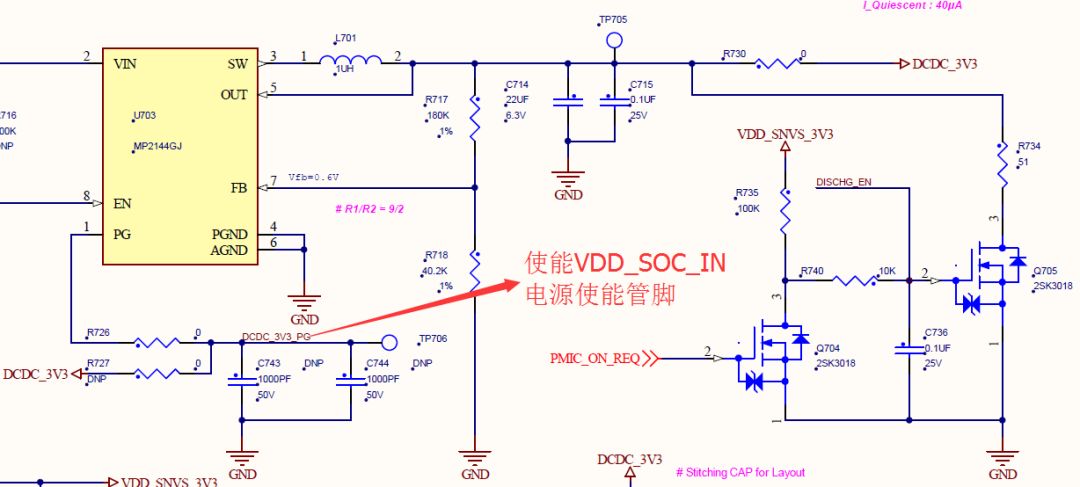

由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN,因此在电路设计中,可使用VDD_HIGH_IN电源芯片的控制信号使能VDD_SOC_IN的电源,如下图所示为使用VDD_HIGH_IN供电芯片的PG信号使能VDD_SOC_IN供电芯片的使能管脚。

使用DCDC_3V3_PG控制VDD_SOC_IN电源使能管脚以满足VDD_HIGH_IN上电先于VDD_SOC_IN的要求,如下图所示。

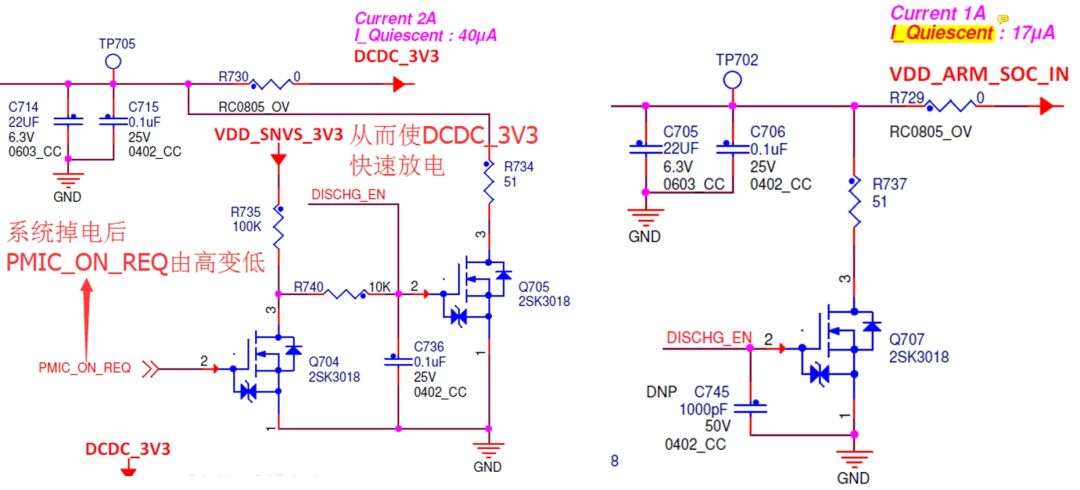

根据掉电时序要求,掉电优先顺序只要满足 VDD_SNVS_IN最后掉电即可。设计中加入相应的可控掉电电路,可使后级的滤波电容快速放电从而实现掉电的先后顺序,如下图所示为DCDC_3V3的掉电电路,DCDC_3V3为VDD_HIGH_IN供电。工作原理:系统掉电后,PMIC_ON_REQ由高电平变为低电平,从而使DISCHG_EN信号变为高电平,从而使DCDC_3V3电流通过电阻R734及MOS管Q705导通到GND, VDD_SOC_IN电压通过DISCHG_EN信号控制MOS管Q707快速掉电,如下图所示。

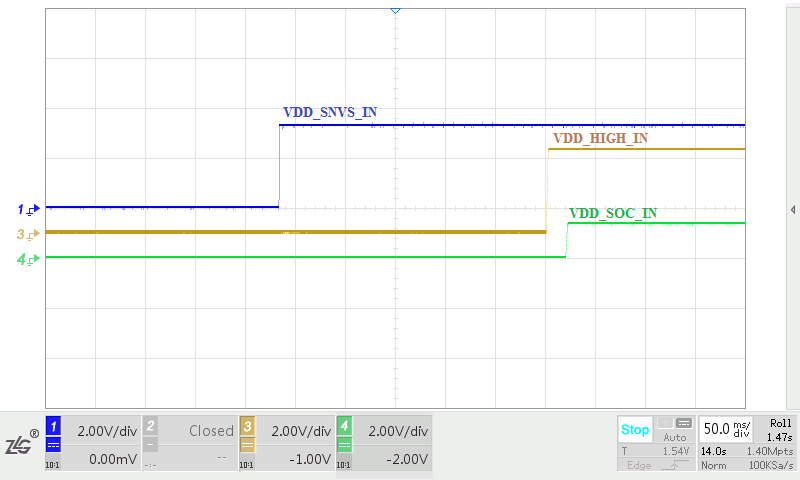

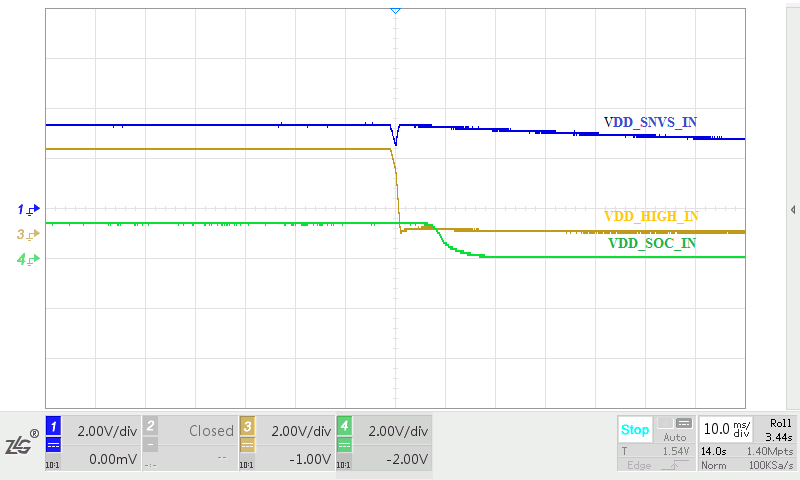

i.MX6UL上电时序波形如下图所示,其中VDD_SOC_IN为内核电压-1.35V。

i.MX6UL掉电时序波形如下图所示。

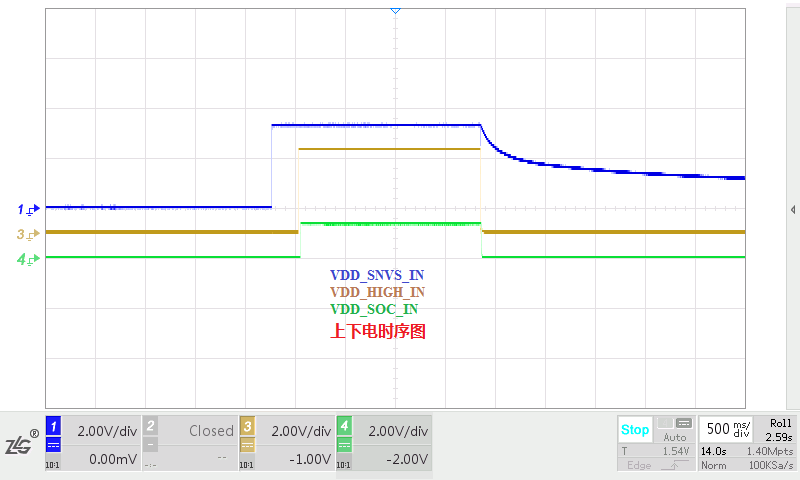

上下电时序完整波形图如下图所示。

四、结束语

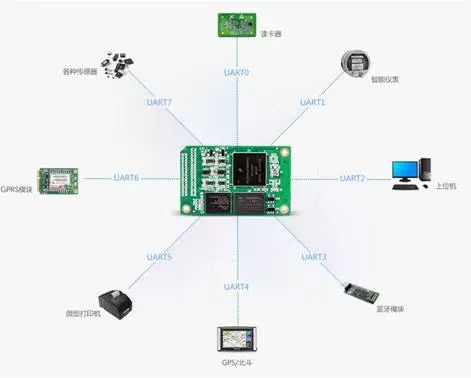

M6G2C采用i.MX6UL处理器,满足芯片手册严格的上下电时序,是一款工业控制核心板,采用 Freescale Cortex-A7 528MHz主频的处理器,以先进的电源管理架构带来更低功耗。标配8路UART、2路USB OTG、2路CAN-Bus、2路以太网等接口;标配128/256MB DDR3和128/256MB NAND Flash、硬件看门狗;通过严格EMC和高低温测试,确保核心板在严酷的环境下稳定工作。

-

i.mx6ul简要介绍2016-04-12 0

-

NXP I.MX6UL工业级核心板带屏开发板免费试用2016-12-19 0

-

【TQi.MX6UL试用申请】基于i.MX6UL的智能网关2017-06-16 0

-

【盈鹏飞I.MX6UL工控开发板试用体验】串口终端使用2017-08-07 0

-

为什么这么高评价i.MX6UL?了解TQIMX6UL多接口工业级开发板吗?2017-08-09 0

-

NXP i.MX6UL嵌入式开发板WIFI(型号:RTL8723BU) 驱动简易移植及测试2018-05-25 0

-

NXP i.MX6UL嵌入式开发板及linux根文件系统定制手册2018-08-31 0

-

【i.MX6UL/i.MX6ULL开发常见问题】单独编译内核,uboot生成很多文件,具体用哪一个?2019-07-01 0

-

【I.MX6UL申请】基于I.MX6UL的智能家居服务器2019-09-02 0

-

复杂处理器的上电时序有什么要求?2019-10-18 0

-

米尔i.MX6UL开发板Linux操作系统的应用开发介绍2021-02-02 0

-

i.MX6UL芯片是如何上电的2021-11-05 0

-

i.MX6UL如何使用串口进行数据通信2021-12-16 0

-

从i.MX6UL到i.MX RT的迁移手册2022-12-12 0

-

i.mx6ul板4G通信移植与使用2023-10-09 0

全部0条评论

快来发表一下你的评论吧 !