Tanner EDA:数字集成电路原理与设计课程教学的IC设计工具

描述

引言

“数字集成电路(Integrated Circuit,简称IC)原理与设计”是为高等学校电子、通信、机电等工科电子类专业的高年级本科生和硕士生开设的一门课程,是培养我国急需的、紧缺的IC设计人才的入门课程。其主要任务是使学生能在较为全面地了解IC设计工艺和掌握IC设计工具的基础之上,掌握IC基本单元的设计,为更复杂、规模更大的电路和系统的设计奠定理论基础,并通过相关实验使学生对微电子技术产生浓厚的兴趣。然而笔者经过调查发现,学生在学习过程中不能系统地了解自己所学的是什么、具体能干什么,以至于对IC设计产生不了浓厚的学习兴趣。实际上,“数字集成电路原理与设计”是一门实践性很强的专业课程,完全依靠传统的板书教学或者多媒体PPT教学都很难表达清楚。因此,如何在有限的学时内通过改革教学方法与教学手段实现教学理论与实践有机结合从而提高授课效率是现阶段该课程教学的一个研究重点。对于此问题,电子设计自动化(EDA)计算机仿真软件给IC教学提供了一个可靠的理论与实践联系的平台。

目前,IC设计仿真软件很多,其中按市场所占份额排行为Cadence、Mentor Graphics和Synopsys。这些工具功能极其强大,涵盖了IC设计的整个流程,包括系统级设计、功能验证、IC综合及布局布线、模拟和混合信号及射频IC设计、全定制IC设计、IC物理验证等。然而由于成本高、适用操作系统环境有所限制、不适合IC初学者等劣势,它们并不十分适合于本科生的教学工作。相比之下,本文介绍的Mentor收购的Tanner公司开发的基于Windows平台的用于IC设计的工具软件Tanner EDA更适用于高校进行相关的教学和科研工作。一放面,Tanner EDA成本低,设备要求不高,可以在任何个人PC机上使用。另一方面,该IC设计工具具有强大的IC设计、模拟验证、版图编辑和自动布局布线等功能,图形界面友好,编辑功能强,易学易用。

1 利用Tanner EDA进行IC设计的流程

利用Tanner EDA进行IC芯片设计的流程如下:

1.1 编辑原理图。利用电路图编辑环境S-Edit工具,根据设计要求编辑合理的电路原理图,注意在设计原理图时要与IC芯片代工厂使用的具体工艺相结合,设定器件的工艺参数。

1.2 模拟仿真。提取电路图的Spice网表(*.sp),用T-Spice工具模拟仿真电路的逻辑特性、延迟特性等,用W-Edit观察仿真波形。如果模拟结果有错误,需返回第一步修改原理图。如果无误,则以L-Edit进行版图设计。

1.3 版图设计。输出TPR网表(*.tpr),用L-Edit工具进行版图的编辑和生成,如果采用厂家提供的标准单元,此时可以直接利用L-Edit的自动布局布线SPR功能得到整个IC芯片的版图,如果是全定制设计,需事先根据所用的工艺,进行标准单元设计,注意在版图设计过程中要以DRC功能作设计规则检查。如果违反设计规则,则修改版图,直到设计规则检查无错误为止。

1.4 版图验证。将验证过的版图输出Spice网表(*.spc),使用T-Spice工具进行模拟仿真(后仿真),如果波形正确即通过验证;也可以用LVS工具,来对比版图和原理图,若一致,即通过验证。最终验证无错误后,将L-Edit设计的版图输出成GDSII文件类型,提交给IC芯片代工厂加工生产该IC芯片。

2 应用Tanner EDA设计5位同步加法计数器芯片的实例

2.1 用S-Edit编辑电路原理图

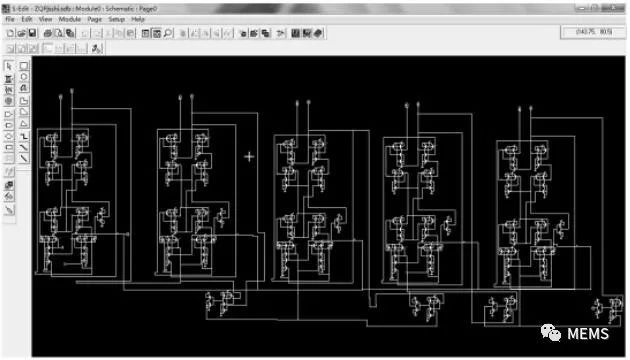

S-Edit工具简单易用,与Protel、Multisim、protues等常用的原理图编辑工具相比使用起来并不复杂,它可以设计特定功能的电路模块。图1是我们在S-Edit工具中利用element库中NMOS,PMOS等元器件得到的5位二进制同步加法计数器电路模块的原理图。该计数器采用5个边沿JK触发器串行连接而成,每个触发器均连成T触发器,再由4个2输入端与非门连接。S-Edit电路图编辑器可以把当前模块的电路图转化为不同的网表。这些网表主要是用于T-Spice电路模拟器的Spice网表,用于L-Edit版图编辑器中的标准单元自动布图布线的TPR网表、VHDL网表、NeTran网表以及EDIF网表。

图1 5位二进制同步加法计数器的原理图

2.2 用T-Spice进行模拟仿真

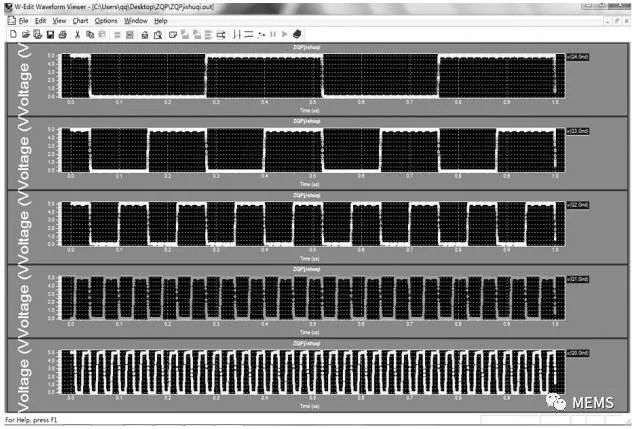

编辑好计数器的电路原理图后,为确认该电路功能正确,需要利用电路模拟工具T-Spice进行仿真,但该工具不能直接对原理图进行仿真,因此在仿真之前需从原理图输出Spice网表(*.sp),该网表文件以节点的形式描述了电路的拓扑结构和元器件的工艺参数。而在输出网表之后,必须加入工艺库模型文件、设定各种仿真必要的参数、确定分析电路特性所需的分析内容和分析类型等。根据T-Spice的格式要求得到*.sp网表文件之后,可以在T-Spice工具下进行电路的功能仿真。图2是从W-Edit观察到的5位二进制同步加法计数器的仿真波形图。

图2 5位二进制同步加法计数器的仿真波形图

2.3 用L-Edit进行版图设计

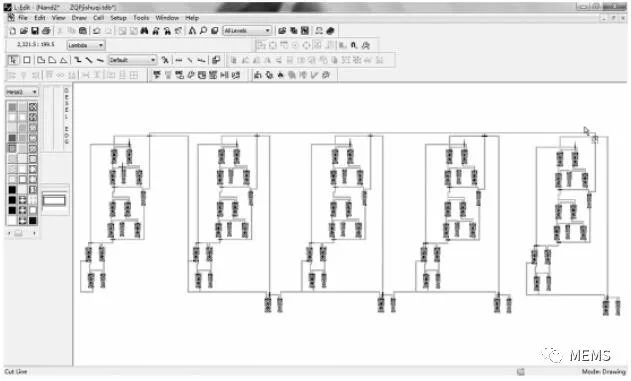

图3 5位二进制同步加法计数器芯片的版图

计数器电路的功能仿真正确后,需要利用L-Edit进行版图设计。根据事先应用特定工艺建立好的标准单元库 (反相器、与非门、或非门、异或门、同或门等),在L-Edit工具中利用电路图驱动版图技术(SDL)来进行计数器的版图设计。SDL能根据电路原理图转换的TPR网表(*. tpr)自动生成计数器电路中各个MOS管的版图,我们只需对这些MOS版图进行金属互连。值得注意的是,在MOS版图金属互连过程中,一定要进行设计规则检查(DRC),看是否符合事先设定的工艺设计规则,如果正确,下一步就是要用LVS进行版图与原理图的对比。

2.4 用LVS进行版图验证

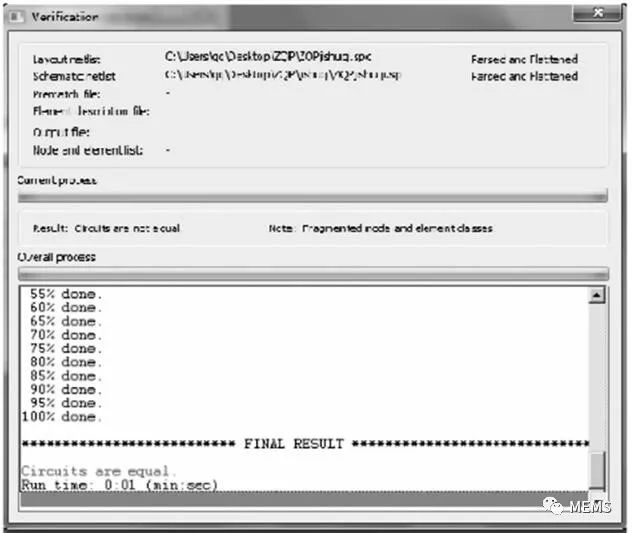

LVS(版图与电路图比较器)是一种网表比较工具,主要用来检查IC芯片版图的正确性。LVS通过比较L-Edit的Extract(版图提取器)从版图提取的Spice网表(*.spc)与S-Edit的网表输出功能从同一设计的电路原理图产生的Spice网表(*.sp),判别它们是否描述同一个电路。如果S-Edit中的电路图已通过验证,利用LVS,后一张网表可以作为判别前一张网表正确性的标准,实现电路图与版图的比较。如果两个网表一致,工具的对话界面将出现“Circuits Are Equal”的提示,则通过验证,说明设计成功。由图4的LVS对比结果可知本文成功设计了计数器。实际上,当不一致时,LVS还能帮助确认和改正版图中错误,然后重复进行验证过程,直到成功为止。最终将L-Edit设计好的版图输出成GDSII文件类型,提交给芯片代工厂加工生产该计数器IC芯片。

图4 LVS对比结果

3 结论

本文介绍了一种实用的、适合于数字集成电路原理与设计课程教学的IC设计工具Tanner EDA。通过以上应用实例可以看出,采用Tanner EDA进行IC设计,现象直观,结果精确。可见,将先进的计算机仿真技术和现代教学结合起来,有利于理论与实践的结合,对于学生理解IC的原理与设计流程,对于学生微电子技术的兴趣的激发、吸引他们涉足IC设计领域都有很好的帮助。

-

数字集成电路-电路、系统与设计 免费下载2009-02-12 0

-

数字集成电路速查2011-01-31 0

-

数字集成电路 应用+制作 PDF+22016-09-26 0

-

数字集成电路应用260例2017-02-07 0

-

什么是数字集成电路IC2021-03-03 0

-

CMOS数字集成电路是什么?CMOS数字集成电路有什么特点?2021-06-22 0

-

数字集成电路设计教学大纲2010-09-20 1038

-

数字集成电路简介2006-04-16 2176

-

数字集成电路的类别2009-09-19 1357

-

用数字集成电路设计的里程表2009-11-03 1685

-

数字集成电路分类及特点2010-02-06 7198

-

数字集成电路_什么是数字集成电路2011-10-28 3850

-

数字集成电路应用300例2011-10-28 7822

-

数字集成电路版图提取2011-10-28 1371

-

数字集成电路课程设计格式模板2017-04-19 775

全部0条评论

快来发表一下你的评论吧 !