一文看懂74LS112和74LS76的区别

芯片引脚图

描述

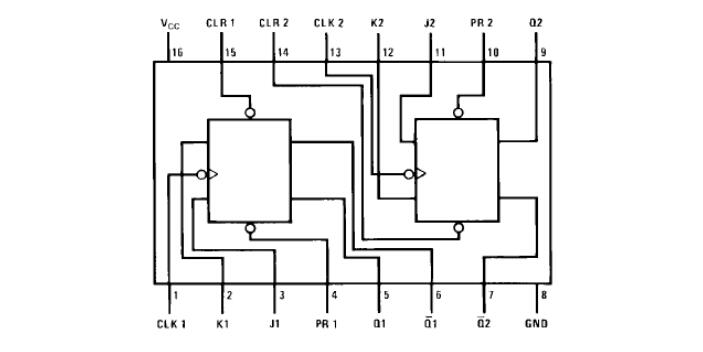

74LS112引脚图

引出端符号: CLK1、CLK2 时钟输入端(下降沿有效)

J1、J2、K1、K2 数据输入端

Q1、Q2、/Q1、/Q2 输出端

CLR1、CLR2 直接复位端(低电平有效)

PR1、PR2 直接置位端(低电平有效)

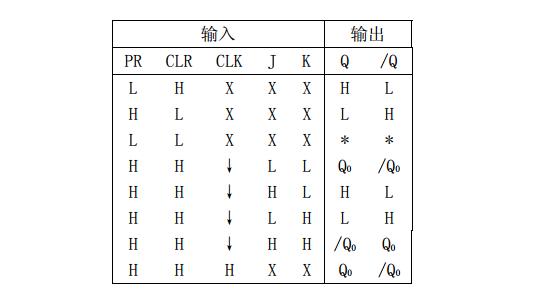

74LS112功能表

说明:H-高电平

L-低电平

X-任意

↓-高到低电平跳变

Q0-稳态输入条件建立前的Q的电平

/Q0-稳态输入条件建立前Q的电平或Q0 的补码

*-不定

74LS112极限值

电源电压------------------------------------------------7V

输入电压

54/74S112---------------------------------------5.5V

54/74LS112---------------------------------------7V

工作环境温度

54×××------------------------------ -55~125℃

74×××------------------------------------0~70℃

贮存温度-------------------------------------- -65~150℃

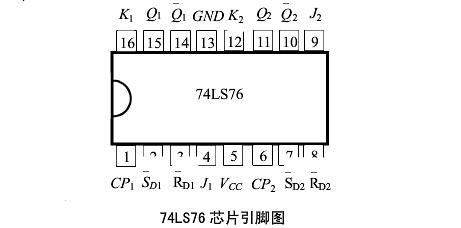

74LS76引脚图

74LS76集成电路为双JK触发器,其管脚图如右图所示。其中J、K为触发器的输入端,Q、Q(-)为两个输出端,S(-)D为置“1”端,R(-)D为置“0”端,CP为时钟输入端。实验中只用其一个JK触发器。

(1)S(-)D、R(-)D的功能测试

将74LS76双JK触发器5脚接电源正极(+5V),13脚接地,CP端和J、K端悬空,R(-)D、S(-)D端分别接至数字电路实验机数据开关SW3、SW4,Q和Q(-)分别接至数字电路实验机逻辑指示灯L1、L2。测试S(-)D、R(-)D的功能。

(2)逻辑功能测试

将J、K端分别接至数字电路实验机数据开关SW1、SW2,时钟输入CP接至数字电路实验机右上端任一逻辑开关(拨动逻辑开关相当于产生一个单脉冲),SW3、SW4接R(-)D、、S(-)D,在实验过程中,视触发器置位、复位需要,需拨动SW3、SW4,从而完成触发器的置位、复位,完成后SW3、SW4都应置高电平。测试JK触发器的逻辑功能。

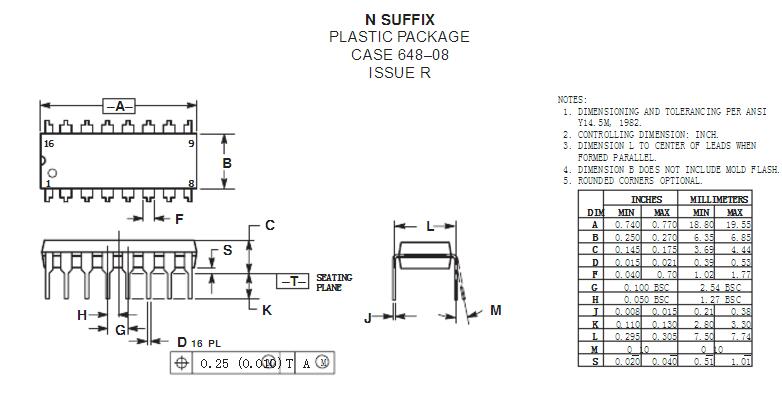

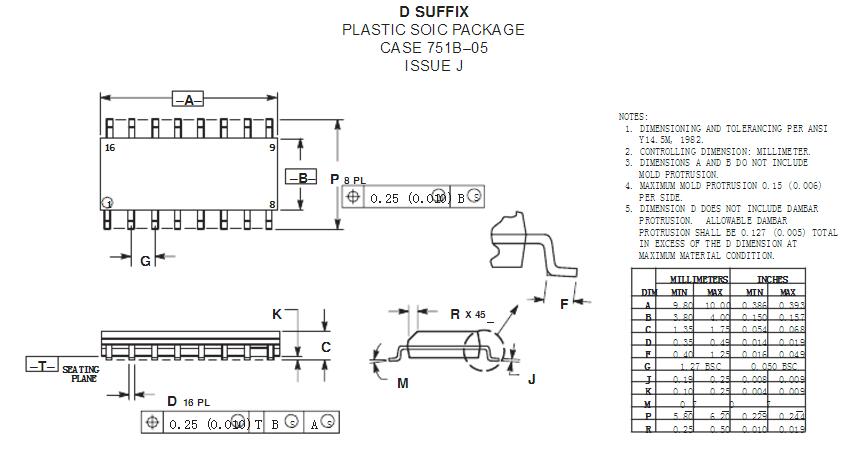

74LS76封装

74LS112和74LS76的区别

74LS112和74LS76都是双J-K触发器,下降沿触发,带正向输出端和反向输出端,各自带有独立的触发信号输入、清零和置位引脚。但是他们的引脚不兼容,就是说相同功能的引脚排列位置不完全一样(少数引脚位置相同,如Vcc、GND、1通道触发信号输入、2通道K端;但其他的多数引脚位置不同)。

-

HD74LS74与SN74LS74有啥区别2017-10-10 0

-

74LS112中文资料pdf2008-03-20 9120

-

74LS112/54LS112 pdf datasheet2008-08-06 28587

-

74LS688/74LS682/74LS684/74LS682008-08-06 2157

-

74LS112型双JK触发器芯片引脚图管脚图2009-02-14 81127

-

74LS系列芯片总汇(76种)2015-12-28 5112

-

74LS112 英版数据手册2016-08-29 1061

-

74LS112英文手册2016-11-15 1573

-

74ls147和74ls148有什么区别2018-05-07 32395

-

74ls160和74ls161区别2018-05-08 117290

-

74ls161与74ls163有什么区别2018-05-08 55888

-

74ls112引脚图及功能详解 74ls112的功能及原理2018-05-29 284520

-

74ls112应用电路图大全(模七计数器/抢答器电路)2018-05-29 64148

-

74ls112引脚图及功能表2021-06-29 99946

-

74ls76的管脚图和功能表2021-07-02 46107

全部0条评论

快来发表一下你的评论吧 !