adf4350编程使用总结(adf4350引脚功能及应用电路)

编程实验

描述

ADF4350简介

ADF4350具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200MHz至4400MHz。结合外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。所有片内寄存器均通过简单的三线式接口进行控制。该器件采用3.0V至3.6V电源供电,不用时可以关断。

ADF4350特性

输出频率范围:137.5MHz至4400MHz

小数N分频频率合成器和整数N分频频率合成器

低相位噪声VCO

可编程1/2/4/8/16分频输出

均方根(RMS)抖动:0.5ps(典型均方根值)

电源电压:3.0V至3.6V

模拟和数字锁定检测

在宽带宽内快速锁定模式

周跳减少

1.8V逻辑兼容

可编程双模预分频器:4/5或8/9

可编程输出功率水平

RF输出静音功能

三线式串行接口

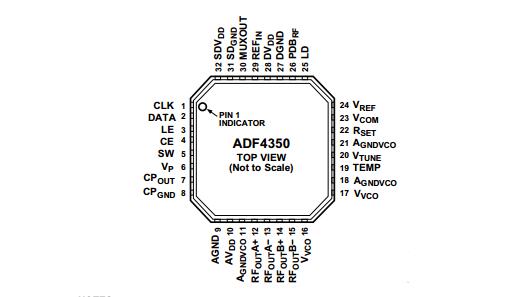

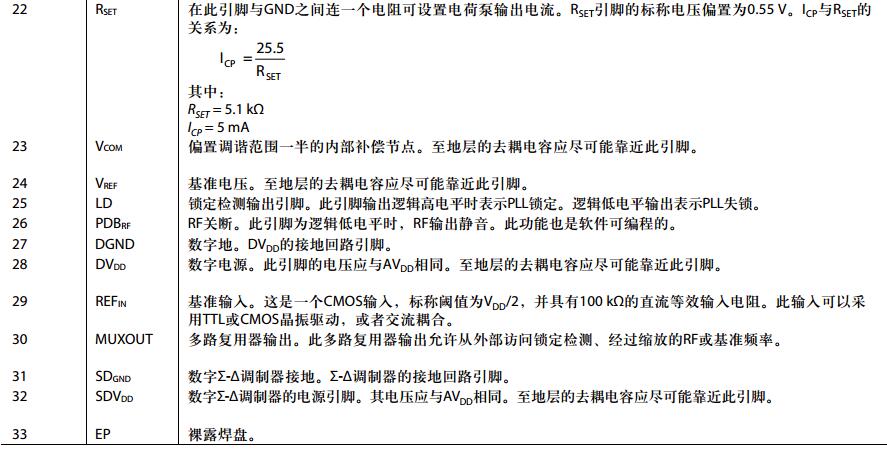

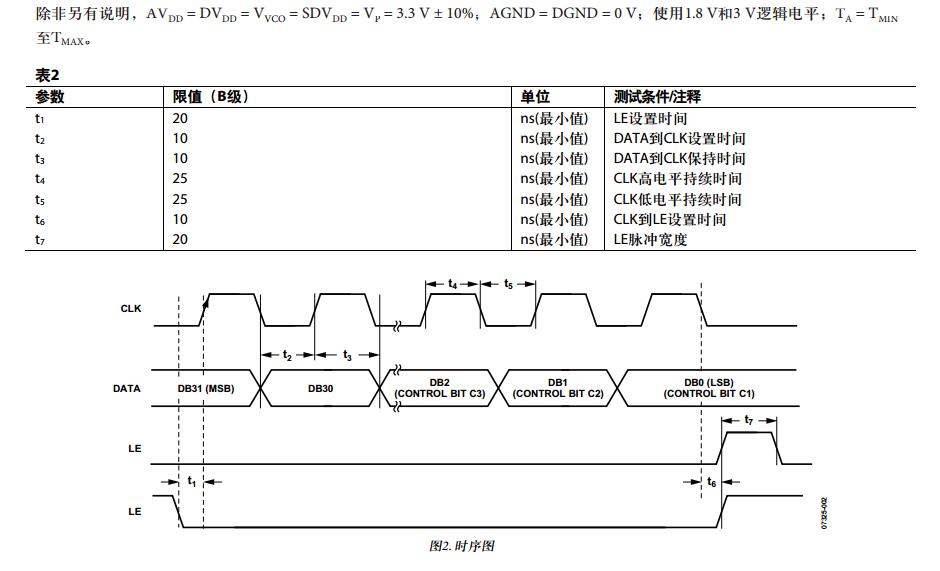

adf4350引脚图及功能

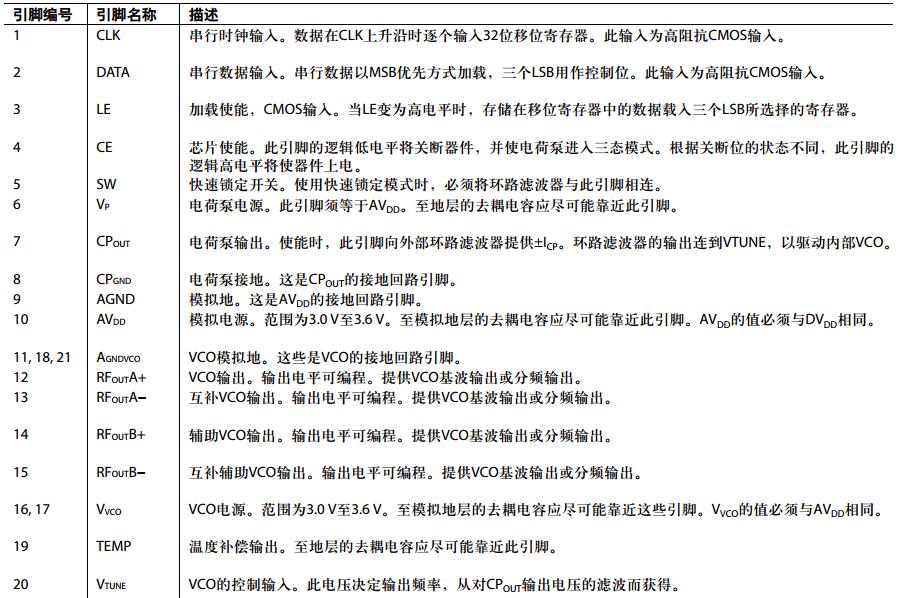

adf4350时序特性

adf4350应用电路

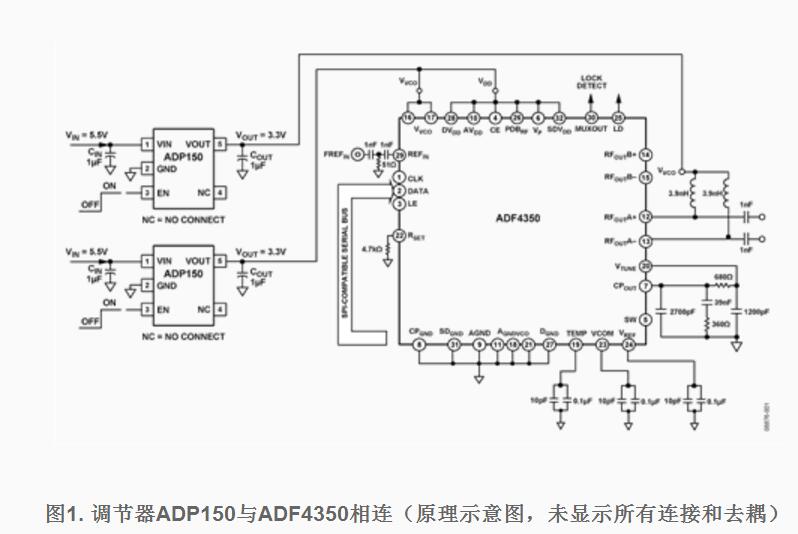

本电路利用低噪声、低压差(LDO)线性调节器为宽带集成PLL和VCO供电。宽带压控振荡器(VCO)可能对电源噪声较为敏感,因此,为实现最佳性能,建议使用超低噪声调节器。

图1所示电路使用完全集成的小数N分频PLL和VCO ADF4350,它可产生137.5 MHz至4400 MHz范围内的频率。ADF4350采用超低噪声3.3 V ADP150调节器供电,以实现最佳LO相位噪声性能。

ADP150 LDO的积分均方根噪声较低,仅为9 μV(10 Hz至100 kHz),有助于尽可能降低VCO相位噪声并减少VCO推压的影响(等效于电源抑制)。

图2是评估板的照片,它利用ADP150 LDO为ADF4350供电。ADP150代表业界噪声最低、封装最小、成本最低的LDO,采用4引脚、0.8 mm x 0.8 mm、0.4 mm间距WLCSP封装或方便的5引脚TSOT封装。因此,在设计中加入ADP150对系统成本和电路板面积的影响极小,但却能显著改善相位噪声性能。

adf4350编程使用总结

近来项目中使用了ADI公司的ADF4350芯片来产生3.45GHz的本振信号。调试中也遇到了一些问题,现在跟大家分享一下设计的过程和调试经历。

一、设计原理

锁相环的基本原理,相信大家都很熟悉,在此就不陈述了。设计中使用10MHz晶振或者信号源做为参考输入,差分3.45GHz输出。采用小数分频模式,低噪声模式,鉴相器频率为20MHz(芯片内部将输入时钟倍频),环路滤波器带宽为100KHz,分频比172.5。设计中使用FPGA(XilinxV5FX70T)来进行SPI配置。

另外,设计时将LD管脚连接上一个LED灯,程序中配置成模拟锁定,来观察锁相环是否锁定。相关的verilog配置程序在附件中[hide][/hide]。

寄存器配置的数据为:

Regisiter5:

32‘h00C00005;

Regisiter4:

32’h000803FC;

Regisiter3:

32‘h000101B3;

Regisiter2:

32’h06005E42;

Regisiter1:

32‘h0800FD01;

Regisiter0:

32’h00563E80;

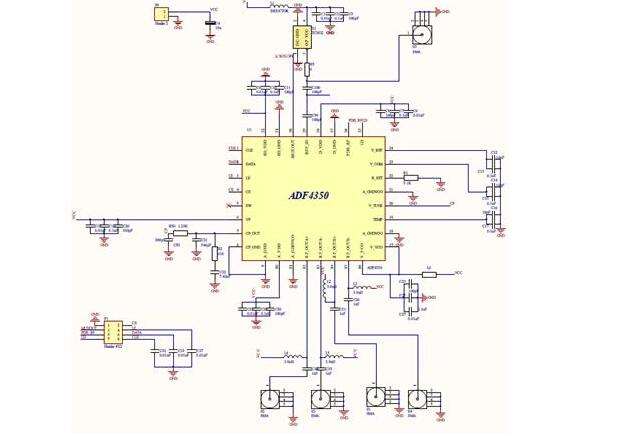

锁相环原理图设计主要包括电源电路设计,FPGA输入信号电路设计,管脚去藕设计,外接环路滤波器设计,输出电路匹配设计,具体电路图见图1。

图1ADF4350外围电路图

1.1管脚去藕设计:

由于PLL电源和电荷泵电源质量要求比较高,所以电源要具有良好的退耦,相比之下,电荷泵的电源具有更加严格的要求。具体实现如下:

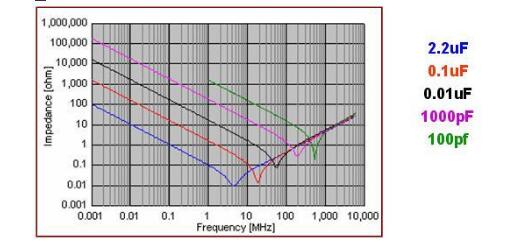

在电源引脚出依次放置0.1µF,0.01µF,100pF的电容。最大限度滤除电源线上的干扰。大电容的等效串联电阻往往较大,而且对高频噪声的滤波效果较差,高频噪声的抑制需要用小容值的电容。如图2可以看到,随着频率的升高,经过一定的转折频率后,电容开始呈现电感的特性。不同的电容值,其转折频率往往不同,电容越大,转折频率越低,其滤除高频信号的能力越差。

图2电容阻抗特性分析

1.2环路滤波器设计

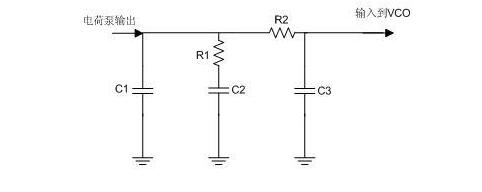

环路滤波器使用ADI公司的ADIsimPLL来设计,使用的是无源低通滤波器,带宽100KHz(如图3)。图中电容器C1来自电荷泵(ADF4350的CP引脚的脉冲转化为直流电压,但是根据对开环传递函数分析,它存在一个二阶极点,会引起环路的不稳定。所以引入了R1和C2稳定环路。它给直流控制电压带来的纹波干扰,可由C3滤除。

图3环路滤波器原理图

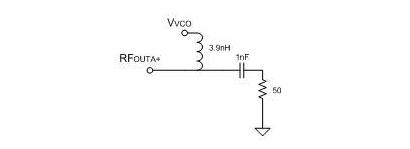

1.3输出电路匹配

输出电路采用datasheet建议的匹配电路来实现(如图4)。

图4RF输出匹配2图

二、测试过程

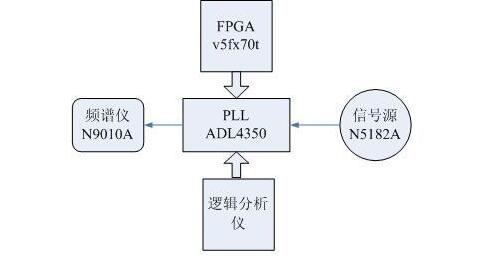

2.1测试平台如图5所示。

2.2测试步骤

1、检查电路焊接无误,上电查看电流在正常值范围,电路中电压测量正常。

2、为了测试外接晶振性能,先使用信号源产生20MHz的时钟输入信号接到CLK管脚。再接上信号源、频谱仪,用FPGA将配置信息下载到PLL,PLL输出随每次通断电结果时有时无,有输出时频率也不对。

图5测试平台

3、检查电路连接,发现FPGA和PLL没有共地,共地后测试,仍然没有结果,此时电流在80mA左右,datasheet上查看正常工作时电流在140mA左右。

4、分析:有几次信号输出,说明电路能够正常工作,主要可能是配置数据不正确或者没有配置下去。

5、将这些电容拿掉,重新配置,结果还是不对,是否是SPI配置速度太快,PLL芯片来不及响应,当前配置速度为10MHz,虽然PLL的datasheet上说明配置速度最高可以支持到20MHz,但也只是给出了最大值,没有典型值,决定将速度改低试试。

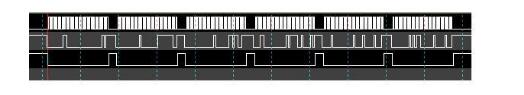

6、将速度改为1M,重新配置,结果还是不对,使用逻辑分析仪抓取PLL这边SPI数据。

7、再次使用逻辑分析仪抓取PLL这边SPI数据。发现在数据和LE上有很多毛刺,持续时间达到100ns,PLL的datasheet显示LE引脚只要持续高电平20ns即可将数据锁存进PLL,毛刺会干扰数据锁存。

图6配置数据抓取结果

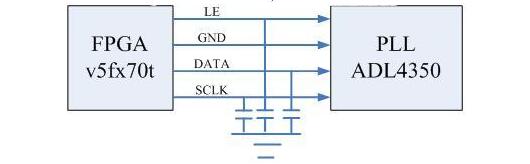

11、在DATA,SCLK管脚上焊接并联到地的电容,另外在LE引脚也加上并联到地的电容,以滤除毛刺(如图)。重新配置,此时抓取的波形显示已没有毛刺(如图8),但是依然无法锁定。

图7FPGA与ADF4350控制接入图示

图8配置数据抓取结果

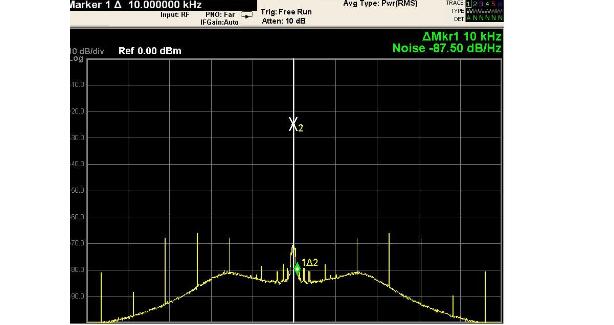

12、重新焊接环路滤波器,锁定,LED灯亮,输出3.45GHz信号。测试的相位噪声结果如下:10KHz的相位噪声如图9所示

-76.09dBc/Hz1KHzoffset@3.45GHz

-87.50dBc/Hz10KHzoffset@3.45GHz

图[font=Verdana]9

10KHzoffset@3.45GHz相位噪声

三、测试中的注意事项

测试中还遇到了一些其它的问题,在此不一一详述,现在分享下总结的测试步骤及问题总结。

1.检查电路连接无误,排除短路等一些问题。

2.上电,测试电源电压,电流是否正确,参考时钟有无输出。

3.先把ADF4350板子上电,然后进行SPI配置。要注意上电顺序相当重要,如果ADF4350和FPGA同时供电,可在程序上作一定的延时来避免同时上电。如果配置没有结果,可以通过逻辑分析仪来抓取配置数据,分析程序是否正确。如果配置数据无问题,可以在clk,data,le管脚并联10K的电阻来保证数据能下进ADF4350。

4.如果配置数据没有问题,输出锁定的频率不正确,很大的可能是环路滤波器焊接的问题,根据调试经验,这种情况下,大部分都能通过重新焊接来锁定。

5.因为小数分频杂散比较大,所以可以选择整数分频模式。调试中也进行了相关的实验,影响不是很大,大家也可以做相关的实验。

6.参考时钟的信号质量对芯片的时钟输出质量影响很大,所以尽量选用质量好的时钟源。

7.环路滤波器的带宽选择,测试最终选择了100KHz的环路带宽,测试中也尝试了更低的环路带宽,比如50KHz,但是影响锁定时间或者无法锁定。

-

追光者Jared

2022-06-26

0 回复 举报附件在哪呢 收起回复

追光者Jared

2022-06-26

0 回复 举报附件在哪呢 收起回复

- 相关推荐

- ADF4350

-

PLL芯片ADF4350的使用2011-11-23 0

-

ADF4350调试记录2018-10-24 0

-

ADF4350无法锁定2018-10-24 0

-

请问怎么用可变频率源作为ADF4350的参考?2018-10-25 0

-

请问ADF4350 RF输出能否悬空2018-11-27 0

-

ADF4350的调试2019-03-05 0

-

stc15w408s控制ADF43502019-12-01 0

-

ADF4350/ADF4360应用电路(参考设计)2009-09-02 1157

-

ADF4350芯片手册2016-02-25 1214

-

ADF4350 集成VCO的宽带频率合成器2019-02-22 721

-

ADF4350/ADF4351 Evaluation Board Software2021-03-10 646

-

ADF4350参考代码2021-03-18 592

-

ADF4350 IBIS型号2021-04-09 390

-

EVADF4350 ADF4350 评估板2021-06-03 484

全部0条评论

快来发表一下你的评论吧 !