提高数据吞吐量和系统效率,多通道DAQ很关键

描述

在多通道多路复用数据采集系统中,增加每个 ADC 的通道数量可改善系统的整体成本、面积和效率。现代 SAR ADC 具有高吞吐量和高能效,使得系统设计人员能够实现比以往更高的通道密度。

今天我们将说明多路复用器输入端的建立瞬变(由多路复用器输出端的大尺度开关瞬变引起)导致需要较长采集时间,使得多通道数据采集系统的整体吞吐量显著降低。然后,文中将着重阐述使输入建立时间最小化以及提高数据吞吐量和系统效率所需的设计权衡。

什么是多通道 DAQ?

如何衡量多通道 DAQ 的性能?

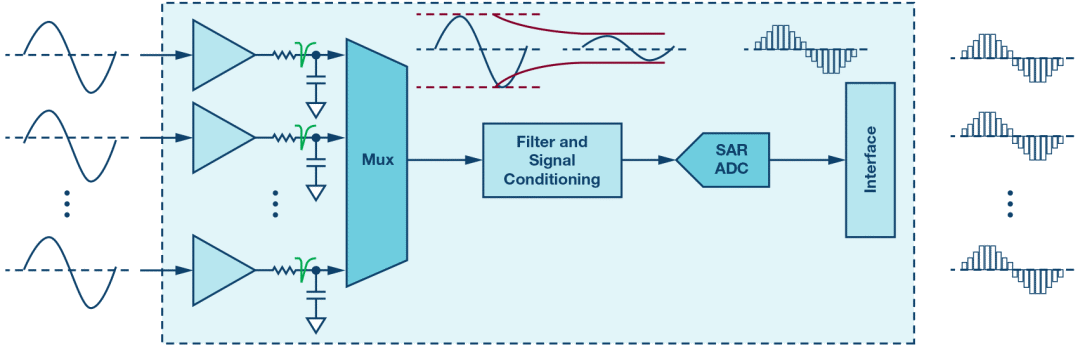

多通道数据采集 (DAQ) 系统是一个与多路输入(通常是传感器)接口的完整信号链子系统,其主要功能是将输入端的模拟信号转换为处理单元可以理解的数字数据。多通道 DAQ 系统的主要组成部分有模拟前端子系统(缓冲器、开关元件和信号调理模块)、ADC 及数字接口。对于高速精密转换器,开关元件(通常是多路复用器)放置在 ADC 驱动器和转换器本身之前,以利用现代 ADC 的先进性能。SAR ADC 兼具高速度和高精度性能,是这些应用最常用的 ADC 类型。

图1. 典型的基于SAR ADC的多路复用数据采集系统框图

用于工业和医疗应用的高通道密度精密DAQ系统致力于将最多的通道压缩到尽可能小的区域中。通过如下手段,多路复用 DAQ 系统一般可以实现高密度、高吞吐量和良好的能效:

-

使用高速精密 SAR ADC

-

每个通道使用最低采样速率

-

最大程度提高 SAR ADC 转换器利用率

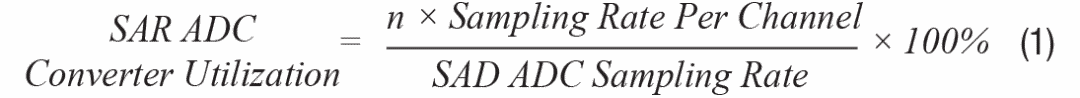

其中:

|

n 为通道数。对每个转换器而言,多通道数据采集系统的总吞吐量由下式给出:

|

这表明多通道 DAQ 系统的总吞吐量不仅取决于 SAR ADC 的速度和分辨率,还取决于此转换器的利用情况。

延迟如何影响多通道 DAQ 系统的性能?在有建立延迟的情况下,ADC 的实际采样和转换周期会增加一项 td,导致转换器的实际最大采样速率由下式给出:

|

其中 TADC 是 ADC 每个样本的采样周期(大多数 ADC 数据手册通常都会提供,更常见的形式是 SAR ADC 采样速率的倒数,以"秒/样本"为单位)。对于非零延迟 td,多通道 DAQ 系统的实际最大采样速率总是小于转换器采样速率,导致转换器利用率始终低于 100%。由此可以明白,采样和转换周期上增加的任何延迟都会降低转换器的利用率。当与前面关于总吞吐量的表达式联系起来时,多通道 DAQ 可以容纳的最大通道数量就会减少。总之,任何建立延迟都会降低多通道DAQ系统的通道密度和/或总吞吐量。

什么是多路复用器输入切换毛刺和输入建立时间?

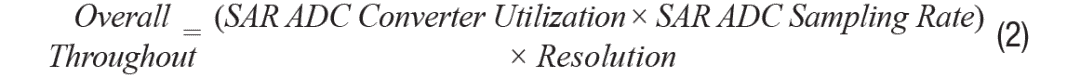

当多路复用器从一路输入切换到另一路输入时,输出仍然有前一输入通道的记忆,其表现形式为多路复用器的输出负载电容和寄生漏极电容中存储的电荷。这对于高容性负载(例如 ADC 驱动器和 ADC 本身)更为明显,因为这些存储的电荷没有低阻抗路径可以走。甚至可以说这些电荷被困住了,原因是输出为容性,并且现代多路复用器采用先开后合 (BBM) 机制,故多路复用器具有高阻抗。只有切换到下一路输入,这些电荷才能被释放电。

图2. 切换前状态(左),切换后,发生电荷共享,迅速引起电压下降ΔV(右)

切换后,输入电容 CA 将并联到输出电容 COUT。然而,CA 和 COUT 最初可能处于不同的电位,这将导致 CA 和 COUT 之间发生电荷共享。对于超高带宽多路复用器,电荷共享几乎立即发生,导致多路复用器输入端出现高频毛刺。此毛刺的幅度 ΔV 由下式给出:

|

其中 ΔVC 是切换之前电容电压的差值。多路复用器输入侧发生的瞬态毛刺现象就是通常所说的反冲,其对于具有高容性负载(例如 ADC、容性 DAC 和采样电路等)的开关应用更为普遍。转换器要产生有效数据,毛刺必须稳定在输出的1 LSB以内,而输入稳定在 1 LSB 以内(并保持在该范围内!)所需的时间就是输入建立时间(tS)。tS 是前面描述的延迟td的组成部分,它对此项的贡献可能是最大的。

当 ADC 不像现在这样快时,这些毛刺及相应的输入建立时间微不足道,可以忽略不计。但是,随着 ADC 速度的提高,转换器采样周期变得越来越短,接近输入建立时间的量级。如前所述,当 ADC 周期 TADC 等于输入建立时间 tS(事实上是 td)时,转换器利用率大大降低至50%。这意味着我们只使用了转换器的一半能力!需要重申输入建立时间的重要性,它应与精密转换器的当前技术同步发展,为提高多通道 DAQ 系统的性能铺平道路。

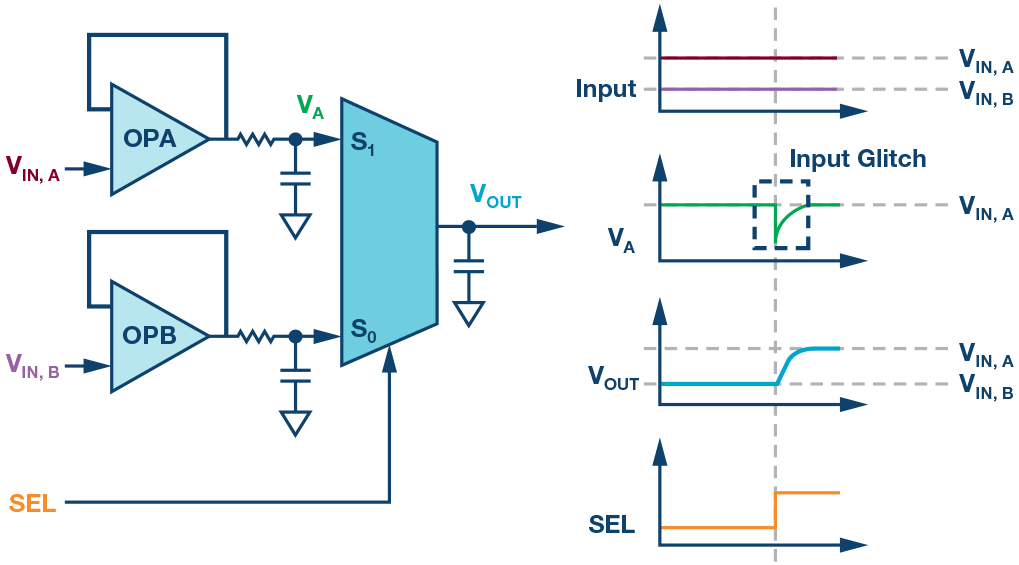

如何最大程度缩短输入建立时间?为使开关毛刺最小化,通常在缓冲放大器和多路复用器之间使用一个 RC 滤波器,称之为缓冲器网络。图3显示了一个双通道多路复用模拟前端子系统的信号链子系统及其相应的开关时序图。

图3. 多通道 DAQ 系统的双通道多路复用模拟前端子系统及相应的时序图

缓冲器RC作为主导极点,假设多路复用器相对于放大器和缓冲器 RC 具有非常高的带宽,那么输入毛刺和建立瞬变可近似为具有一阶(指数)响应。为了进一步分析输入毛刺,图 4 详细显示了输入毛刺瞬态响应。

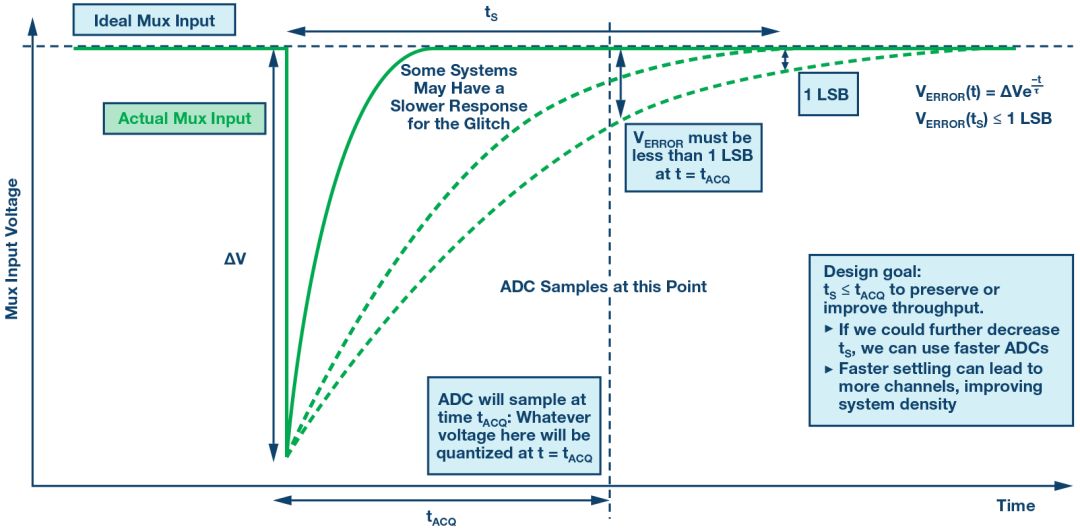

图4. 分析切换期间的多路复用器输入毛刺:时序定义和设计目标

对于一阶假设,误差 VERROR 的表达式是一个关于时间的递减指数函数。VERROR 的初始值(切换时的值)为毛刺幅度 ΔV,其将以缓冲器RC值决定的速率衰减。VERROR 稳定在 1 LSB 以内所需的时间被定义为输入建立时间。

另一方面,转换器以周期 tACQ 采样(也称为采集时间)。在 tACQ 过去后的 ADC 转换阶段,转换器将量化任何可用的采样数据。如果VERROR衰减速度过慢,导致其未稳定在某一值(1 LSB 到几个 LSB )以内,就会产生问题。这将导致当前样本被前一模拟输入破坏,引起 ADC 通道之间的串扰。考虑到输入建立时间,必须确保输入建立时间小于转换器采集时间,以使误差最小。而且,进一步减小 tS 还为使用更快转换器以提高系统总吞吐量和密度提供了机会。

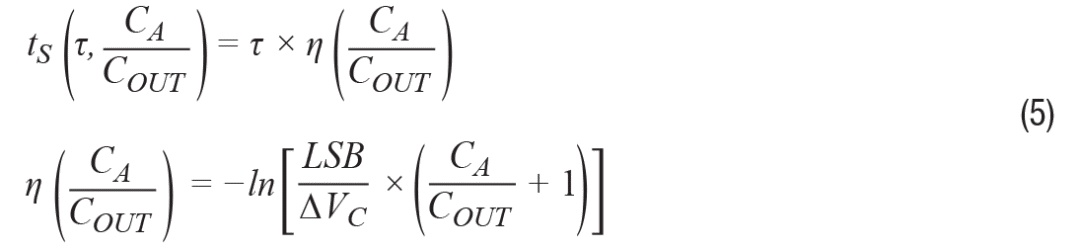

利用我们的数学技能,当 ΔVC 为满量程输入范围且 VERROR 达到至少 1LSB(多路复用器输出在目标电平的 1 LSB 以内)时,可以推出最差情况下的最快输入建立时间表达式。多通道 DAQ 系统设计人员将拥有两个设计抓手:缓冲器时间常数和 CA/COUT 比率,从而得出输入建立时间的表达式:

|

这里可以看出,输入建立时间是缓冲器时间常数 τ 和 VERROR 稳定在 1LSB 以内所需的时间常数数量 η 的线性函数。减少输入建立时间的最直接方法是使用时间常数较小的缓冲器网络,这很有意义,因为较快的(高带宽)缓冲器网络会降低时间常数。然而,这种方法将带来一组不同的涉及噪声和负载的权衡。另一方面,η 项最小化也可以达成类似的结果。

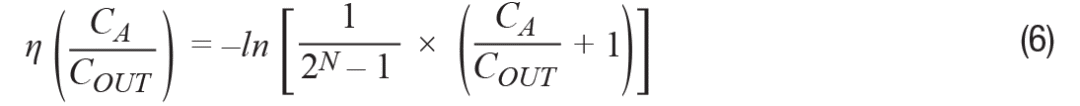

η 是缓冲器电容 (CA) 与输出电容 (COUT) 之比的函数。如果 1 LSB 等于满量程输入范围除以 2 的 N-1 次方(N为位数),并且最差情况下 ΔVC 等于满量程输入范围,则该表达式可以进一步简化。

|

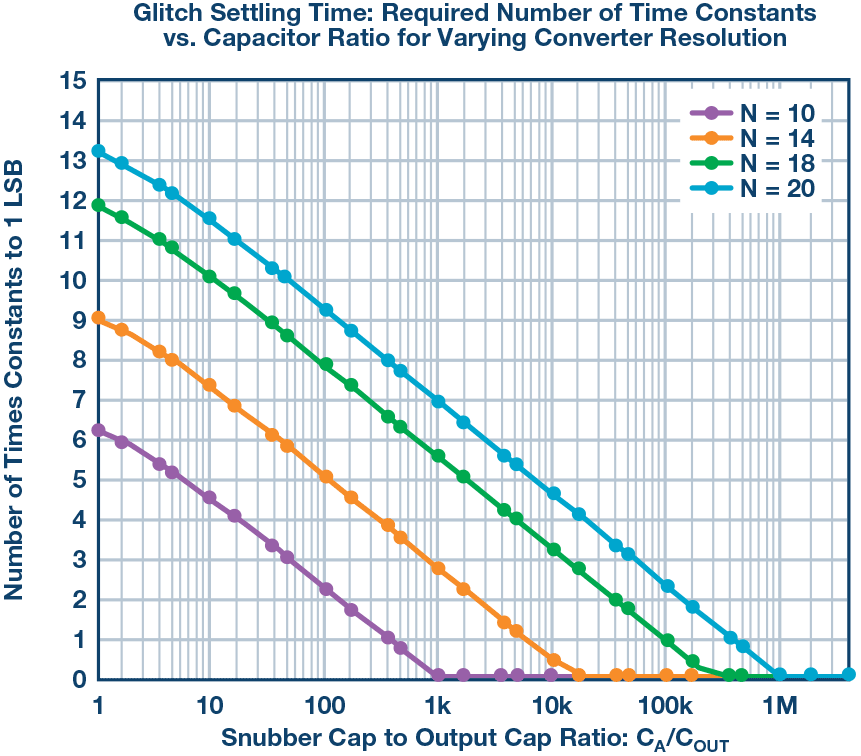

公式 6 可能不那么直观,很难可视化,所以仅利用 10 位、14 位、18 位和 20 位分辨率的半对数图来说明可能更好,如图 5 所示。

图5. 建立至1 LSB所需时间常数的图形

可以看出,CA/COUT 值越高,则建立时间越短;电容比非常高时,建立时间甚至接近 0。COUT 实质上是多路复用器的漏极电容和后续各级的输入电容,因此只有 CA 保持比较灵活的自由度。对于 10 位分辨率,要使建立时间为 0,CA 须比 COUT 大至少1000倍;对于 20 位系统,至少要比 COUT 大 1,000,000 倍!举例来说,对于 10 位和 20 位系统,为使建立时间为 0,100 pF 的典型负载分别需要 100 nF 和 100μF 的缓冲器电容。

总之,输入建立时间最小化可以通过两种方法实现:

-

对缓冲器网络使用高带宽;

-

相对于COUT,使用较高的CA值。

高带宽和大缓冲器电容可最大限度地减少输入建立时间,所以使用最高带宽和最大电容就行了?

非也!必须考虑 RC 负载效应和放大器的驱动能力!为了研究缓冲器网络对缓冲放大器的负载影响,应在频域分析模拟前端子系统。

由于我们将输入毛刺建立在一阶响应的思想上,所以缓冲器网络极点应该就是最主要的贡献者。换句话说,缓冲器带宽应该小于缓冲放大器和多路复用器的带宽,以避免多极点交互,确保一阶近似成立。

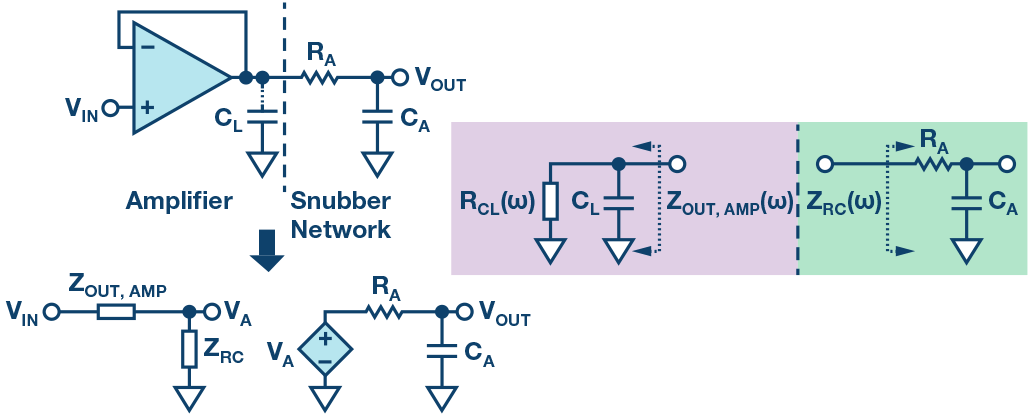

图6. 缓冲和缓冲器等效电路(左)与放大器和缓冲器网络的等效阻抗(右)

典型缓冲架构由缓冲(G = 1)配置的精密放大器与缓冲器网络级联组成。在频域中分析,此子系统的输出取决于缓冲器输入阻抗与缓冲器输入阻抗和放大器闭环输出阻抗之和的比率。检查可知,为避免负载效应,缓冲器输入阻抗应该大于放大器闭环阻抗,如公式7所示。

|

也就是说,为避免缓冲器网络成为缓冲放大器的负载,我们应该:

-

增大缓冲器时间常数 RACA,以有效降低带宽

-

使用较小缓冲器电容 CA

-

选择闭环输出阻抗非常低的放大器

前两个选项使我们清楚地了解到负载效应和输入建立时间之间的取舍。这限制了我们可以使用的缓冲器带宽和电容的大小。第三个选项引入了一个性能参数,选择适当的精密放大器时应予以考虑。还应考虑稳定性和驱动能力。

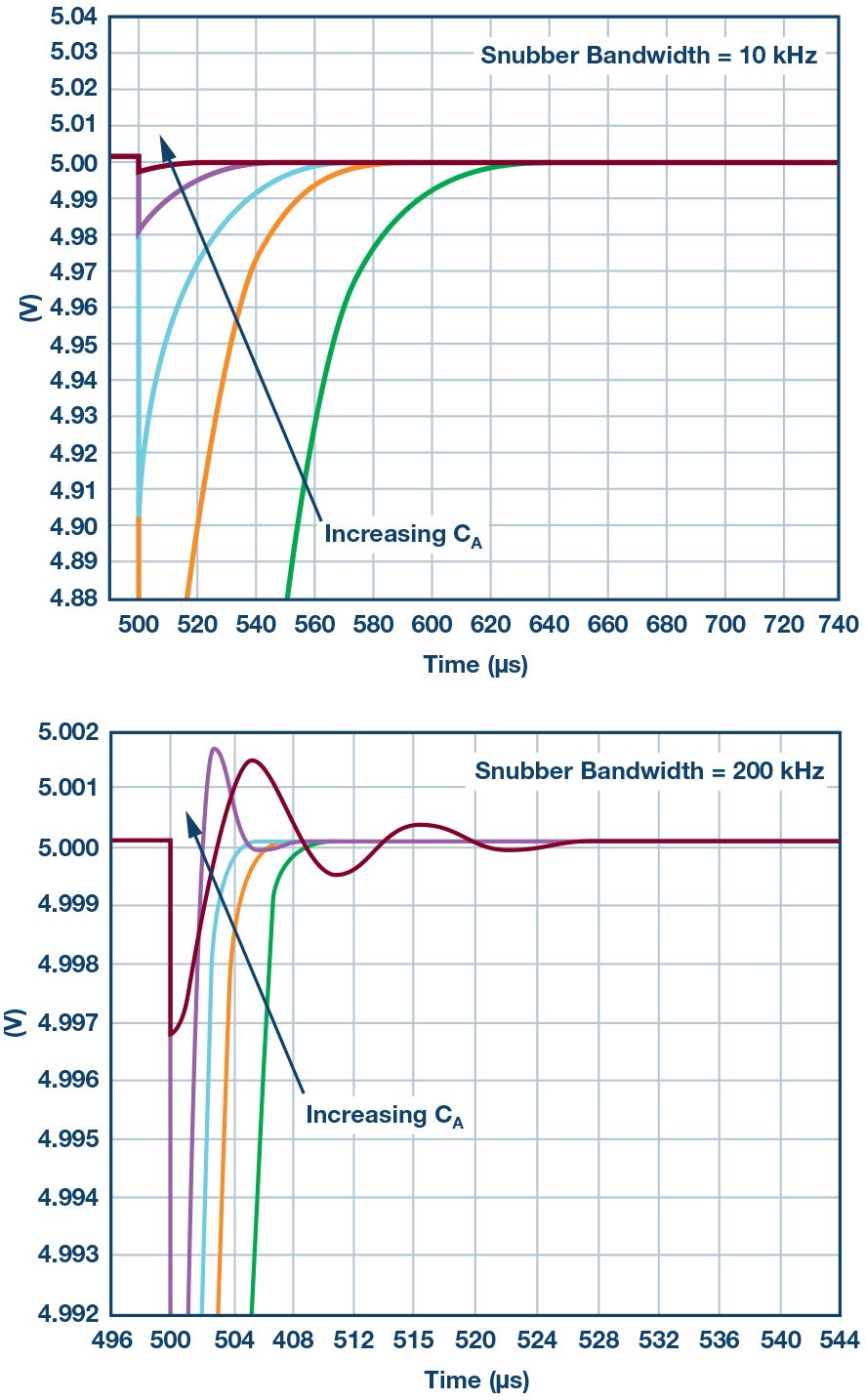

图7显示,对于具有足够带宽的精密放大器(例如 -3 dB 闭环带宽约为 970 kHz 的 ADA4096-2,结果与目前进行的分析一致,但少数波形除外。对于10 kHz 的缓冲器带宽,最大 CA 产生最快的输入建立时间。而对于 200 kHz 的缓冲器带宽,增大 CA 仍然会加快建立时间,直至发生负载效应。从结果中看到的欠阻尼响应具有极小的毛刺幅度,但建立时间比较小 CA 所产生的响应要长,尽管后者的毛刺幅度较高。这凸显了仔细研究缓冲器如何加载放大器的重要性,在为系统选择器件时务必考虑这一点。

图7. 针对10 kHz(上方)和200 kHz(下方)缓冲器带宽的多路复用器输入,ADA4096-2放大器模型

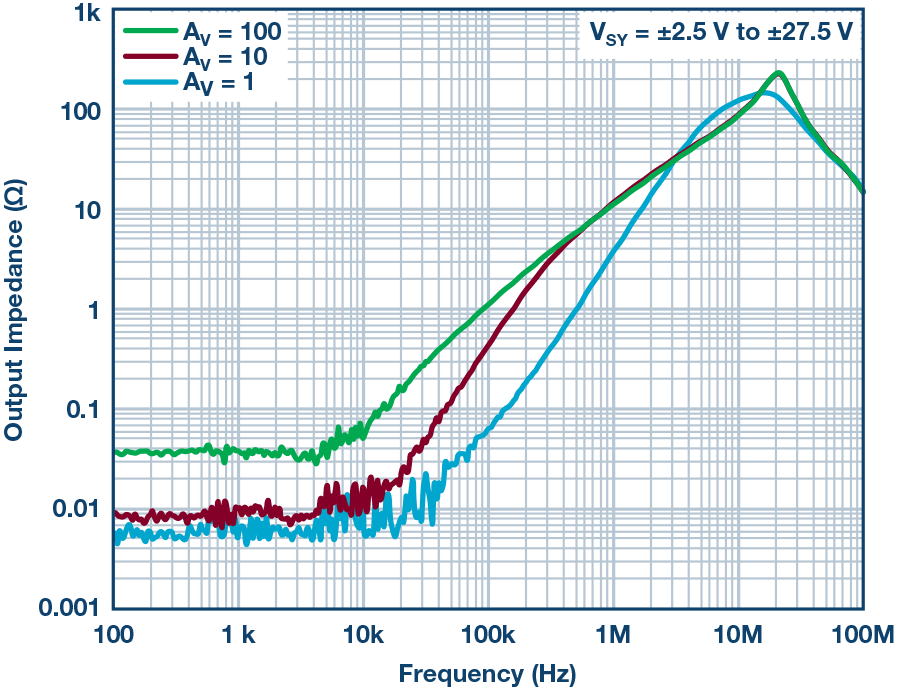

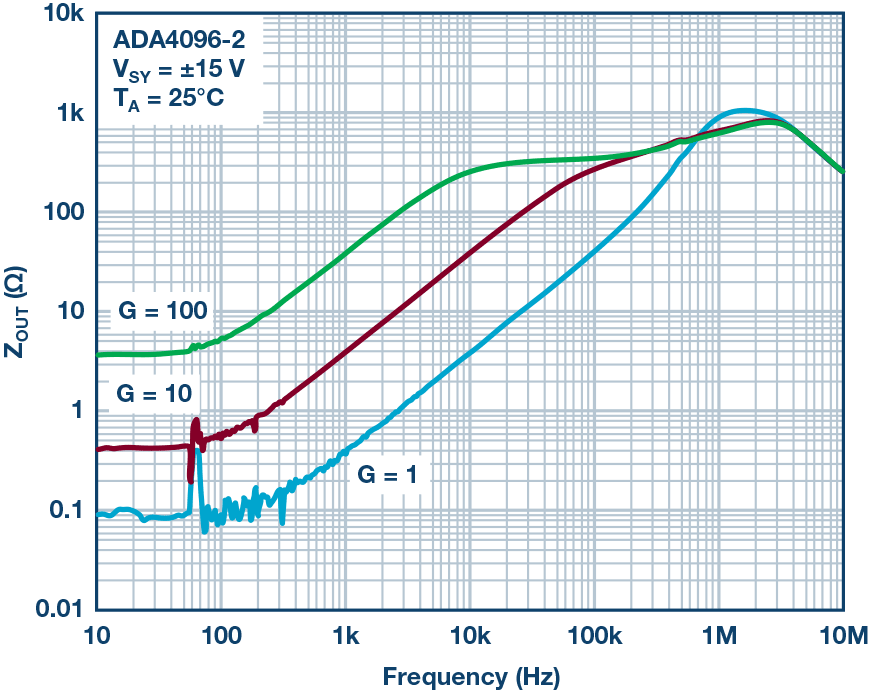

如前所述,需要注意的一个放大器参数是闭环输出阻抗。运算放大器的闭环阻抗通常与其开环增益AV成反比。我们还希望缓冲器网络具有高带宽以使建立时间最短,因此要求放大器的-3 dB带宽甚至大于缓冲器带宽。除了较低的噪声、失调和失调漂移外,最适合用于多路复用 DAQ 系统以实现最小输入建立时间的精密放大器还有两个优先特性:1)具有高带宽,2)具有非常低的闭环阻抗。然而,这些优势的得来并非没有代价,而代价的表现形式就是功耗。例如,我们可以查看图 8 所示的 ADA4096-2 和 ADA4522-2 的闭环阻抗。

图8a. ADA4522-2数据手册中的闭环阻抗图

图8b. ADA4096-2数据手册中的闭环阻抗图

考虑数据手册中的闭环输出阻抗图,以及 ADA4522-2 的 -3 dB 闭环带宽为 6 MHz(标称值),显然可知它是更适合该应用的驱动器。但当功耗优先时,ADA4096-2 的每个放大器的电源电流为 60 μA(典型值),比 ADA4522-2 的每放大器 830 μA(典型值)更具吸引力。尽管如此,这两款精密放大器都可以使用,最终取决于应用真正需要达成的目标。

我们怎么做最好?-

为了最大限度地提高多通道 DAQ 系统的密度和吞吐量,输入建立时间应小于或等于 ADC 采集时间,任何额外的延迟都会降低多通道 DAQ 系统的性能;

-

为使输入建立时间最小化,需要提高缓冲器网络的带宽和电容,不过选择元件值时必须小心,避免频域中发生负载效应;

-

选择最合适的精密放大器需要权衡功耗、闭环输出阻抗和 -3 dB 带宽,按照应用的真正需求确定其优先地位。

-

如何提高CYBT-243053-02吞吐量?2024-02-27 0

-

基于随机多址协议的系统吞吐量分析2010-05-06 0

-

网卡吞吐量测试解决方案2013-12-23 0

-

利用NI LabVIEW的并行化技术来提高测试的吞吐量2014-12-12 0

-

优化FPGA利用率和自动测试设备数据吞吐量参考设计2018-10-29 0

-

如何优化多通道数据采集系统?从了解输入建立时间的门道开始2018-10-29 0

-

使用NI USB数据采集和Windows 7提高吞吐量2019-06-06 0

-

浅析敏捷高吞吐量卫星通讯载荷2019-07-23 0

-

如何通过UBFS获得流式ADC数据的最高吞吐量?2019-10-11 0

-

如何衡量多通道DAQ的性能2020-08-13 0

-

提高BLE吞吐量的可行办法2021-01-18 0

-

如何利用NI LabVIEW技术提高测试系统的吞吐量?2021-04-15 0

-

如何提高VLD的吞吐量和执行效率?2021-04-28 0

-

如何通过触发模型提高吞吐量?2021-05-11 0

-

如何显著提高ATE电源吞吐量?2023-11-08 398

全部0条评论

快来发表一下你的评论吧 !