资料下载

×

高速DSP系统详细设计过程和设计中许多挑战的建议详细资料概述

消耗积分:0 |

格式:rar |

大小:3.36 MB |

2018-05-04

本文件包含以下章节:

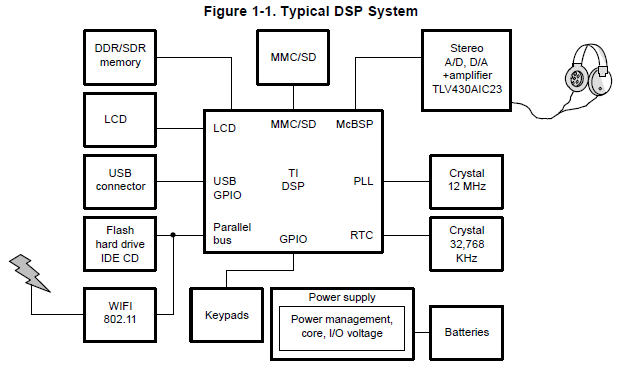

·第1章介绍了高速DSP、音频、视频和通信系统所面临的挑战。

·第2章提供了高速DSP系统中传输线的信息。

·第3章提供了DSP系统中噪声的相关信息。

·第4章介绍了高速DSP电源设计的相关信息。

·第5章提供了关于印刷电路板发展的信息。

·第6章给出了锁相环与内、外噪声隔离的信息。

·第7章提供了高速DSP系统中的电磁干扰信息。

·第8章总结了高速DSP系统的复杂操作。

今天的数字信号处理器(DSP)通常运行在1GHz的内部时钟速率,而发送和接收信号与外部设备的运行速率高于200兆赫。这些快速切换信号产生相当数量的噪声和辐射,这会降低系统性能并产生电磁干扰(EMI)问题,这使得通过联邦通信委员会(FCC)获得认证所需的测试变得困难。良好的高速系统设计要求在动态负载条件下具有低开关噪声的鲁棒电源,高速信号迹线之间的最小串扰,高低频解耦技术,以及具有最小传输线效应的良好信号完整性。本文提供了高速DSP系统设计中许多挑战的建议。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章